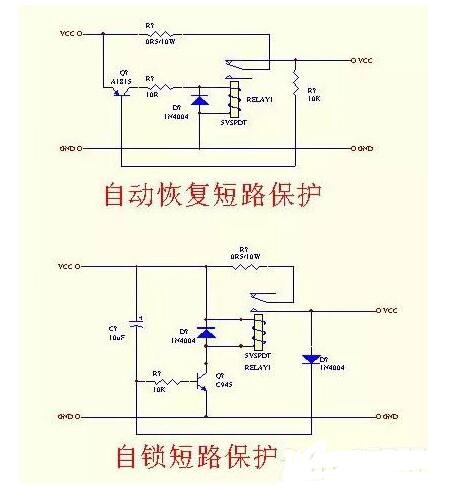

输出短路保护电路图解析

保护电路图

133人已加入

描述

上电:C2 两端电压不能突变,Q2基极电压由VCC开始下降,下降到Q2可以导通(BE结压降取0.7V),这个时间大概是0.12mS。但是同时Q1也在起到阻止 Q2导通的作用,Q1导通的时间大概是:5.87mS也就是说 Q2在5.87mS后才会导通,但是同时C3在阻止Q3的导通,阻止时间是0.17mS。

Q3在上电0。17MS后导通,负载得电,Q3 C极电压达到13.3左右,迫使Q2截至,由此可见Q1可以去掉。

短路时,Q3 C极被拉低,Q2导通,形成自锁,迫使Q3截止,Q3截至后面负载没有电压,这时有没有负载已经没有关系了,所以即使拿掉负载也不会有输出。要想拿掉负载后恢复输出,可以在Q3得 C E结上接一个电阻,取1K左右。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

输出短路保护电路分析2023-07-17 7549

-

LM2596输出短路保护电路图2023-05-30 9528

-

USB接口电路图解析2022-08-25 28628

-

带有短路保护系统的5V直流稳压电源电路图2022-06-27 22645

-

过流短路检测与保护电路图2022-02-09 3483

-

常见的电子元件及电路图解析2021-06-27 8433

-

220V电子镇流器电路图解析2021-04-28 2454

-

锂电池充电电路图如何设计 三节锂电池充电管理芯片电路图解析2020-12-12 28018

-

输出短路保护电路图2019-10-29 22644

-

一个经典输出短路保护电路2016-12-17 3383

-

稳压电源的短路保护电路图2009-06-24 3199

-

5V快速短路保护电路图2009-04-07 6678

-

具有短路保护的低压稳压器电路图2009-04-06 1405

-

低压变压器短路保护电路图2007-12-01 1914

全部0条评论

快来发表一下你的评论吧 !