SONNET中的工艺技术层介绍

EDA/IC设计

描述

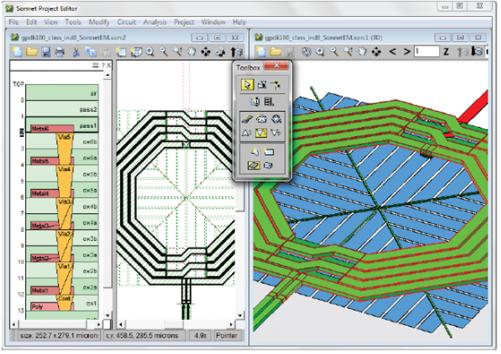

在新版本的帮助下,用户可以对高加工精度的高频电磁模型进行高精度的模型创建,用作用户的EDA设计工作。本次版本中新的特性和功能增强将为用户提供更快,更强大的仿真能力以完成相比以往更大更复杂的线路布局仿真,同时也将有比以往更自动化的设计和仿真流程。

用于一体化设计流程的工艺技术层(Technology Layers)

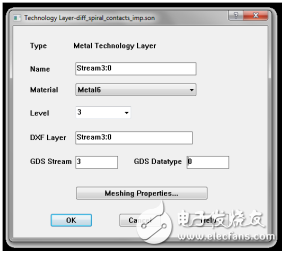

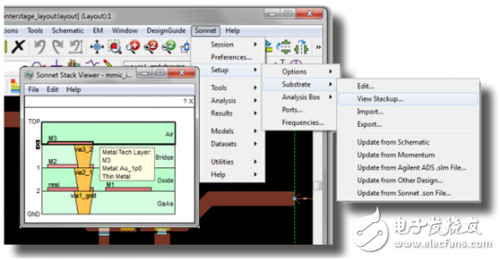

在14版本中,SONNET新引入了一种名为工艺技术层的属性定义层,以实现EDA框架和设计流程的平滑过渡。该工艺技术层实际上是用户创建的EM工程中 的多个属性对象的集合体,其中包括了很多基本属性设置,比如层的命名、物理位置、金属属性、网格控制选项等等。工艺技术层通常可用于定义平面金属,过孔, 和金属块。它们也可以通过GDSII或者DXF导入的方式来进行自动定义,这种导入方式和GDSII的流或者DXF的层的命名是一一对应的,这样的话 SONNET就能保证在导入导出的过程中不会对源文件造成任何更改。SONNET中新引入的这种层的概念让不同RF设计环境下创建的模型能够轻易的进行导 入与导出而无需在SONNET中进行重复的定义。

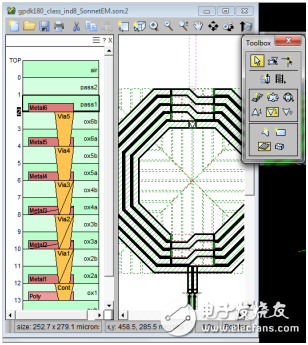

层叠管理器(Stackup Manager)

SONNET14在工程编辑界面中新引入了一种层叠管理器,该管理器能让用户更加直观的进行层的创建和编辑。同时,该管理器也对新引入的工艺技术层提供了 图形接口。在该管理器的帮助下,即使是SONNET的入门用户也能够非常快速的定位当前操作的层以方便他们进行电路结构的创建和修改。另外,当 Cadence Virtuoso和Agilent ADS通过自带的SONNET接口调用SONNET的工程编辑器的时候,该层叠管理器将自动生成。

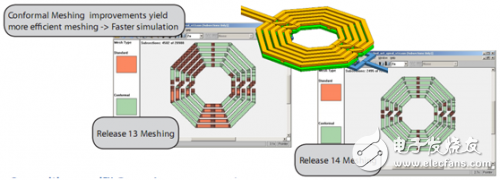

更快的仿真速度

桌面级仿真引擎中,我们已经将CPU并行 运算的核心数由3个提升到了6个,这将使得计算效率得到几乎成倍的提升。而我们的高性能计算引擎对CPU的并行利用核心数则由12个提升到了32个,这也 使得高性能硬件系统的资源利用率得到极大限度的提升。

为了更大限度的增强CPU的并行运算效率,我们对网格剖分引擎也进行了大量优化。在SONNET用于深结硅RFIC电路和连接器的时候,大规模IC过孔阵列和条形过孔结构的网格剖分将会更加高效的助力于整个工程的仿真计算加速。同时,SONNET也对我们的专利技术,共形网格剖分技术进行了改 良,以使其能够更加高效率的完成多层板以及厚金属板材的仿真计算。

自动分组共校准端口

SONNET的共校准端口技术为内部端口的校准提供了前所未有的高精度,这将使大型电路结构由外向内实现无误差的内部联接。在以往的版本中,为了实现校准 端口分组,工程师必须手动在相互之间间距非常小的端口上进行选择和分组的操作。而在14版中,我们新引入了共校准端口自动分组功能,借助该项功能,设计者 能将以往需要手动完成的工作交给求解器进行智能化的端口分组,并且实时而精确。用户只需要将共校准端口分组设置为“Auto”即可。

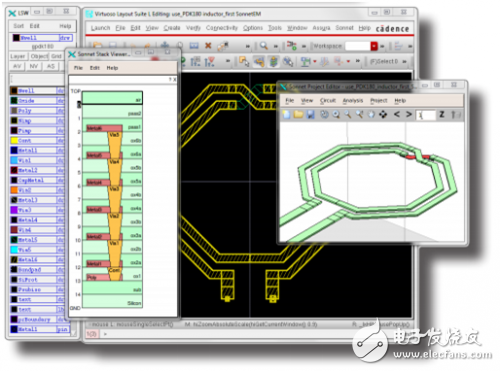

EDA界面架构增强

使用Cadence Virtuoso或者Agilent ADS平台的RF工程师会发现,SONNET的无缝整合化的产品模块已经更加的自动化。有了诸如共校准端口自动分组和层叠管理器等新加入的功 能,SONNET完全能够流程化的进行3D平面电磁模型的处理。SONNET针对Cadence Virtuoso和Agilent ADS的EDA接口现在包括以下内容增加:

l Cadence和Agilent中创建的层能够自动生成为SONNET中的工艺技术层。

l EDA框架中直观的工艺技术层叠视图。

l 在EDA框架中直接进行SONNET的DC连续性检测。

l 共校准端口的自动分组功能可自动应用于内部端口。

l 保存/载入状态移动至Virtuoso网格单元视图。

l 在处理微型过孔阵列时,对精简之后的多边形过孔进行联接与合并的选项,该选项能更进一步的降低网格剖分的资源需求。

l 过孔阵列合并操作,针对无接地面,介质层接触过孔的情况。

Linux和VM虚拟机环境下的GUI性能增强

为了满足不断增长的Linux及虚拟机软件平台下对SONNET的运行需求。14版的SONNET对各种接口进行了优化,以使得远程主机和虚拟主机能有更加迅速的响应—这在企业级的软件安装中也显得越来越重要。

来源;互联网

-

SOI工艺技术介绍2025-10-21 2549

-

芯片制造中的浅沟道隔离工艺技术2025-03-03 4389

-

电子工艺技术论文-反射层对倒装LED芯片性能的影响2021-12-08 962

-

半导体工艺技术的发展趋势是什么?2019-08-20 4575

-

半导体工艺技术的发展趋势2019-07-05 4632

-

曝光成像与显影工艺技术的原理及特点2019-04-28 36982

-

COMS工艺制程技术与集成电路设计指南2019-03-15 6551

-

EMC设计、工艺技术基本要点和问题处理流程2015-08-25 5052

-

晶圆凸起封装工艺技术简介2011-12-01 5419

-

常用PCB工艺技术参数2010-07-15 755

-

超细线蚀刻工艺技术介绍2010-03-30 2130

-

创建灵敏的MEMS结构的工艺技术介绍2010-03-11 994

-

什么是CPU的生产工艺技术/向下兼容?2010-02-04 1005

-

Sic mesfet工艺技术研究与器件研究2009-10-06 6770

全部0条评论

快来发表一下你的评论吧 !