关于FPGA它的整体结构是怎样的

可编程逻辑

1395人已加入

描述

(文章来源:OFweek电子工程网)

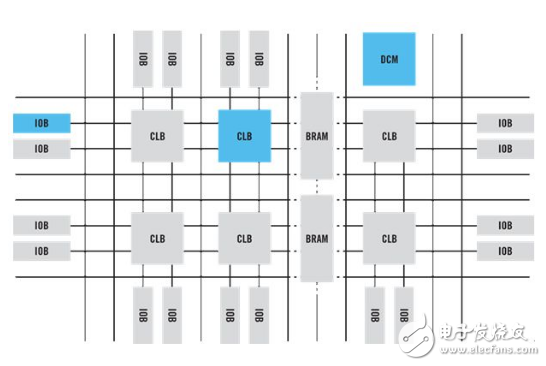

FPGA架构主要包括可配置逻辑块CLB(Configurable Logic Block)、输入输出块IOB(Input Output Block)、内部连线(Interconnect)和其它内嵌单元四个部分。

CLB是FPGA的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个CLB都包含一个由4或6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

FPGA可支持许多种I/O标准,因而可以为系统设计提供理想的接口桥接。FPGA 内的I/O按bank分组,每个bank能独立支持不同的I/O标准。目前最先进的FPGA提供了十多个I/O bank,能够提供灵活的I/O支持。

CLB 提供了逻辑性能,灵活的互连布线则负责在CLB和I/O之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低skew布线(全局性专用布线资源)。一般,各厂家设计软件会将互连布线任务隐藏起来,用户根本看不到,从而大幅降低了设计复杂性。

内嵌硬核单元包括RAM、DSP、DCM(数字时钟管理模块)及其它特定接口硬核等。一般来说,器件型号数字越大,表示器件能提供的逻辑资源规模越大。在FPGA器件选型时,用户需要对照此表格,根据业务对逻辑资源(CLB)、内部BlockRAM、接口(高速Serdes对数)、数字信号处理(DSP硬核数)以及今后扩展等多方面的需求,综合考虑项目最合适的逻辑器件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

关于FPGA通信协议的问题2014-12-06 4088

-

FPGA入门:内里本质探索——器件结构2015-01-27 5156

-

TVM整体结构,TVM代码的基本构成2021-01-07 3860

-

FPGA芯片整体架构2021-07-29 1713

-

XILINX FPGA 芯片整体架构是如何构成的2021-10-29 3477

-

STM32CubeIDE整体开发的流程是怎样的2021-11-25 1393

-

匿名飞控源码整体的逻辑顺序是怎样的2022-01-20 1824

-

PCB板的整体布局与印刷结构2009-09-30 525

-

FPGA整体视频介绍2010-11-18 1211

-

FPGA视频教程之怎样开始一个简单的FPGA设计2019-03-20 1258

-

关于FPGA芯片的结构组成是如何的2019-09-06 4006

-

关于FPGA它的开发流程是怎样的2019-11-06 2965

-

FPGA的基本组成结构2020-06-01 13224

-

关于直线电机的浅析,它的结构和工作原理是怎样的2020-09-11 7836

-

FPGA中关于SPI的使用2023-04-12 1685

全部0条评论

快来发表一下你的评论吧 !