交流耦合电容介绍

电容器

描述

从电路来说,总是存在驱动的源和被驱动的负载。如果负载电容比较大,驱动电路要把电容充电、放电,才能完成信号的跳变,在上升沿比较陡峭的时候,电流比较大,这样驱动的电流就会吸收很大的电源电流,由于电路中的电感,电阻(特别是芯片管脚上的电感,会产生反弹),这种电流相对于正常情况来说实际上就是一种噪声,会影响前级的正常工作。这就是耦合。

去藕电容就是起到一个电池的作用,满足驱动电路电流的变化,避免相互间的耦合干扰。

旁路电容实际也是去藕合的,只是旁路电容一般是指高频旁路,也就是给高频的开关噪声提高一条低阻抗泄防途径。高频旁路电容一般比较小,根据谐振频率一般是0.1u,0.01u等,而去耦合电容一般比较大,是10u或者更大,依据电路中分布参数,以及驱动电流的变化大小来确定。

旁路是把输入信号中的干扰作为滤除对象,而去耦是把输出信号的干扰作为滤除对象,防止干扰信号返回电源。这应该是他们的本质区别。

交流耦合电容

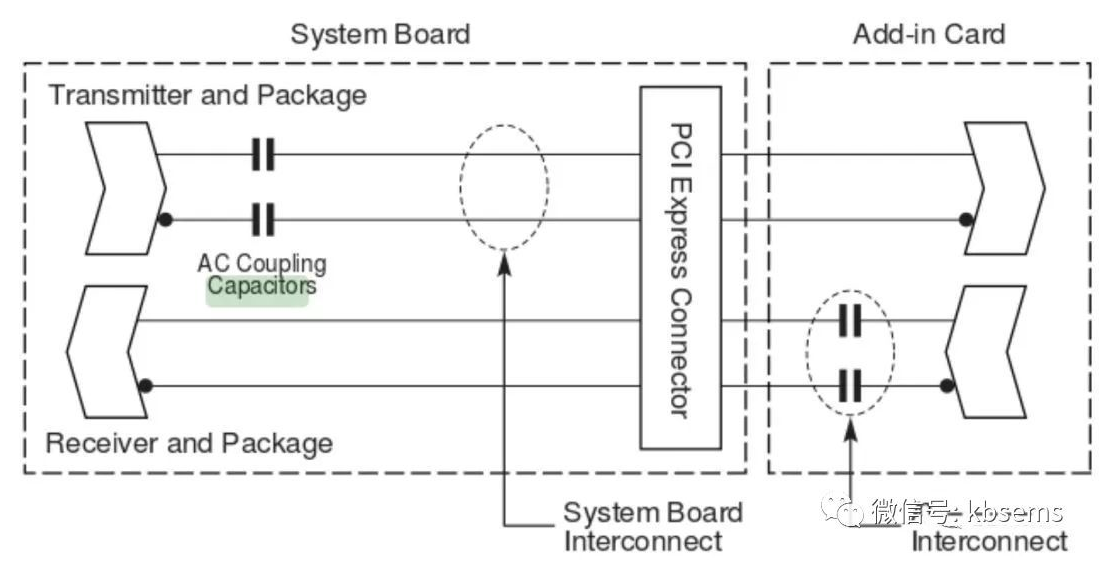

我们在处理高速差分信号的时候,经常使用交流耦合,也会使用直流耦合, 比如PCI Express我们看到的是交流耦合, 早期光模块和芯片之间的LVPECL则更多地使用直流耦合, 这篇文章我们不打算讨论什么情况下使用交流耦合,什么情况下使用直流耦合,我们要讨论的是使用交流耦合时需要解决的问题。

很简单的一个问题, 交流耦合的电容需要选择多大?我们最常见的有0.1uF和0.01uF, 可是我们有想过为什么吗?为什么不选更大或者更小的?今天我们试图来用最简单的方式来解释,我们先使用频域的方式。

频域

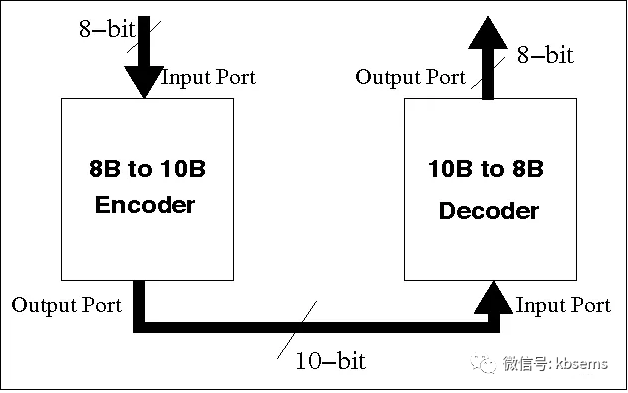

以PCIE为例, 我们知道PCIE内含8b/10b编码,并且我们知道它的所谓2.5Gbps (PCIE1.0), 5Gbps (PCIE2.0),8Gbps (PCIE3.0)速率指的包含了8b/10b后的速率,也就波特率,这一点和以太网不一样,千兆以太网的SGMII接口速率其实1.25Gbps,去除8b/10b后比特率是1000M,所以这里的千兆指的payload速率,而且PCIE的速率指的是加上开销以后的速率。

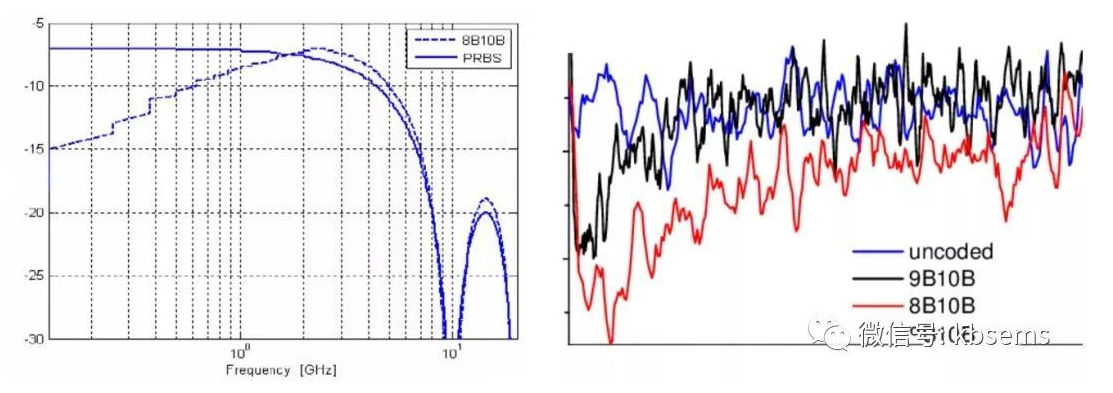

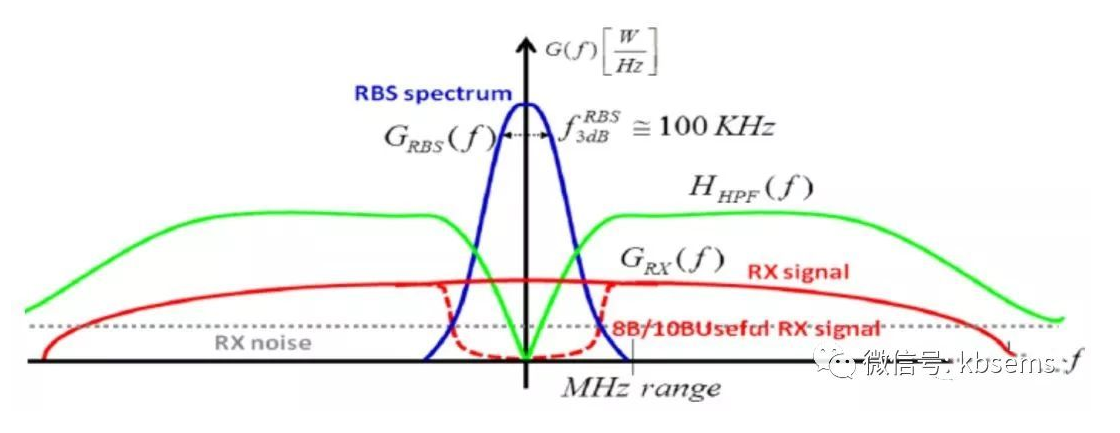

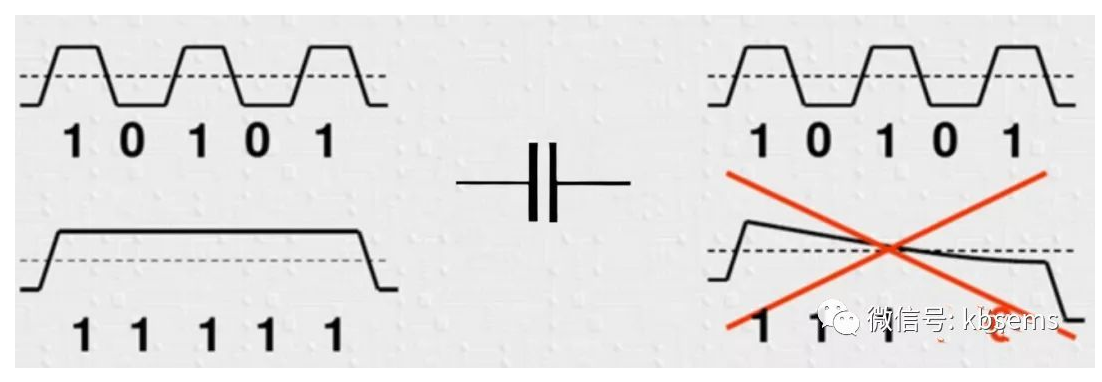

题外话不多说, 我们知道8b/10b作用是确保0和1的平衡,使得信号不会出现很长0和很长的1,防止接收端的CDR失锁,也就是去除了信号的低频部分,使得信号的频谱保持在某个频率以上。如图所示经过8b/10b编码后信号的频谱在低频段衰减了8dB。

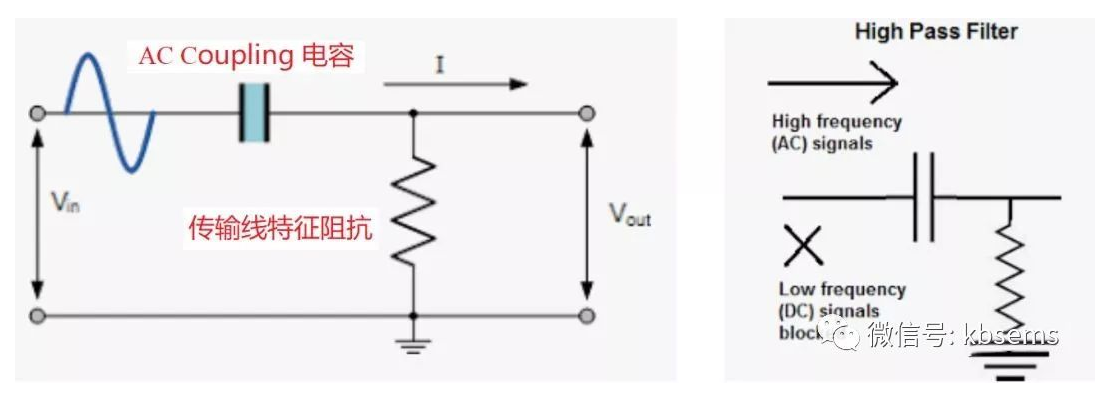

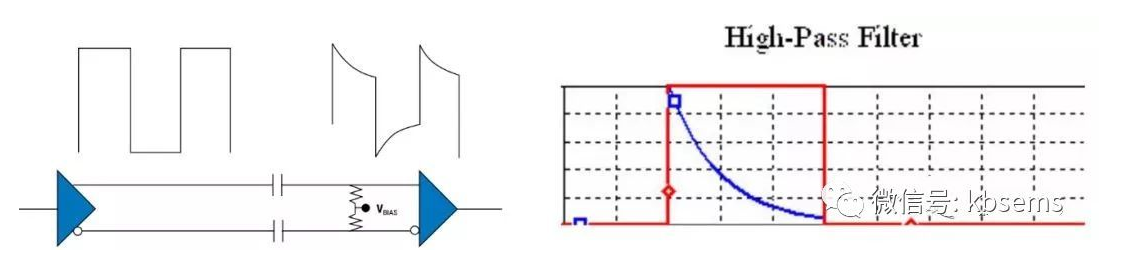

那么我们怎么去除?为什么我们要去除低频,保留高频呢?这还得从AC耦合的结构原理说起:

根据上图,我们进一步细化一下模型如下:

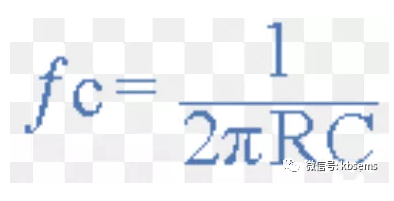

我们看到耦合电容和传输线的特征阻抗组成了一个高通的滤波器, 如下面的图所示我们需要确保此High pass filter的截止频率(绿色线)要低于信号经过8b/10b后的频谱的最低点(红色线),因为只有这样才能确保信号的能量完整的通过。

下面我们来计算一下:

1. 传输线特征阻抗Zr=50;

2. AC coupling电容值为C;

3. PCIE信号经过8b/10b后的信号频谱也是已知的,用频谱仪测一下或者简单用速率(比如PCIE2.0的5Gbps)除以4简单估算一下, 因为8b/10b最长0或者1只有4位了;

下面我们就来计算电容的值:

我们很容易就能得出C的值了,简单吧。

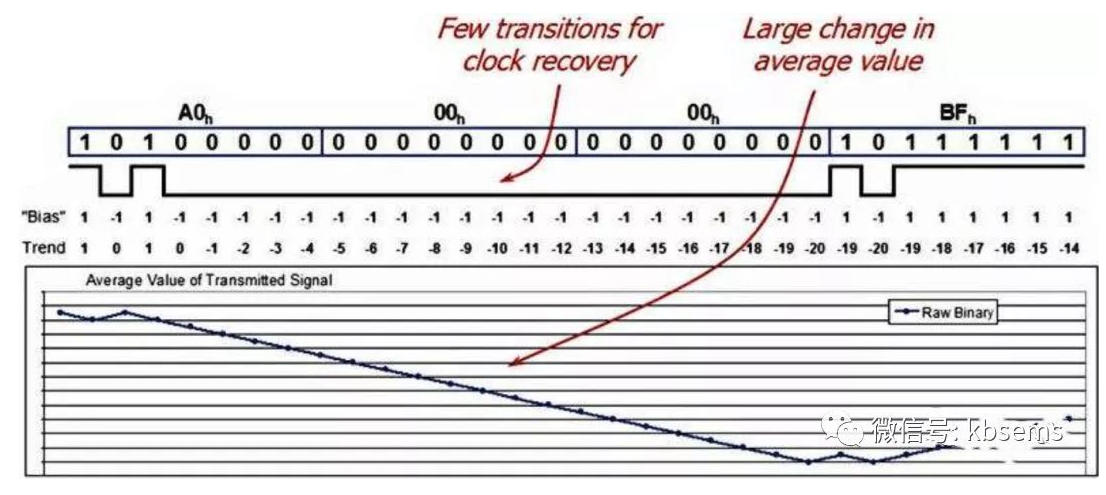

时域

从时域来解释, 如果不用8b/10b的话,问题有两个,请看下面这段英文的精妙论述:AC coupled data signals would have DC drifts depending on the data content. A long sequence of 1´s will lead into positive drift and many 0´s will drift toward negative voltage. 意思是说如果没有8b/10b的话,信号的长0和长1会使得信号本身发生直流漂移。

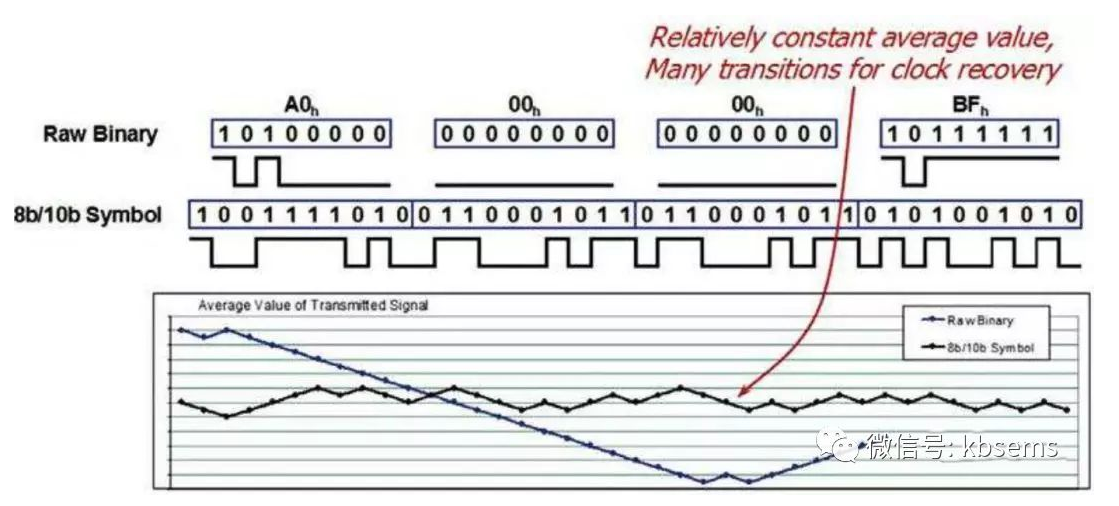

而加了8b/10b以后, CDR和恢复和信号直流漂移问题解决,下面这张图我们再来看, 所谓的“constant average value”已经趋于水平而不会上下摇摆。

我们继续阐述8b/10b在时域的作用,信号经过了ac coupling电容之后,相当于经过了一个高通的滤波器,会产生的问题如下,高频跳变的能量可以顺利通过, 而低频的长0和长1则不能通过, 低频信号发生了畸变,而经过了8b/10b后,信号的低频部分被消除,也不会有畸变的事情发生了。

那么是不是说加了8b/10b后,使用ac coupling就什么问题都没有了呢? 不是, 我们需要仔细考虑计算我们的ac coupling电容的大小。我们先来看看经过high pass后时域信号发生的变化:

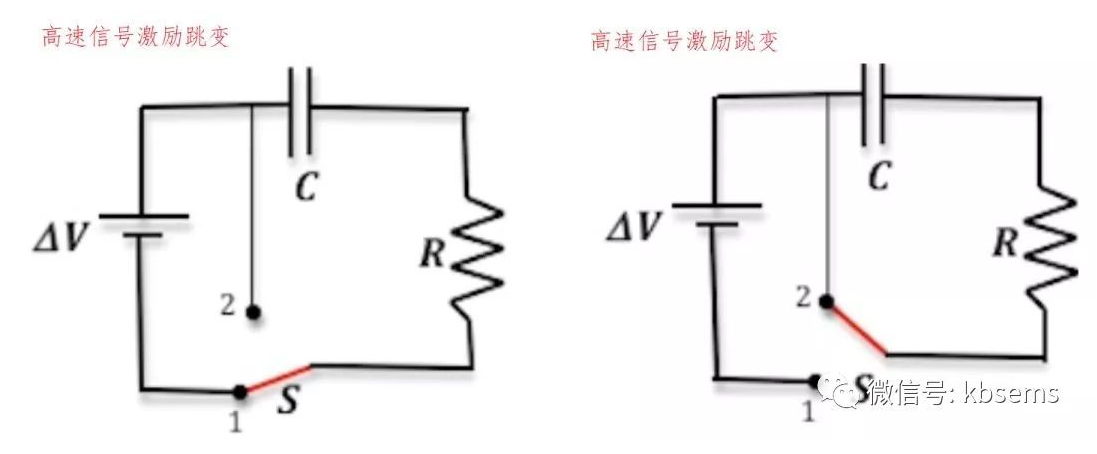

我们看到仍然有部分低频部分被去除,这可能是由于电容选择不合理,我们先来看看电容取值如果太小会怎么样?

电容如果取值太小,高速信号在充放电的时候,很显然容易饱和,我们知道电容一旦饱和,阻抗就会变得很大,抵抗外面的高速信号的变化,为什么小电容容易饱和呢? 我们想象一下, 电容的正负极板其实是随着信号跳变也在不停地做充放电,这样极板两边的极性才会随着信号的高低而变化,如果是小电容再加上长0长1的低频部分到来,一下就充满了。一旦充满,最终导致信号的有效低频部分被去除,如下如所示,连续三个1就会导致电容饱和,我们仔细看一下变化的步骤:

1) 开关打到1;

2) 电容阻抗无穷小,电阻分压最大;

3) 随着电容充电,电容的阻抗在变大,如果饱和了,阻抗就变得无穷大,阻碍外部的交流变化,而且电阻上的分压变得很小,导致直流漂移;

4) 开关打到2;

5) 电容开始放电,如此周而复始。

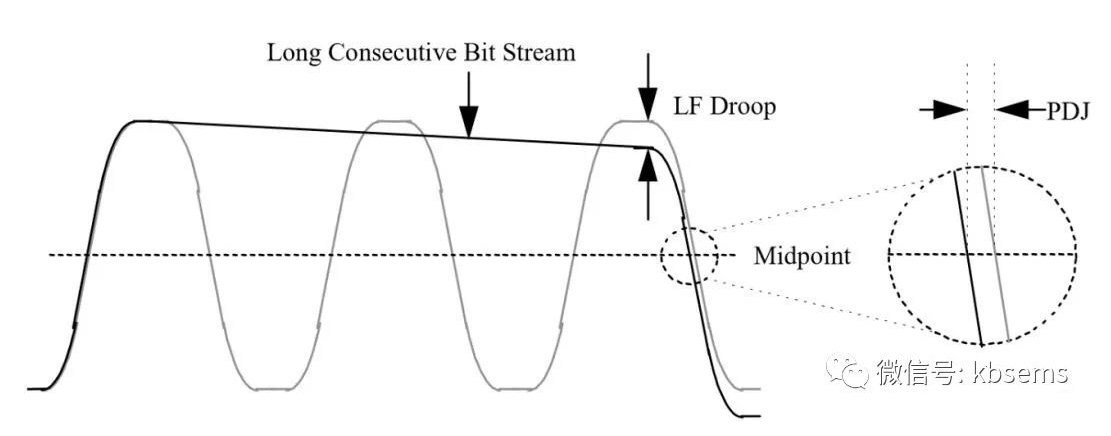

我们可以看到直流电平缓慢下降的直流漂移会带来什么, 会带来抖动,这种特殊的抖动叫PDJ。

我们看到出现1110的数据时,就会在1到0转变的边沿偏离,产生抖动,产生的原因很简单,就是因为直流电平的起点低了,导致下降沿比正常的周期跳变信号提前了, 这种抖动是我们不喜欢的,一方面信号变形,另外一方面CDR需要跟踪并且修复这种抖动, 是的眼图质量裂化,误码率升高。

那么电容选太大会怎么样? 当然很容易想明白,不能选太大的电容,因为大电容含有ESL/ESR,也会对信号有衰减。

所以从时域和频域的两个角度,我们知道高速信号的ac coupling的电容选择需要仔细计算和考量, 不能随意。

-

直流耦合与交流耦合的区别和用途2024-08-09 9388

-

示波器交流耦合时的电容有多大?2024-02-25 7778

-

运放的多级交流放大电路如何选用电容耦合?2024-02-03 4102

-

电路的交流耦合分析,电容一般选择多大容量?2024-01-21 3302

-

AD9467芯片的时钟输入的端接100欧电阻是放在交流耦合电容前还是交流放耦合电容之后?2023-12-04 582

-

耦合电容计算公式_耦合电容对音质的影响2023-02-25 17995

-

使用电容实现LVDS连接交流耦合有什么优势?2021-04-08 1832

-

耦合电容是什么,它的作用是什么2021-03-31 33605

-

耦合电容是什么意思2019-10-16 53328

-

电容耦合电路的特点2019-06-06 13139

-

电容耦合是什么意思2019-01-04 40855

-

耦合电容是什么?详细解析耦合电容的原理,耦合电容的应用和耦合电容电路2017-05-06 48954

-

AC Coupling---交流耦合,旁路电容2012-11-04 5438

-

交流耦合的优点2009-05-02 6193

全部0条评论

快来发表一下你的评论吧 !