浅析静态功耗和静态时序分析

嵌入式技术

1412人已加入

描述

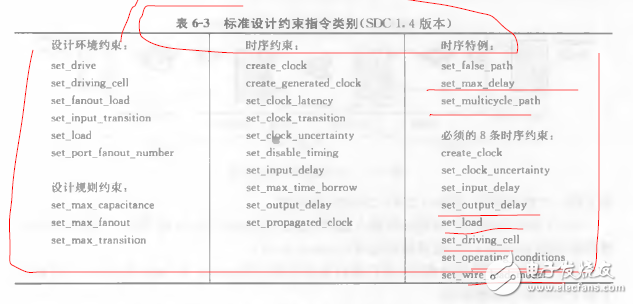

静态时序分析

STA贯穿设计过程的各个阶段,从RTL逻辑综合到布局、时钟树综合、布线和反标,直到tape_out。每一次分析的目的都是为了检查当前设计的结果是否满足设计的约束条件。

在做时序分析时,总延迟的期间延迟部分由时序库提供,互连线延迟部分在每一阶段是不一样的。前者在设计中随后者的变化而变化。即随着RC对器件负载和信号转换在不断的更新和变化。

功耗分析

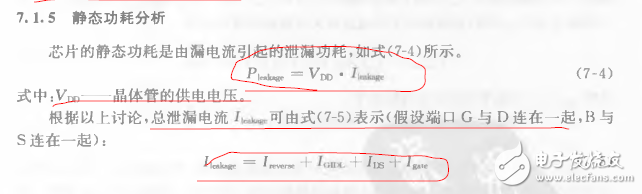

静态功耗分析

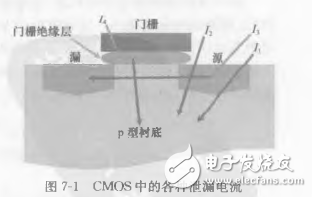

静态功耗又称泄漏功耗,它是指电路处于等待或不激活状态时泄露电流所产生的功耗。泄露电流主要有4种:

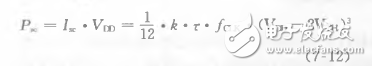

动态功耗

指芯片工作中,晶体管处于跳变状态所产生的功耗,主要由动态开关电流引起的动态开关功耗以及短路电流产生的短路功耗两部分组成。

开关功耗

短路功耗

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何测试TPA3118和TPA3116的静态电流和静态功耗?2024-10-12 919

-

浅析CMOS电路的静态功耗和动态功耗2024-04-01 9716

-

动态电路和静态电路的区别2023-09-17 6702

-

静态时序分析的相关概念2023-07-04 2034

-

解读FPGA的静态时序分析2023-03-14 1465

-

时序分析的静态分析基础教程2021-01-14 1074

-

华为FPGA硬件的静态时序分析与逻辑设计2020-12-21 1549

-

静态时序的分析原理及详细过程2020-11-25 11213

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2722

-

静态时序分析基础及应用2016-05-09 858

-

课题三_基本共射极放大电路的组成和静态分析(2学时)2015-11-13 894

-

静态时序分析在IC设计中的应用2011-12-20 1244

-

静态时序分析与逻辑(华为内部培训资料)2010-07-09 1018

-

[求助]静态时序分析与时序仿真?2010-03-03 4949

全部0条评论

快来发表一下你的评论吧 !