DDR3 SDRAM的IP核调取流程

可编程逻辑

描述

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核的调取和使用是非常必要的。下面我们以A7的DDR3 IP核作为例子进行IP核调取。

DDR3是IP软核,什么是软核呢?软核就是使用查找表,寄存器搭建出来的IP核。需要占用FPGA的逻辑。

一、DDR3 SDRAM IP核建立流程

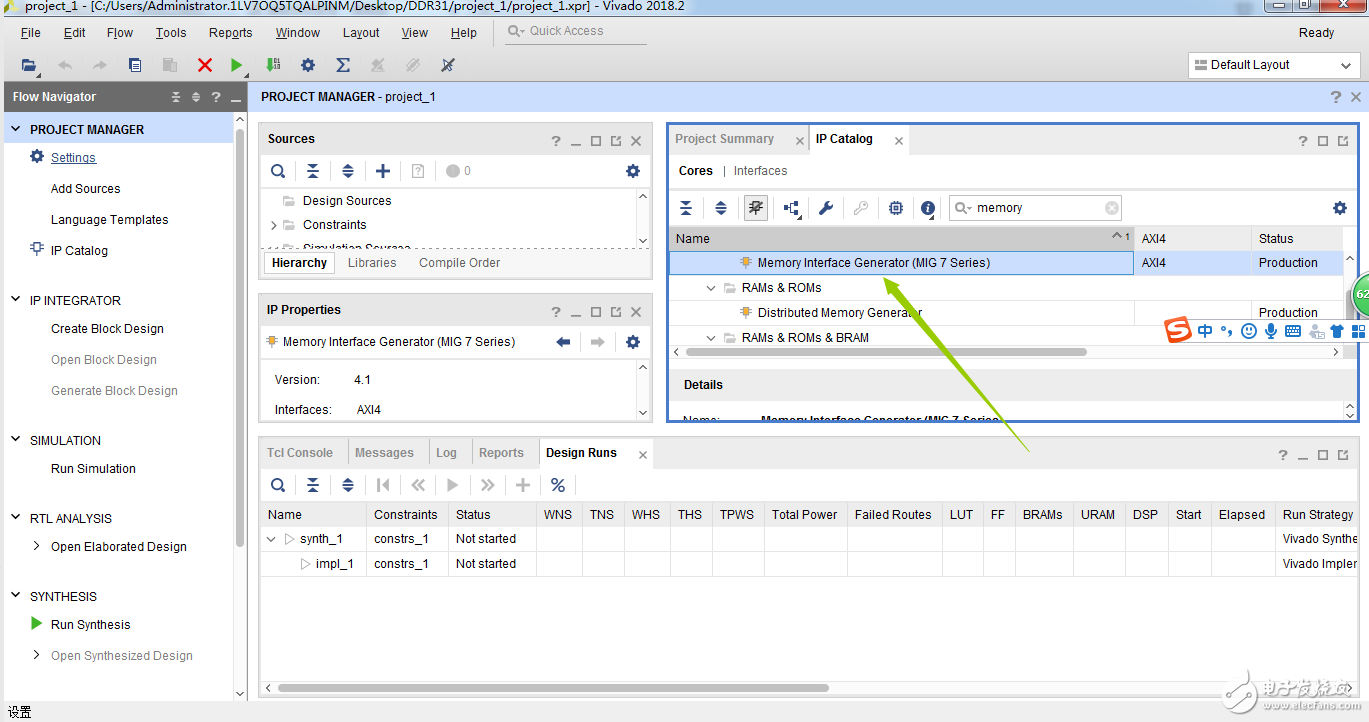

1、在工程建好之后,可以点即IP Catalog来建立相应的IP,具体界面如图所示。

在搜索区搜索memory,然后找到如下图所示的选项,双击。

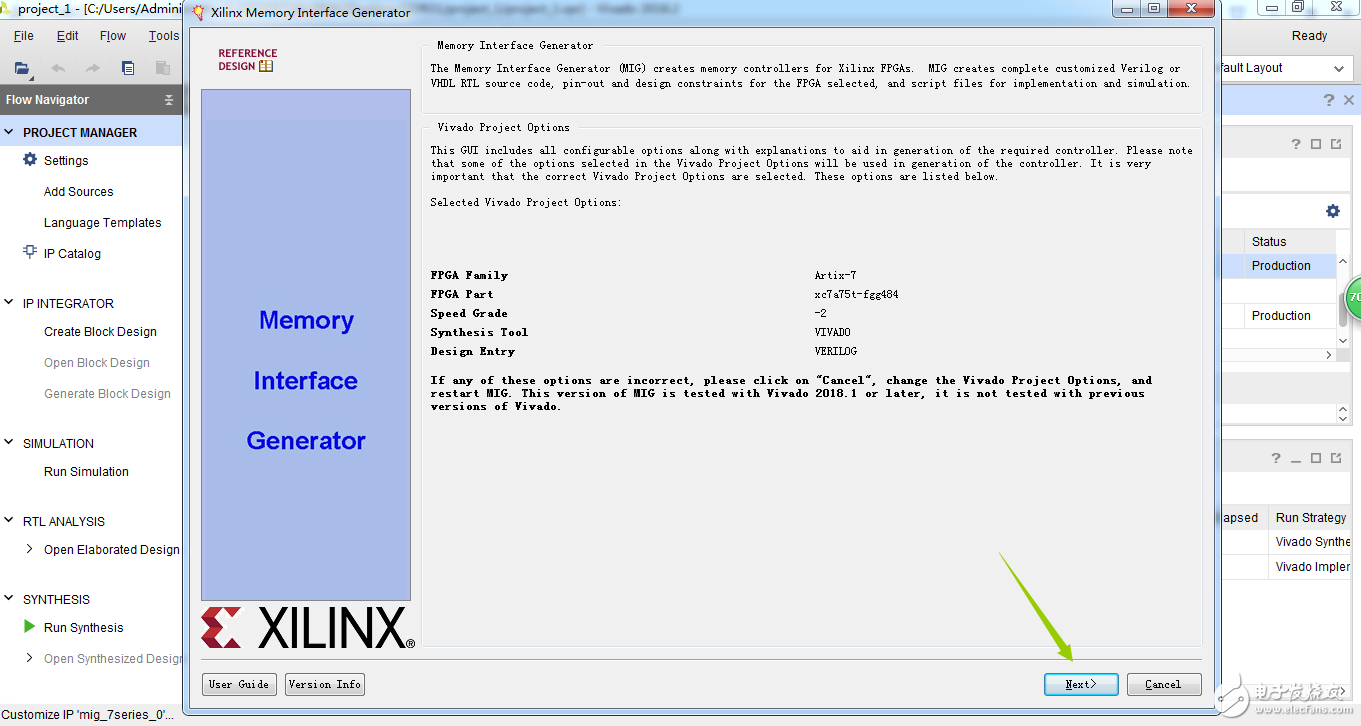

2、点击next

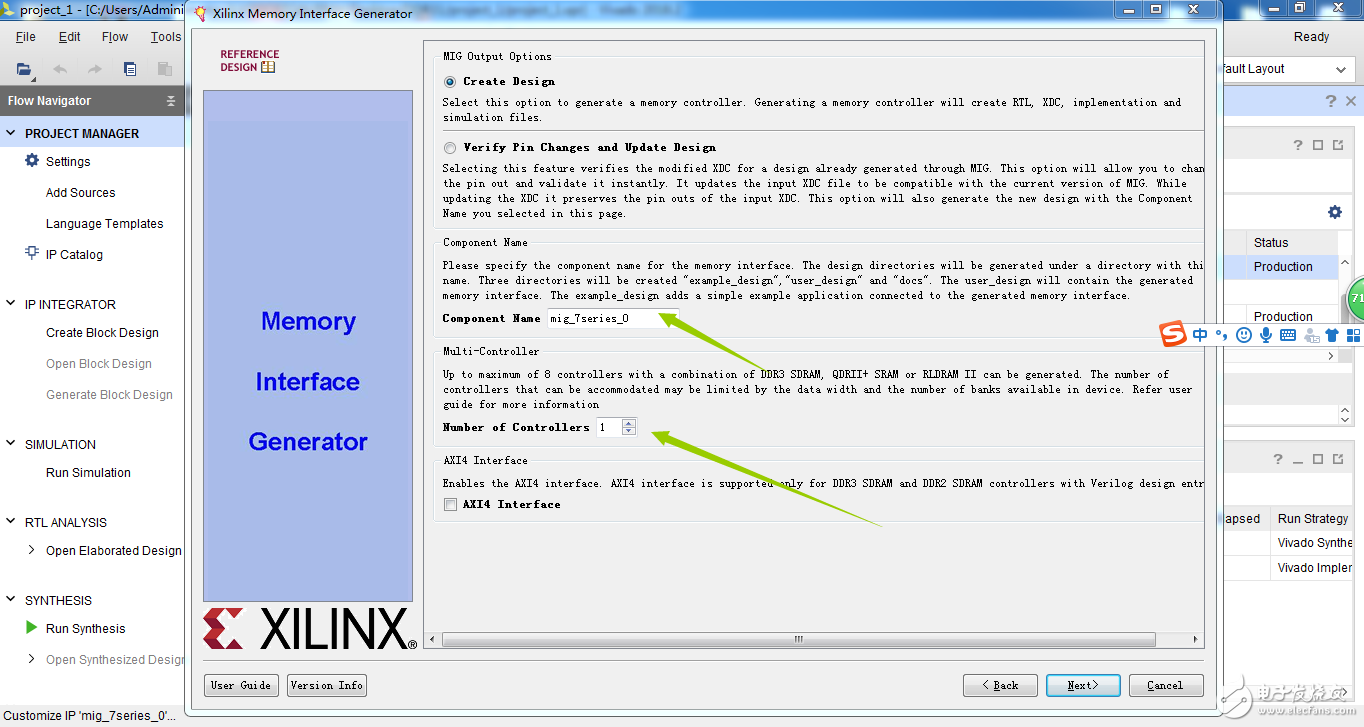

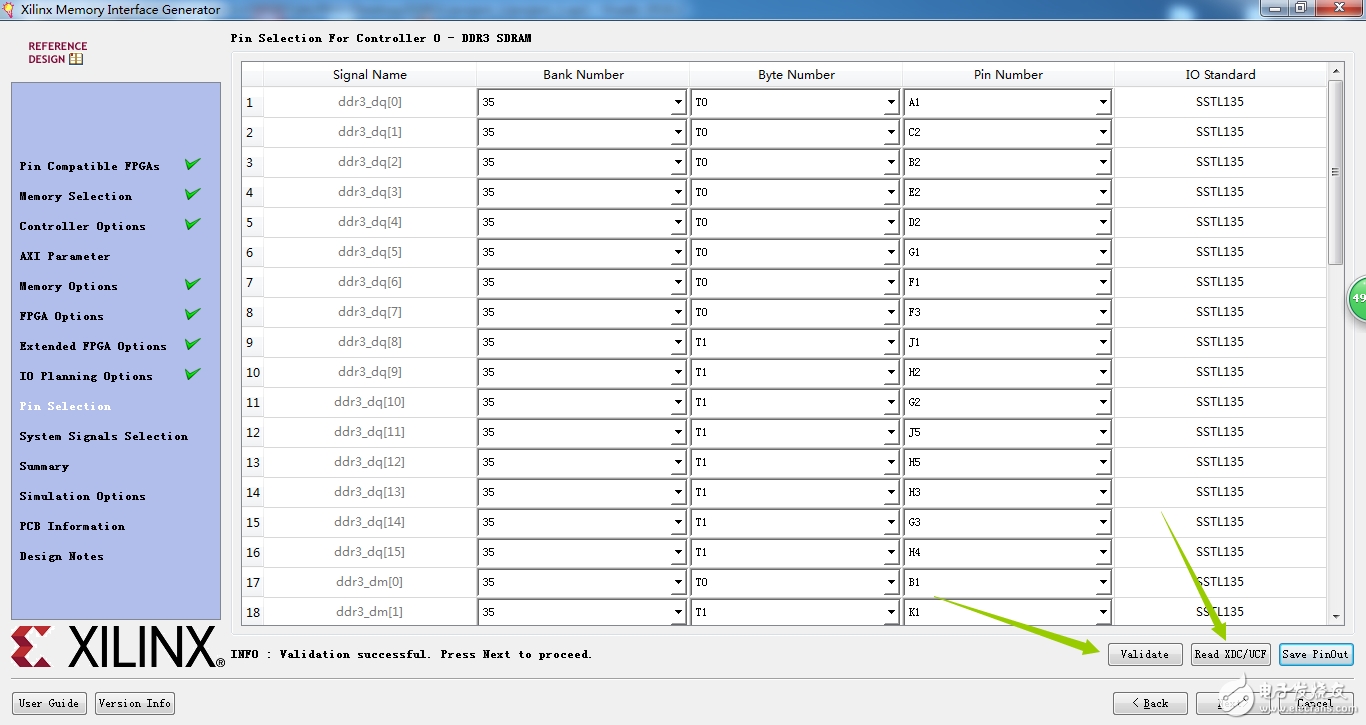

3、定义器件名,选择控制器个数。控制器个数我们选择1个,点击next。

注:AXI4 Interface,就选择的是AXI格式的MIG核,不勾是传统的接口信号格式。

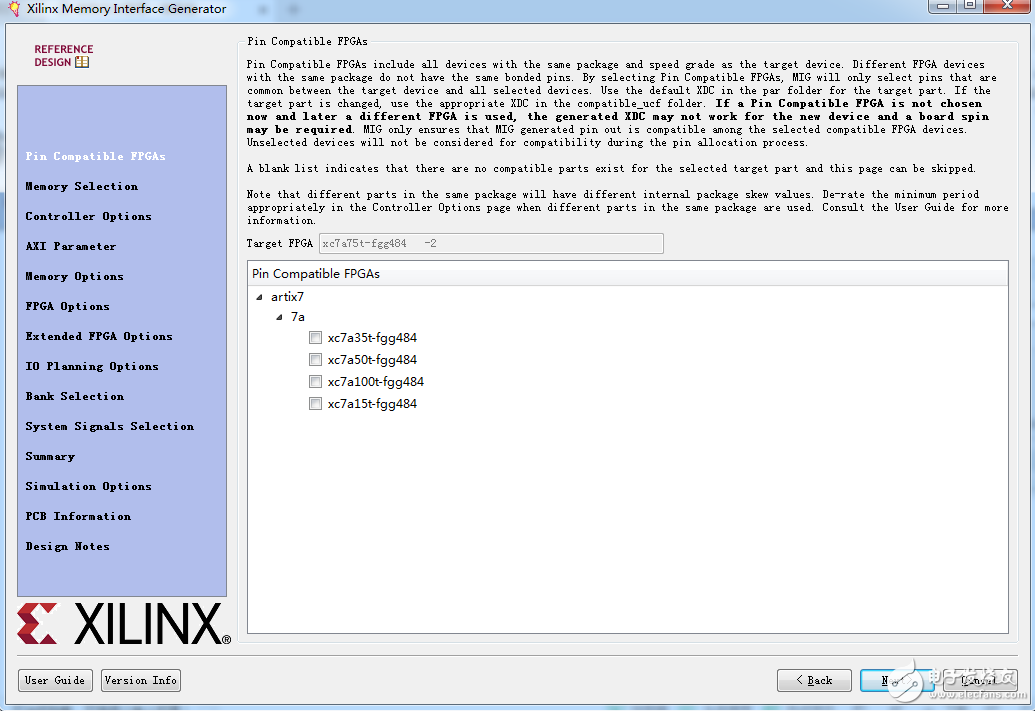

4、进入到如图所示的界面,如果使用的芯片相同,则可以选择,若没有,可以不选,继续点击next。

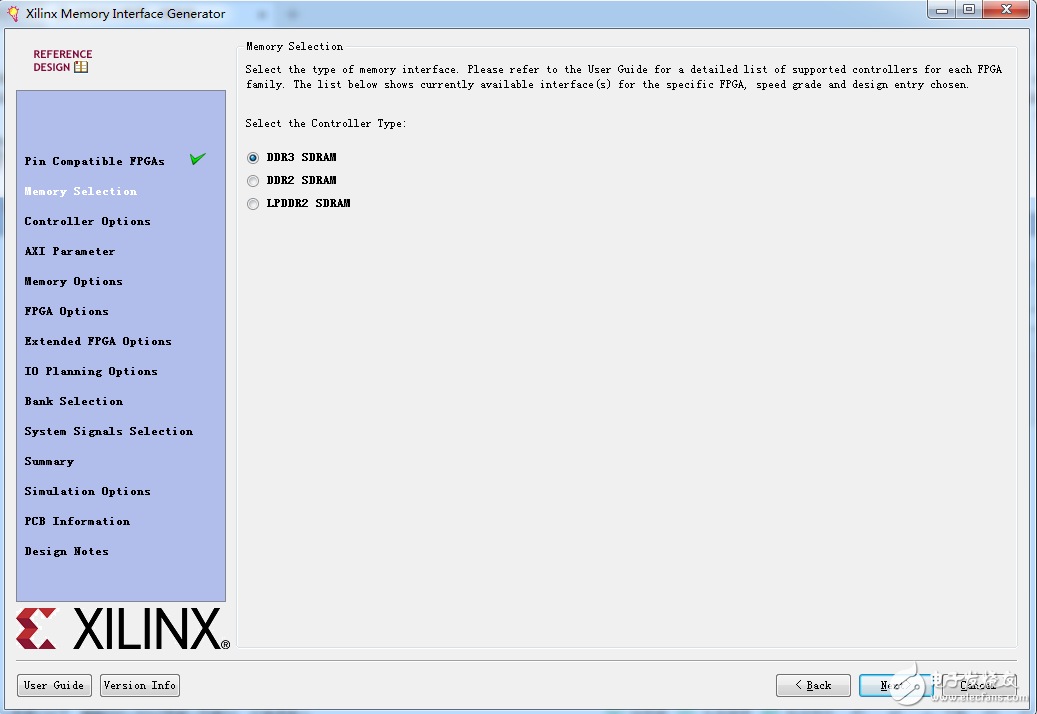

5、进入到选取控制器类型的界面,由此我们选择DDR3,点击next。

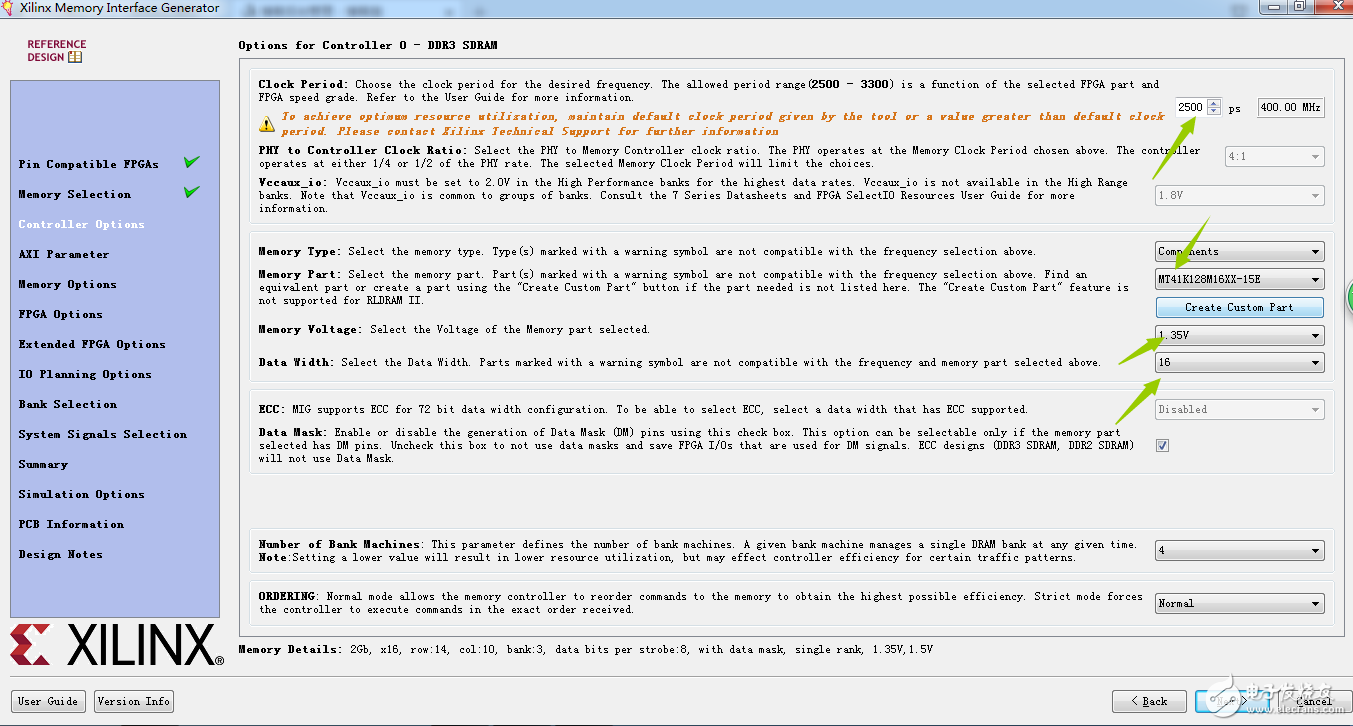

6、进入到DDR3 SDRAM相应参数的界面,我们首先选择的是DDR3的工作频率设置为400MHZ。因为开发板上的供电电压为1.35V,所以我们在此处设置为1.35V。设置DDR3的总线位宽是16位的。

位宽的计算:400*2*16=12.8Gbps带宽

400是控制器PHY的时钟,2是DDR双沿采样,16是16bit位宽,半双工,所以考虑读写的情况,平均分配的话每个操作占有6.4Gbps的理论带宽。

(1)Clock period:通过周期调整DDR3工作时钟。

(2)4:1和2:1部分,是选择用户的工作时钟。

4:1表示DDR3工作时钟400M情况下用户时钟为100M。

2:1表示DDR3工作时钟400M的情况下用户时钟为200M。

(3)memory part的意思是选择DDR3器件的型号。

(4)Number of Bank Machines:意思是bank的数量。

(5)Data mask:代表的是数据淹模

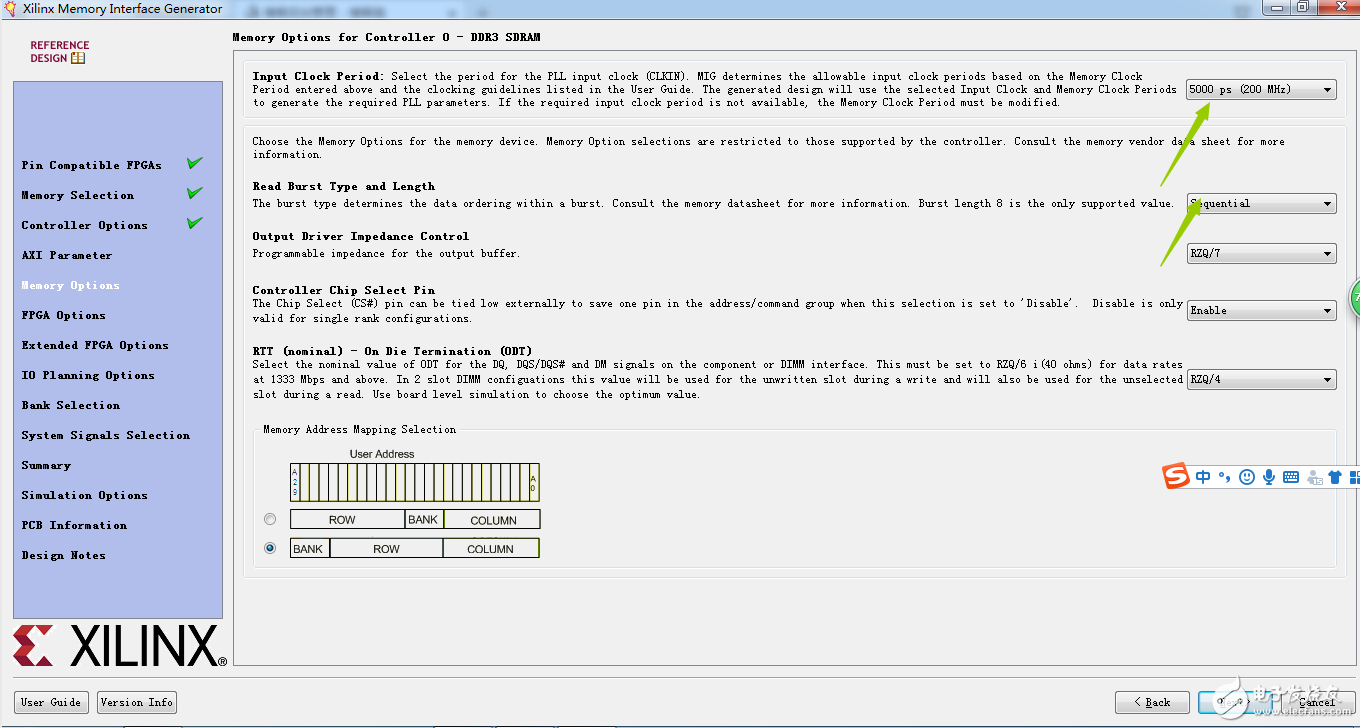

7、输入IP核的时钟设置为200Mhz,我们将200Mhz通过PLL倍频产生400MHZ的时钟,然后给PHY芯片。

(1)input clock period:IP核的工作时钟,常用时钟50M、200M必须直接连板子。

(2)read burst type and length 表示:数据顺序。

(3)memory address mapping selection表示:地址类型。

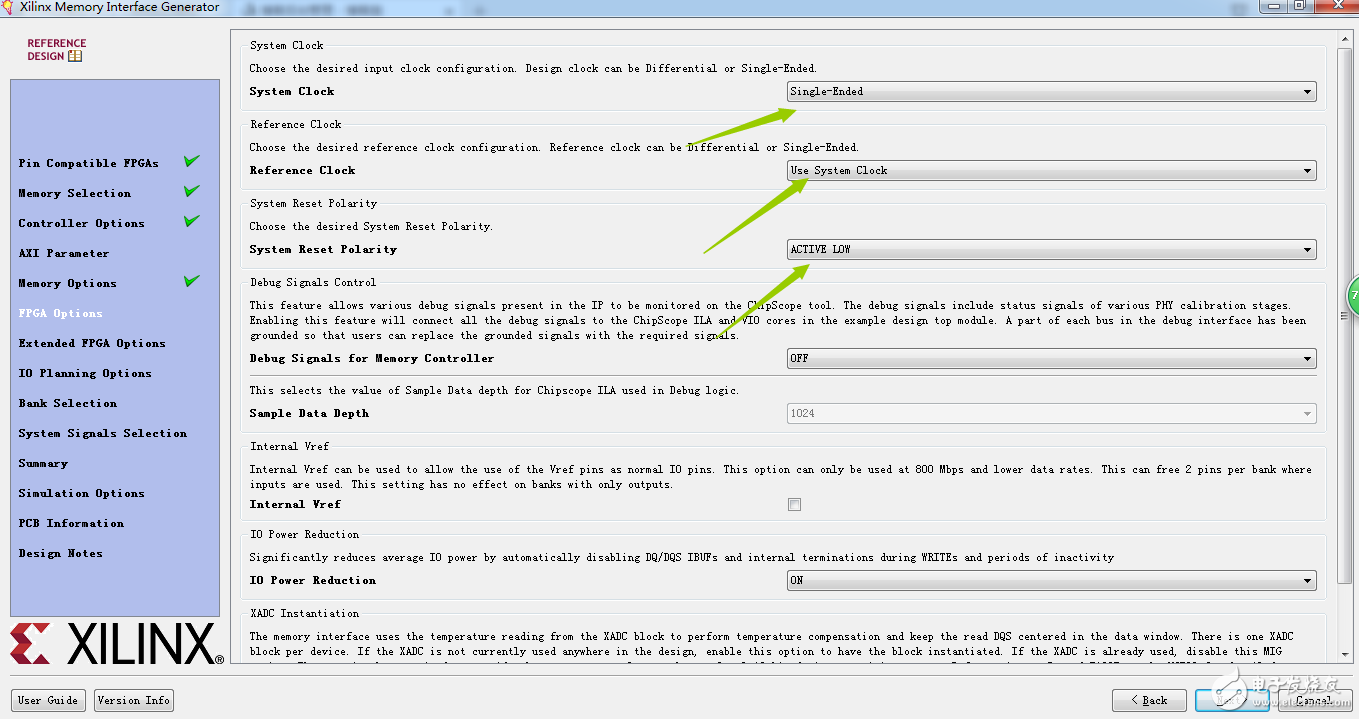

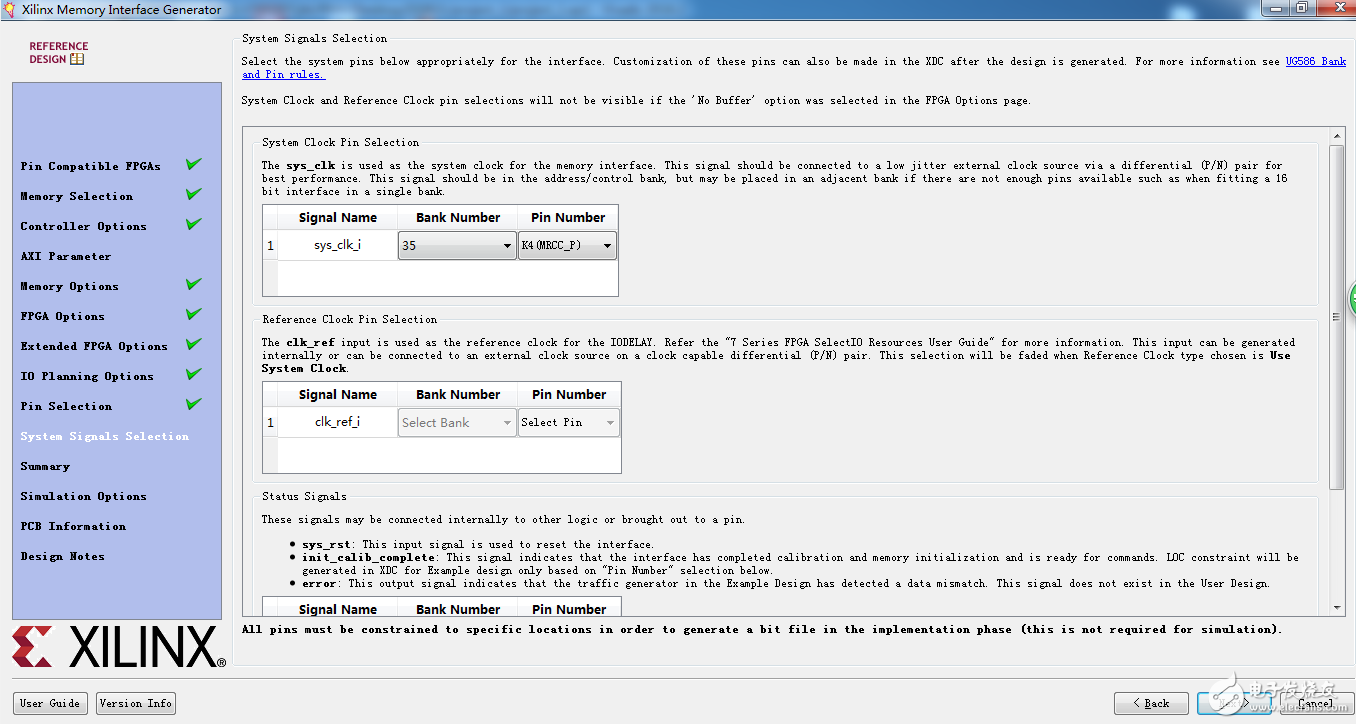

8、设置控制系统时钟和参考时钟

系统时钟有single_ended、deferential和no buffer三种,single_ended为来源于引脚的单端时钟,diferential为差分时钟,no buffer为来源于FPGA内部的时钟。参考时钟有4种,其中三种也为single_ended、deferential和no buffer,另外一种为use system clock,注意:只有在system clock时钟频率为199Mhz~201Mhz时,参考时钟才能存在use system clock选项。

注1:如果选择参考时钟,如果选择200Mhz系统时钟,可以不选参考时钟直接使用系统时钟作为参考时钟。

注2:system reset polarity意思是选择复位高低有效。

9、点击next,勾选第二项,再次可以直接导入DDR3 SDRAM的引脚信息,前提是引脚约束文件已经存在,引脚约束文件可以是ucf和xdc类型。然后点击如下两个图标找到ucf/xdc的路径,选择对应的约束文件,点击打开,之后点击validate来确认约束文件有效。

10、默认点击next,剩余的直接点击next就可以了。最后gengerate生成DDR3 IP核。

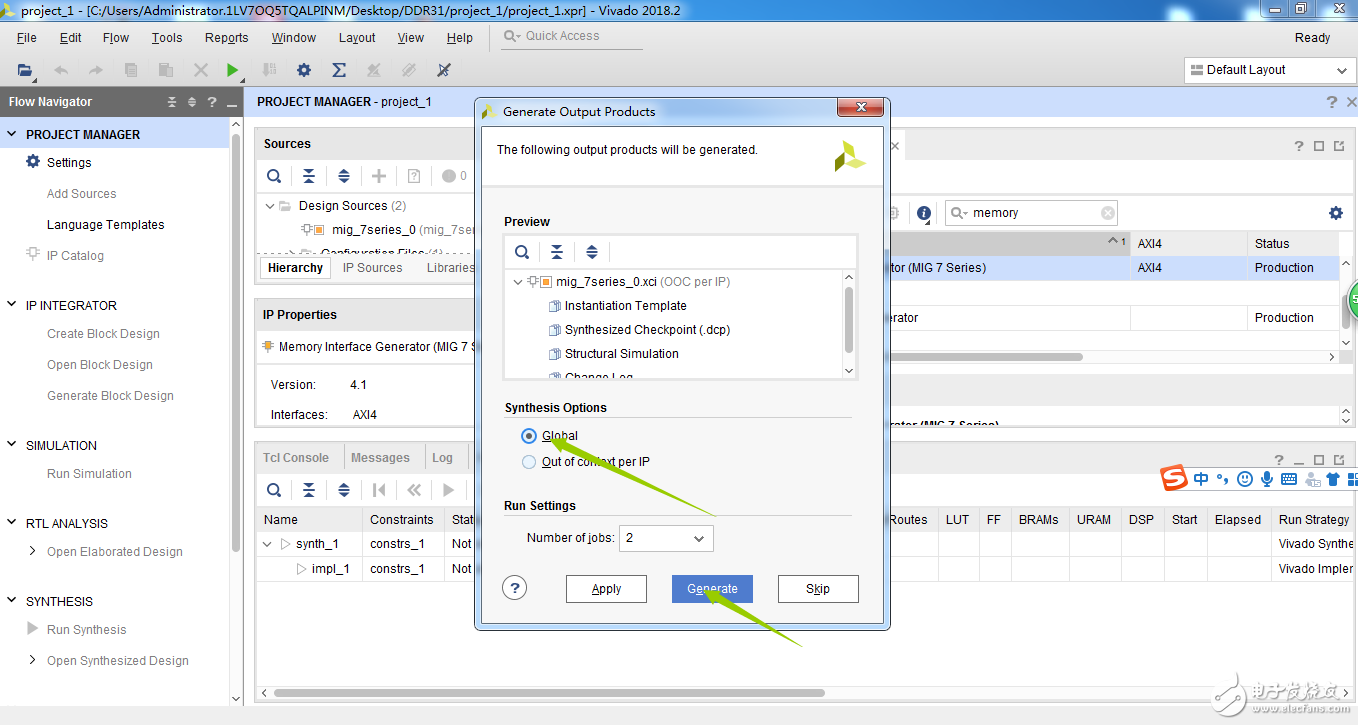

11、选择global,generate。

完毕。

责任编辑:zl

-

DDR3 SDRAM参考设计手册2025-11-05 385

-

DDR3 SDRAM配置教程2025-04-10 4498

-

基于AXI总线的DDR3读写测试2023-09-01 7919

-

DDR SDRAM与SDRAM的区别2023-04-04 5327

-

硬件和布局设计DDR3 SDRAM的考虑因素2022-03-31 751

-

lattice DDR3 IP核的生成及调用过程2022-03-16 2893

-

如何根据Xilinx官方提供的技术参数来实现对IP核的读写控制2022-02-08 920

-

XILINX DDR3 VIVADO(二)写模块2021-12-04 964

-

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解2020-12-31 7175

-

基于FPGA的DDR3 SDRAM控制器的设计与优化2018-08-02 5108

-

ddr3 sdram controller with uniphy 17.1 无法例化2018-05-14 3980

-

SDRAM,DDR3,DDR2,DDR4,DDR1的区别对比及其特点分析2017-11-17 28460

-

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢2016-01-14 23954

-

基于Stratix III的DDR3 SDRAM控制器设计2010-07-30 870

全部0条评论

快来发表一下你的评论吧 !