基于GaN器件的驱动设计方案

接口/总线/驱动

描述

氮化镓(GaN)是最接近理想的半导体开关的器件,能够以非常高的能效和高功率密度实现电源转换。但GaN器件在某些方面不如旧的硅技术强固,因此需谨慎应用,集成正确的门极驱动对于实现最佳性能和可靠性至关重要。本文着眼于这些问题,给出一个驱动器方案,解决设计过程的风险。

正文

氮化镓(GaN)HEMT是电源转换器的典范,其端到端能效高于当今的硅基方案,轻松超过服务器和云数据中心最严格的80+规范或USB PD外部适配器的欧盟行为准则Tier 2标准。虽然旧的硅基开关技术声称性能接近理想,可快速、低损耗开关,而GaN器件更接近但不可直接替代。为了充分发挥该技术的潜在优势,外部驱动电路必须与GaN器件匹配,同时还要精心布板。

对比GaN和硅开关

更高能效是增强型GaN较硅(Si)开关的主要潜在优势。不同于耗尽型GaN,增强型GaN通常是关断的器件,因此它需要一个正门极驱动电压来导通。增强型GaN的更高能效源于较低的器件电容和GaN的反向(第三象限)导电能力,但反向恢复电荷为零,这是用于硬开关应用的一个主要优点。低栅极源和栅极漏电容,产生低总栅电荷,支持门极驱动器快速门极开关和低损耗。此外,低输出电容提供较低的关断损耗。可能影响实际GaN性能的其他差别是没有漏源/栅雪崩电压额定值和相对较低的绝对最大门极电压,Si MOSFET约+/-20V,而GaN通常只有+/-10V。另外,GaN的导通阈值(VGTH) 约1.5V,远低于Si MOSFET(约3.5V)。如果外部驱动和负载电路能够可靠地控制源极和门极电压,开关频率可达数百kHz或MHz区域,从而保持高能效,进而减小磁性器件和电容尺寸,提供高功率密度。

GaN门极驱动对性能至关重要

使门极驱动电压保持在绝对最大限值内并不是唯一的要求。对于最快的开关,一个典型的GaN器件需要被驱动到约5.2V的最佳VG(ON)值,这样才能完全增强,而不需要额外的门极驱动功率。驱动功率PD由下式得出:

其中VSW为总门极电压摆幅,f为开关频率,QGTOT为总门极电荷。虽然GaN门极具有有效的电容特性,但在门极的有效串联电阻和驱动器中功率被耗散。因此,使电压摆幅保持最小很重要,特别是在频率很高的情况下。通常,对于GaN来说,QGTOT是几nC,约是类似的硅MOSFET值的十分之一-这也是GaN能够如此快速开关的原因之一。GaN器件是由电荷控制的,因此对于纳秒开关具有纳米库仑门极电荷,峰值电流为放大器级,必须由驱动器提供,同时保持精确的电压。

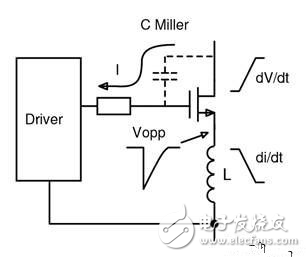

理论上,GaN器件在VGS = 0安全关断,但在现实世界中,即使是最好的门极驱动器,直接施加到门极的电压也不可能是0V。根据VOPP = -L di/dt (图1),在门极驱动回路共有的源引线中的任何串联电感L都会对门极驱动器产生相反的电压VOPP,这会导致高源di/dt的假开关。同样的影响可能是由关态dv/dt迫使电流流过器件的“Miller”电容造成的,但对于GaN,这可忽略不计。一种解决方案是提供一个负门极关断电压,可能-2或-3V,但这使门极驱动电路复杂,为避免复杂,可通过谨慎布板和使用以‘开尔文连接’和具有最小封装电感的器件如低高度、无铅PQFN型封装。

图1:源极和门极驱动共有的电感会引起电压瞬变

高边门极驱动的挑战

GaN器件不一定适合于所有的拓扑结构,如大多数“单端”反激式和正激式没有反向导通,而且其高于硅MOSFET的额外成本超过了任何小的能效优势。然而,“半桥”拓扑-如图腾柱无桥PFC、LLC转换器和有源钳位反激-将自然成为GaN的根据地,无论是硬开关还是软开关。这些拓扑都有“高边”开关,其源是个开关节点,因此门极驱动被一个具有纳秒级的高压和高频波形所抵消。门极驱动信号于参照系统地面的控制器,因此高边驱动器必须将电平移位与适当的耐压额定值(通常为450 V或更高)结合起来。它还需要一种为高边驱动产生低压电源轨的方法,通常采用由自举二极管和电容组成的网络,参照开关节点。开关波形应力为dV/dt,GaN可达100 V/ns以上。这导致位移电流流经驱动器到地面,可能导致串联电阻和连接电感的瞬态电压,可能损坏敏感的差分门极驱动电压。因此,驱动器应具有较强的dV/dt抗扰度。

为了最大限度地防止灾难性的“击穿”和实现最佳能效,半桥高边和低边器件应保证无重叠被驱动,同时保持最少的死区时间。因此,高边和低边驱动应有控制非常好的、匹配的传播延迟。

对于低边,接地驱动器应直接在开关源进行开尔文连接,以避免共模电感。这可能是个问题,因为驱动器也有一个接地信号,这可能不是最好的连接。因此,低边驱动器可能采用隔离或某种分离功率和信号的方法,具有一定程度的共模电压容限。

GaN驱动器可能需要安全隔离

现在增强型GaN器件正受到极大的关注用于离线应用,这种应用要求设备及其驱动器至少有600 V的高压额定值,但较低的电压应用越来越普遍。如果驱动器输入信号由控制器产生,可通过通信接口人工访问连接,则驱动器将需要符合相关代码的安全隔离。这可通过高速信号伽伐尼隔离器以适当的绝缘电压实现。保持驱动器信号边缘率和高低边匹配成为这些布板的问题,虽然控制器电路常被允许‘primary-referenced’,但无论如何,在大多AC-DC转换器中这是常态。

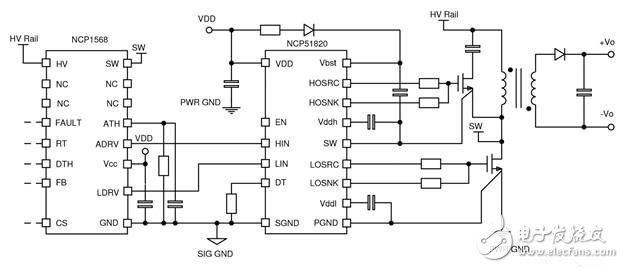

应用示例 – ‘有源钳位反激’

这是个有源钳位反激拓扑的例子(图2),使用一个高边开关将换流变压器的漏感能量循环供应。与“缓冲”或硬齐纳钳位法相比,能效更高,EMI更好,漏波更干净,电路应用功耗低,在45W到150 W之间,典型的应用包括支持USB PD的手机和膝上型计算机的旅行适配器,以及嵌入式电源。

图2:GaN有源钳位反激转换器概览

图2显示安森美半导体的NCP51820专用GaN门极驱动器[1]及NCP1568[2]有源钳位反激控制器 (细节省略)。该驱动器采用具有调节的+5.2V幅度的门极驱动器用于高边和低边最佳增强型GaN。其高边共模电压范围-3.5V到+650V,低边共模电压范围为-3.5至+3.5V,dv/dt抗扰度200 V/ns,采用了先进的结隔离技术。如果在低边器件源极有一个电流检测电阻器,低边驱动电平移位使开尔文连接更容易。驱动波形的上升和下降时间为1ns,最大传播延迟为50 ns,且高低边提供独立的源汲输出,以定制门极驱动边沿,达到最佳的EMI/能效折衷。在这种拓扑结构中,高低边驱动器不重叠,但具有不同的脉冲宽度,以实现由NCP1568器件控制的具漏极钳位和零电压开关的电源转换/调节。

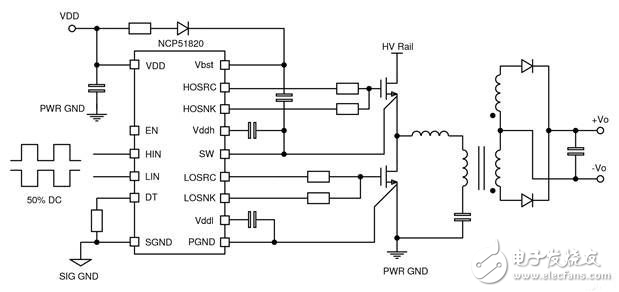

应用示例 – LLC转换器

在功率大于150 W的情况下,谐振式LLC转换器因能效高、开关电压应力有限而常被使用。该转换器的一个特点是驱动波形为50%的占空比,通过变频调节。因此,控制死区时间以保证不发生重叠至关重要。图3显示了NCP13992高性能LLC控制器的典型架构。这种设计可以在500 kHz的开关频率下工作,并且通常用于大功率游戏适配器和OLED电视、一体化电脑的嵌入式电源。

图3:基于GaN的LLC转换器概览

所示的安森美半导体NCP51820驱动器确保门极驱动不重叠,但这可视拓扑需要(如电流馈电转换器)而禁用。该器件还含一个使能输入和全面的保护,防止电源欠压和过温。它采用PQFN、4×4mm 的15引线封装,使短、低电感连接到GaN器件的门极。

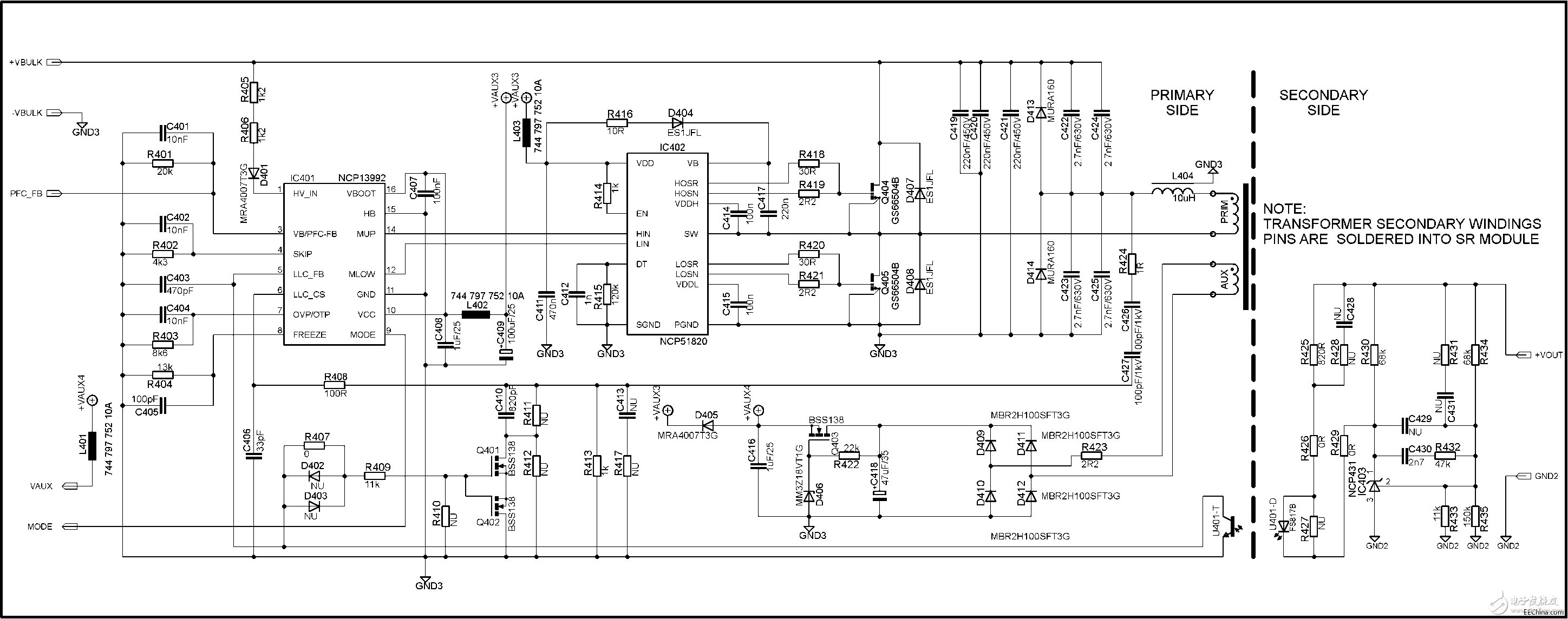

布板考量

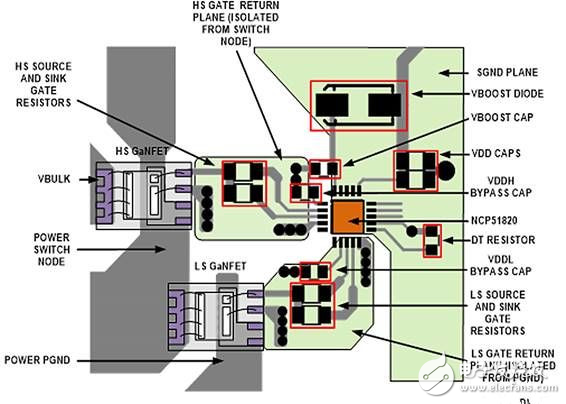

在所有应用中,布板是成功的关键。图4显示了一个采用安森美半导体的NCP51820的示例布板,微型化并匹配门驱动回路。GaN器件和驱动器被置于PCB同侧,通过适当地使用接地/返回面来避免大电流通孔。

图4:GaN门极驱动电路的好的布板

总结

对于GaN开关,需要仔细设计其门极驱动电路,以在实际应用中实现更高能效、功率密度及可靠性。此外,谨慎的布板,使用专用驱动器如安森美半导体的NCP51820,及针对高低边驱动器的一系列特性,确保GaN器件以最佳性能工作。

-

德州仪器:GaN器件的直接驱动配置2020-08-04 2309

-

GaN转变充电器设计方案详解2021-04-07 4850

-

基于GaN器件的驱动设计方案2022-07-12 4523

-

求告知LED驱动电源的设计方案2016-08-11 3584

-

未找到GaN器件2019-01-17 3017

-

基于GaN的开关器件2019-06-21 3599

-

GaN HEMT在电机设计中有以下优点2019-07-16 3326

-

直接驱动GaN晶体管的优点2020-10-27 1751

-

压电马达的驱动设计方案2021-03-04 2164

-

直接驱动GaN器件可实现更高的开关电源效率和更佳的系统级可靠性2023-02-14 1079

-

GaN器件在Class D上的应用优势2023-06-25 2439

-

TILED驱动设计方案详细资料2018-04-13 1254

-

集成汽车 GaN 功率器件2022-08-03 1432

-

GaN驱动技术手册免费下载 氮化镓半导体功率器件门极驱动电路设计方案2025-03-13 55126

-

“芯”品发布 | 高可靠GaN专用驱动器,便捷GaN电源设计2025-11-11 1107

全部0条评论

快来发表一下你的评论吧 !