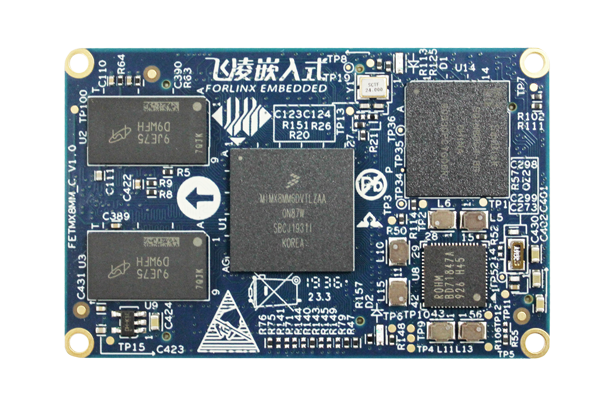

飞凌嵌入式FETMX8MM-C核心板介绍

描述

CPU:NXP i.MX8M Mini

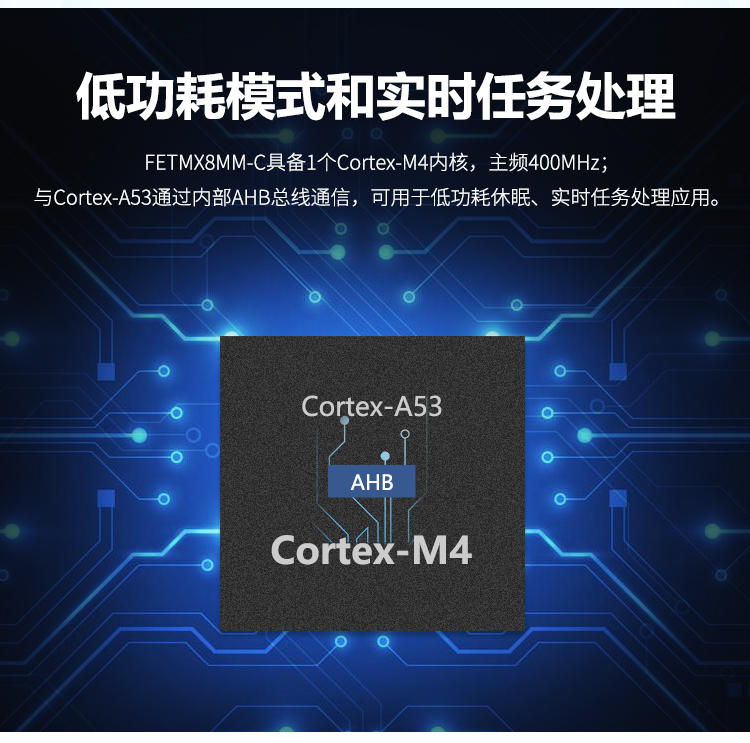

架构:四核Cortex-A53+M4

主频:1.8GHz

内存:2GB DDR4

ROM:8GB eMMC

系统:Linux4.14.78+QT5.10.1、Android9.0

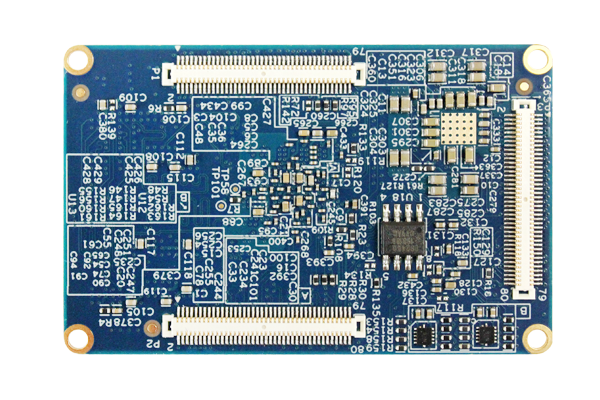

FETMX8MM-C 核心板基于NXP 公司的i.MX8M Mini 四核64位处理器设计,主频最高1.8GHz,ARM Cortex-A53架构;2GB DDR4 RAM,支持一个通用型Cortex®-M4 400 MHz内核处理器。可提供多种音频接口,包括I2S、AC97、TDM、PDM和SPDIF。提供多种外设接口,如MIPI-CSI、MIPI-DSI、USB、PCIe、UART、eCSPI、IIC和千兆以太网。

目标应用:

·IP摄像头视频监控 ·双向视频会议

·可视门铃 ·图像分析

·音频处理 ·音频广播系统

-

Cortex A53 Core:

• 4x Cortex-A53 processors

-

• Target frequency of 1.8GHz

-

• Support of 64-bit Armv8-A architecture

-

• Floating Point Unit (FPU) with support of the VFPv4-D16 architecture

-

• 32 KB L1 Instruction Cache

-

• 32 KB L1 Data Cache

-

• 512 KB unified L2 cache

-

Cortex M4 Core:

• 1x Cortex-M4 processor

-

• frequency of 400MHz

-

• 256 KB tightly coupled memory (TCM,128 KB TCMU, 128 KB TCML)

-

• 2GB

-

• DDR4

-

• 8GB

-

• eMMC Flash

-

LCDIF Display Controller:

-

• Support up to 2 layers of overlay

-

• Support up to 1080p60 display through MIPI DSI

-

MIPI Interface:

-

• 4-lane MIPI CSI interface,operating up to a maximum bit rate of 1.5 Gbps.

-

• 4-lane MIPI DSI interface,operating up to a maximum bit rate of 1.5 Gbps.

-

Audio:

-

• SPDIF input and output, including a new Raw Capture input mode

-

• Five synchronous audio interface (SAI) modules supporting I2S,AC97, TDM,codec/DSP,and DSD interfaces, including one SAI with 8 Tx and 8 Rx lanes, one SAI with 4 Tx and 4 Rx lanes,two SAI with 2 Tx and 2 Rx lanes,and one SAI with 1 Tx and 1Rx lane. Support over 20 channels of audio subject to I/O limitations.

-

• 8-Channel Pulse Density Modulation (PDM) input

-

3D GPU Core:

-

• GCNanoUltra

-

• Support OpenGL ES 1.1, 2.0

-

• Support OpenVG 1.1

-

• TrustZone support using a local MMU to manage secure regions

-

2D GPU Core:

-

• GC320

-

• Support multi-source composition

-

• Support one-pass filter

-

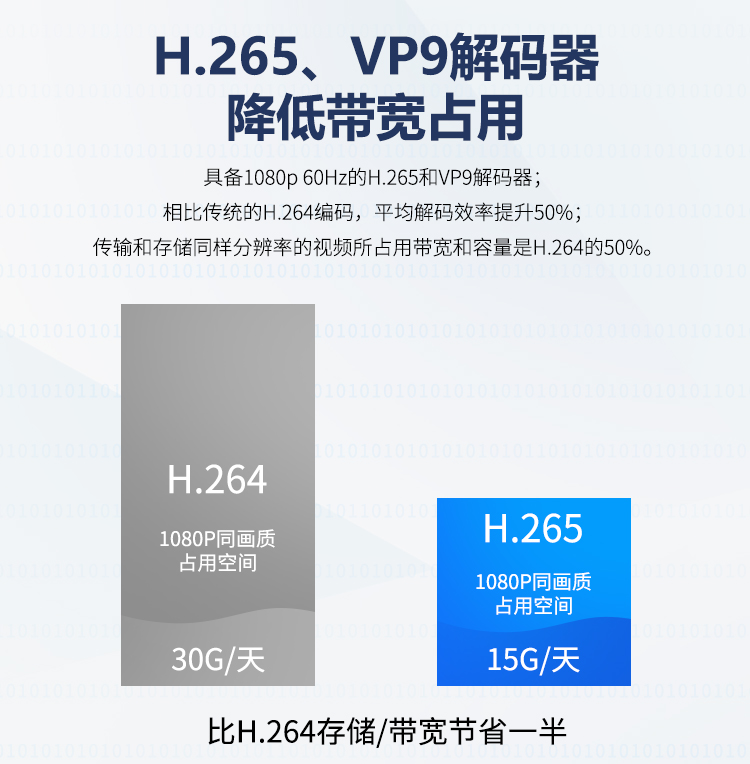

Decoder:

-

• 1080p60 VP9 Profile 0, 2 (10-bit)

-

• 1080p60 HEVC/H.265 Decoder

-

• 1080p60 AVC/H.264 Baseline, Main, High decoder

-

• 1080p60 VP8

-

Encoder:

-

• 1080p60 AVC/H.264 Encoder

-

• 1080p60 VP8

-

One PCI Express (PCIe)

-

• Single lane supporting PCIe Gen2

-

• Dual mode operation to function as root complex or endpoint

-

• Integrated PHY interface

-

• Support L1 low power sub-state

-

Two USB 2.0 OTG controllers with integrated PHY interfaces

-

Two Ultra Secure Digital Host Controller (uSDHC) interfaces:

-

• SD/SDIO 3.0 compliance with 200 MHz SDR signaling to support up to 100MB/sec

-

• Support for SDXC (extended capacity)

-

• 1.8 V and 3.3 V operation, but do not support 1.2V operation.

-

One Gigabit Ethernet controller:

-

• support for Energy Efficient Ethernet (EEE)

-

• Ethernet AVB,

-

• IEEE 1588

-

Four Universal Asynchronous Receiver/Transmitter (UART) modules:

-

• 7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even,odd, or none)

-

• Programmable baud rates up to 4 Mbps.

-

• 32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud

-

Four I2C modules:

-

I2C provides serial interface for external devices. Data rates of up to 320 kbps are supported.

-

Three eCSPI modules:

-

Full-duplex enhanced Synchronous Serial Interface, with data rate up to 52 Mbit/s. Configurable to support Master/Slave modes, four chip selects to support multiple peripherals.

-

The FlexSPI module acts s an interface to external serial flash devices. This module contains the following features:

-

• Flexible sequence engine to support various flash vendor devices

-

• Single pad/Dual pad/Quad pad mode of operation

-

• Single Data Rate/Double Data Rate mode of operation

-

• Parallel Flash mode

-

• DMA support

-

• Memory mapped read access to connected flash devices

-

• Multi master access with priority and flexible and configurable buffer for each master

-

飞凌嵌入式i.MX8M Mini核心板已支持Linux6.12025-01-10 3119

-

低成本与高性能兼备,FETMX8MPL-C核心板上新2024-12-10 1378

-

首发!飞凌嵌入式FETMX6ULL-S核心板已适配OpenHarmony 4.12024-05-20 1705

-

稳定运行矿山鸿蒙系统——飞凌嵌入式的这2款核心板获得「矿鸿资质证书」2024-02-23 1732

-

基于飞凌嵌入式FETMX8MM-C核心板的血细胞分析仪2024-02-02 1380

-

飞凌嵌入式亮相CACLP 2022,让医疗设备更智能2022-10-28 1666

-

ARM核心板,为医疗设备不断赋能2022-06-30 9529

-

动态讲解-一起了解这款尺寸仅29x40mm的小尺寸FETMX6ULL-C核心板2022-05-05 1619

-

FETMX6Q-C核心板有哪些优势呢2021-12-20 969

-

测评|飞凌iMX8MP核心板多媒体功能测评2021-11-05 14415

-

飞凌FETMX8MM-C核心板在麻醉系统中的应用2021-10-26 2632

-

飞凌iMX8MM核心板在麻醉系统中的应用2021-10-23 9111

-

FETMX8MM-C核心板之管道巡检机器人控制平板方案分享2020-10-13 2035

-

低调的奢华-飞凌嵌入式FETMX6Q-C是怎么练成的2016-10-07 22181

全部0条评论

快来发表一下你的评论吧 !