Intel的核显真的占用了CPU的4根PCI-E通道吗

处理器/DSP

描述

在讨论到CPU的PCI-E通道问题时,我发现很多人都以为Intel的核显占用了CPU的4根PCI-E通道,包括很多可以找到的“科普贴”中都写了核显会占用4条PCI-E通道。其实这是一种常见的误区,从Sandy Bridge架构开始,Intel的核显就是挂在Ringbus这个内部环形总线上面的,它不会占用CPU的PCI-E通道。

TL;DR: 从Sandy Bridge开始,Intel的核显就挂在Ringbus上面,不占用PCI-E通道。

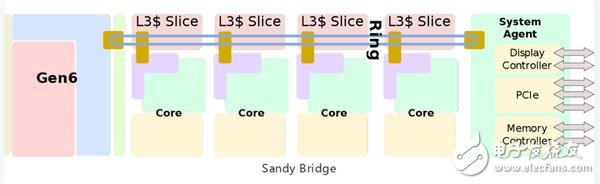

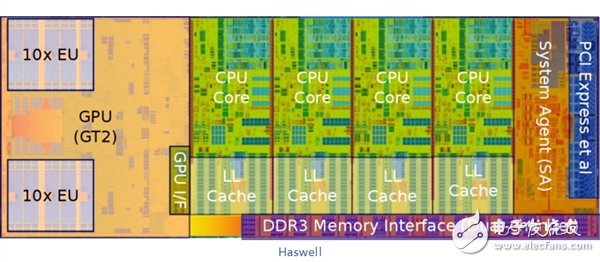

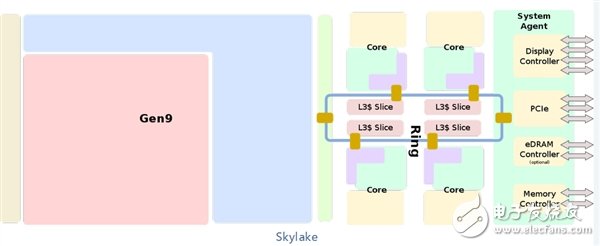

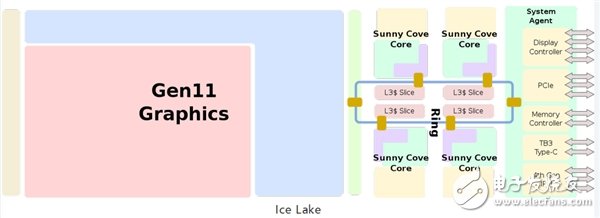

要看证据的话,我我们从Sandy Bridge开始摆架构简图/Die Shot:

可以看到,从Sandy Bridge开始,核显部分都是以节点形式挂在Ringbus上面的。而CPU的PCI-E控制器在另外一端的System Agent组件中,中间隔了万水千山。

如果还要证据的话,简单测试一下核显的内存带宽就知道了,比如我这台工作机上面的HD 4600,分配了32MB的显存,简单跑一下,显存带宽超过9GB/s,很明显这个带宽已经超过了PCI-E 3.0 x4的上限3.94 GB/s了。GPU-Z也可以告诉你,核显不占用PCI-E通道数。

所以,不要再相信什么屏蔽核显释放PCI-E总线的说法了,没有用的。

题外话,其实在传奇的E3V2上面Intel是给了20条PCI-E 3.0总线的,而到下一代又缩回去了。

那为什么Intel和AMD在主流级桌面平台上面都不多给一点PCI-E总线通道呢?因为增加CPU的PCI-E总线通道需要修改CPU的触点设计,增加CPU触点的同时会引发CPU封装体积的变大,成本变高。所以Intel的主流桌面级CPU至今仍只提供16条直连通道,而更多的PCI-E通道需要通过DMI 3.0由芯片组分出。

责任编辑:wv

-

pci-e插槽的规格有哪些 各个版本的pci-e的规范区别2023-08-05 16917

-

什么是PCI PCI-X PCI-E?2021-10-25 1833

-

PCI PCI-X PCI-E介绍 精选资料分享2021-07-29 1874

-

PCI-E接口的固态硬盘和SATA接口的区别是什么2020-07-28 8535

-

英特尔Rocket Lake处理器部分功能泄露 或将支持PCI-e 4.02020-07-23 3144

-

Intel核显开始发力,不比独显差多少2018-06-05 4718

-

浅谈显卡PCI/AGP/PCI-E接口的区别2017-11-03 10641

-

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡2017-10-19 7191

-

pci-e布线规范2016-07-14 4976

-

Intel新一代处理器Skylake:全新的GT4e核显2015-05-13 4155

-

PCI-e总线FPGA开发板资料说明2011-04-14 2127

-

PCI-E 的PADS封转2011-03-30 2806

-

南桥PCI-E通道数2009-12-26 744

-

PCI-E接口定义 引脚定义图 PCI-E针脚定义图2008-04-27 85472

全部0条评论

快来发表一下你的评论吧 !