JEDEC定义了一种串行复位协议,用以取代专用复位引脚

电子说

描述

行业标准组织JEDEC定义了一种串行复位协议,用以取代专用复位引脚。

今天的嵌入式系统,例如智能设备和物联网终端,通常都要求在实现高性能与低功耗的同时提供实时启动功能。所有电子系统还要具备从瞬态故障引起的状况中恢复的能力。这些故障通常与信号完整性密切相关,这使得当今的高速系统设计更具挑战性。

从运行时出现的故障中恢复通常需要能够对系统的全部或部分进行受控复位。极端情况下,若尚未提供软复位功能,此时就可能会提示需要重新启动设备。而对于远程的物联网终端来说,重启可能存在困难而且成本高昂。这只是说明嵌入式设计中复位功能重要性的一个示例。

串行外设接口(SPI)广泛应用于将外设和存储器连接到嵌入式系统中的微控制器或处理器中。复位串行闪存是初始化或恢复的重要部分。为使主机处理器能够更容易地重置SPI存储器,行业标准组织JEDEC定义了一种串行复位协议,替代了使用专用复位引脚来进行复位。本文介绍了该复位协议及其用法,特别参考了扩展SPI(xSPI)和串行非易失性存储器的执行代码。

SPI闪存的作用

串行接口相对于并行总线的主要优点是减少了所需信号数量。在大多数情况下,较少的信号和I/O引脚可降低元件成本与功耗,因为驱动片外信号所需的功率是总功率消耗的主力军。

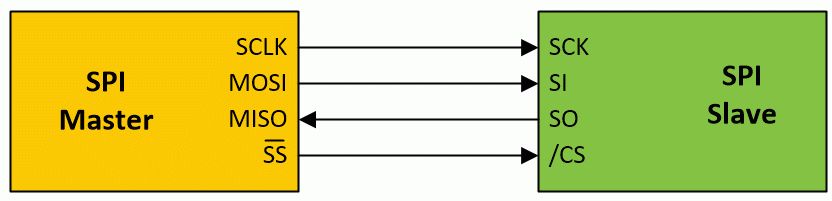

最初的SPI规范包括四种信号:一个串行时钟(SCLK)信号,用于同步数据传输;一个或多个芯片选择(SS)信号用于实现寻址多个目标;以及两个数据信号(MOSI和MISO),用于在每个方向上传输数据。该标准目前已经以各种方式进行了扩展以实现更高的性能,现在更拓展了通过SPI接口执行软复位的功能。

串行外设接口(SPI)(来源:Adesto Technologies)

SPI接口不断演变和发展以扩大带宽,其变体现在包括dual SPI(双线SPI),它使用半双工配置中的两个数据引脚在每时钟周期内发送两个bit的数据;还有quad SPI(四线SPI)和octal SPI(八线SPI),它们增加了更多数据线,使得每个时钟周期可以传输更多位数。此外,这些SPI都可在双倍数据速率(DDR)模式下使用,且支持在两个时钟边缘传输数据。

Quad和Octal SPI接口由JEDEC的扩展SPI(xSPI)标准JESD251定义,该标准提供的硬件指导可以实现系统中高吞吐量xSPI器件的无故障集成。

最近,JEDEC还定义并发布了一个标准,规定了通过串行接口重置设备。该复位协议在JEDEC标准JESD252中定义,它取消了在串行闪存中使用专用复位引脚来进行复位的需求。

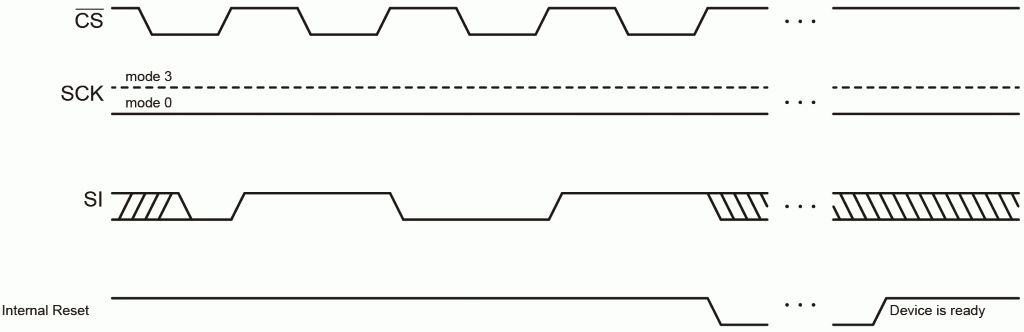

该标准定义了芯片选择信号、时钟信号和输入数据信号需要遵循的特定顺序,以使器件执行硬件复位。使用该模式使得由串行数据线上的噪声引起的伪转换不会导致意外复位。在复位期间,时钟信号保持低电平,进一步确保了引脚转换不会被解释为数据传输,而芯片选择引脚则用于确保仅复位特定的器件。

复位协议(来源:Adesto Technologies)

SPI闪存被广泛应用于嵌入式产品,特别是用于其代码。这使得它对系统整体功能而言显得至关重要,因此必须保持可靠的运行,包括具备必要时发起复位的能力。

利用复位进行初始化和恢复

系统通常在通电时使用复位功能来确保系统中所有器件都以已知状态启动。复位还可用于在运行期间从可能由硬件问题引起的严重故障中恢复,其中包括信号完整性问题和时序问题、电磁干扰或由背景辐射引起的随机存储器损坏(另请参见《MiTIgating Metastability》这篇文章);还可用于由软件错误可能导致的程序崩溃和无响应。

这些偶发的错误对于消费者可能是仅仅造成不便,但对于具有数千个节点需要高可用性的物联网而言,却是一个严重的问题。在越来越多的情况下,手动复位或重启这些物联网设备变得越来越不可能。嵌入式系统通常使用看门狗定时器和其它自检机制来检测故障并采取纠正措施。这就可能意味着执行“软”复位,其中只有必要的子系统在处理器的控制下被复位。

SPI接口是有状态的(stateful)。例如,在接收到命令之后,闪存将期望有一定数量的地址或数据传输。导致主机和内存之间失去同步的任何错误都将引起不可预测的行为。要从中恢复,主机需要能够通过执行软复位将串行存储器重置为已知状态。这种复位有助于保持系统稳定,而且是在没有看到任何外部故障指示的情况下进行的。也因为如此,软复位现在被认为是嵌入式系统操作的一个标准特性。

有些串行闪存可能有一个专用的复位引脚;但另一些则使用多路复用以减少引脚数,此时,复位引脚同时也是一个I/O引脚;但有时候,制造商可能根本不提供复位功能。即使有复位引脚,专门指定微控制器的一个输出去控制它也不实际。

JESD252规范的产生使得串行闪存设备无需专用或物理复位引脚仍然可以支持复位功能。除了故障恢复之外,还可以在上电启动时使用串行复位机制,以确保电源稳定后串行存储器也能正确启动。

芯片内执行(XiP)

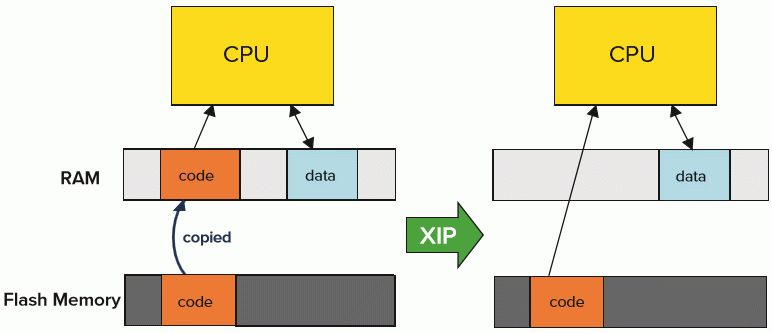

传统的串行闪存通过低速SPI连接,这意味着如果这些器件用于存储程序存储器,则处理器在执行代码之前必须先将代码复制到片上SRAM中。而芯片内执行,即XiP,是通过提供更快更宽的接口省去了代码复制步骤的串行闪存。反过来,这减少了对片上SRAM的需求,从而降低了主机微控制器或处理器的价格。

与其他八通道器件相比,Adesto的EcoXiP采用octal SPI接口,具有高性能和极低功耗,并且具有比quad-SPI存储器高得多的性能。

Execution modes (Source: Adesto Technologies)

执行模式 (来源: Adesto Technologies)

对于现代嵌入式设备来说,XiP的开发极具价值,不仅仅是因为片上闪存的昂贵和尺寸上的限制。微控制器通常最多具有1 MB的内存,但现代物联网节点通常需要更多的代码空间用于通信堆栈、无线接口、音频处理、机器视觉和应用软件等功能。利用XiP的外部闪存可以实现更大的代码存储空间。而且由于减去了代码传输阶段,启动时间也缩短了。

XiP的使用使得SRAM无需存储代码而是仅用于存储数据,从而减少了所需的SRAM数量。因为削减了对外部SRAM的需求或允许微控制器使用较少的片上SRAM,系统成本也相应降低。由于NOR闪存(非易失性闪存)允许随机访问,而微控制器需要将串行接口映射到其自己的存储空间,因此它被视为另一个存储区域,从而支持XiP。为了进一步提高性能,EcoXiP还针对代码执行进行了优化。

标准SPI接口设计都支持随机访问;每次读取都包含命令、地址和返回的数据。数据返回后,才可以进行再次请求。但是,指令通常从连续地址中获取。EcoXiP接口充分利用了这一点,为每个读取请求提供连续字节,直到具有新地址的命令被发送为止。这使得总线吞吐量加倍,因为消除了为每次提取发送新地址的延迟。

EcoXiP可以持续以156MB/s(峰值速率为266 MB/s)的速率发送指令。

传统NOR闪存的另一个问题是写入比读取慢几个数量级。这意味着当代码在闪存中执行时无法将数据写入闪存,因为这样会对性能产生重大影响。EcoXiP通过灵活地将存储器划分为独立的存储体来支持并发读写。这使得采用XiP可以在执行代码的同时,将数据保存到存储器并执行(Over-the-AIr,OTA)空中更新。

对JEDEC标准的支持,包括远程复位的支持,使业界采用XiP串行闪存变得更加简单。

结论

在主处理器的控制下能够复位串行闪存是嵌入式系统的重要需求。JEDEC JESD252串行复位协议可实现该功能,而无需存储器上的复位引脚或来自微控制器或主机处理器的专门信号。

尽管使用串行复位和XiP会影响主机和存储器的设计,还是有越来越多的微控制器正在增加对这些标准的支持。Adesto是第一家提供串行NOR闪存的制造商,其产品支持串行闪存复位信令协议和xSPI标准。EcoXiP可在提供所需执行能力的同时降低系统功耗与成本。它还兼容串行闪存发现标准,并具有改善能效和安全的其它特性。

拥有上述技术,嵌入式工程师可以更好地应对开发物联网产品时所面临的挑战。

-

FPGA复位的8种技巧2024-11-16 2094

-

复位电路的复位条件和复位过程2024-01-16 2496

-

RC复位电路中R如何影响芯片复位?2023-10-25 2525

-

如何远程复位串行SPI存储设备2022-10-24 1438

-

一种软件模拟内核复位的方法2022-03-14 2882

-

STM32的电源复位和引脚复位2022-01-07 934

-

19--一种移动式轨道运输车辆掉道复位装置2021-09-22 842

-

PCI总线中定义了四种复位名称2018-09-04 8257

-

430怎么复位_430软复位方法详解2018-05-20 7302

-

上电复位和按键复位区别2017-10-20 120027

-

复位电路工作原理和作用以及基本复位方式解析2017-05-12 70730

-

一种CMOS图像传感器像素复位电路2017-01-03 919

-

一种片上系统复位电路的设计2013-09-25 672

-

一种单键开关机和复位方案2011-08-31 13994

全部0条评论

快来发表一下你的评论吧 !