大功率DC/DC转换器的EMC和效率优化

大功率DC/DC转换器的EMC和效率优化

电子说

1.4w人已加入

描述

1.概述

选择合适的电容器技术、存储电感、开关频率和半导体——相较其它因素——对于提高具有相对较高输入和输出电流的DC/DC开关电源的效率至关重要。一个高效的开关电源以及使用它的终端产品需要符合所有必要的EMC标准方可上市。这通常意味着输入和输出端必须另外加装合适的滤波器,以降低干扰发生。然而,如果输入和输出电流较高,则很难在滤波器的效率、尺寸、阻尼、成本以及实际性能水平之间作出权衡。本文档将通过一个100W升降压DC/DC设计示例,简要介绍作出这种权衡所需的注意事项、布局和器件。

图 1:100 W 降压-升压转换器的演示电路板。

2.项目范围

设计一款满足以下要求的升降压转换器:

18 Vout / Vin 14-24 Vdc 时 Pout 最高为 100 W

Iin max. = 7 A Iout max. = 5.55 A

输出100W 时效率超过95%

符合CISPR32 Class B干扰限值(传导和辐射)

低输出纹波(低于 20mVpp)

无法屏蔽

长输入和输出线缆(各1m)

尽可能紧凑

性价比尽可能高

为了满足这些严格的要求,必须设计出一种电感非常低、紧凑布局,以及能够匹配转换器的滤波器。如果考虑EMC,输入和输出线缆是频率范围高达1GHz的主要天线。由于现代四开关升降压转换器在输入和输出端都具有高频电流环路,因此必须根据工作模式对输入和输出进行滤波。这可以防止由于MOSFET快速开关导致的高频干扰进入线缆并产生辐射。

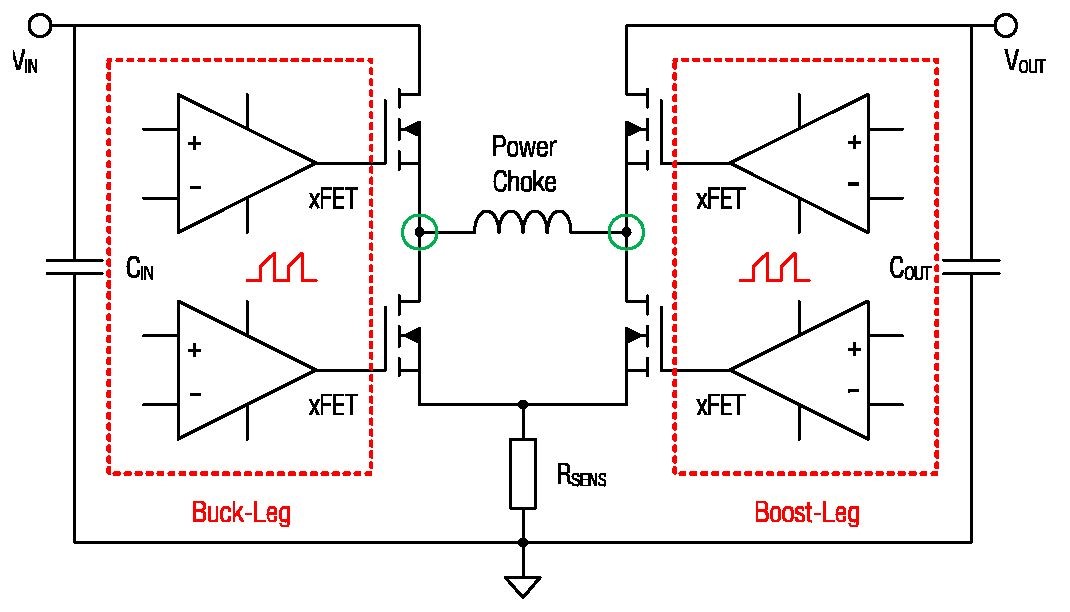

图2:高频 ΔI/Δt 环路和临界ΔU/Δt开关节点电路图,具体取决于转换器工作模式。

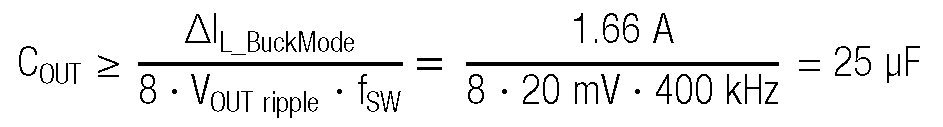

本应用使用了来自Linear Technology (Analog Devices) 的开关稳压器LT3790。其输入电压范围高达60VDC,开关频率可调,可控制四个外部MOSFET,使设计具有高度灵活性。

3.设计和测量

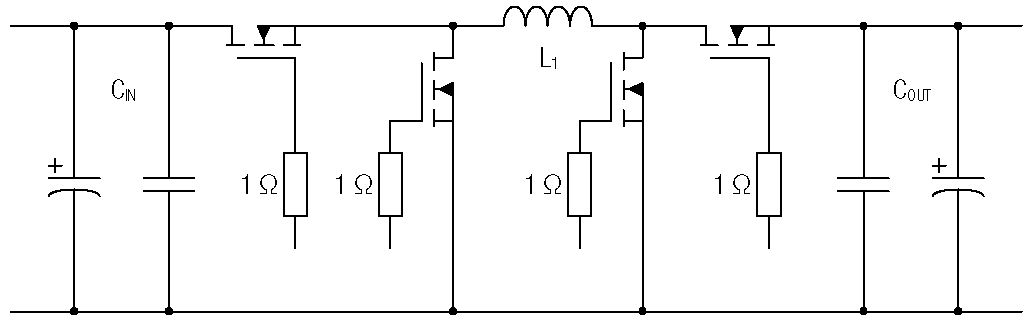

升降压电路设计的主要特点:

双面6层印刷电路板

400kHz开关频率

扼流圈中的电流纹波约为额定电流的30%

紧凑型60V MOSFET,具有较低的Rdson、Rth和封装ESL

1Ω栅极串联电阻

图3:转换器功率级简图。

3.1.电感选择

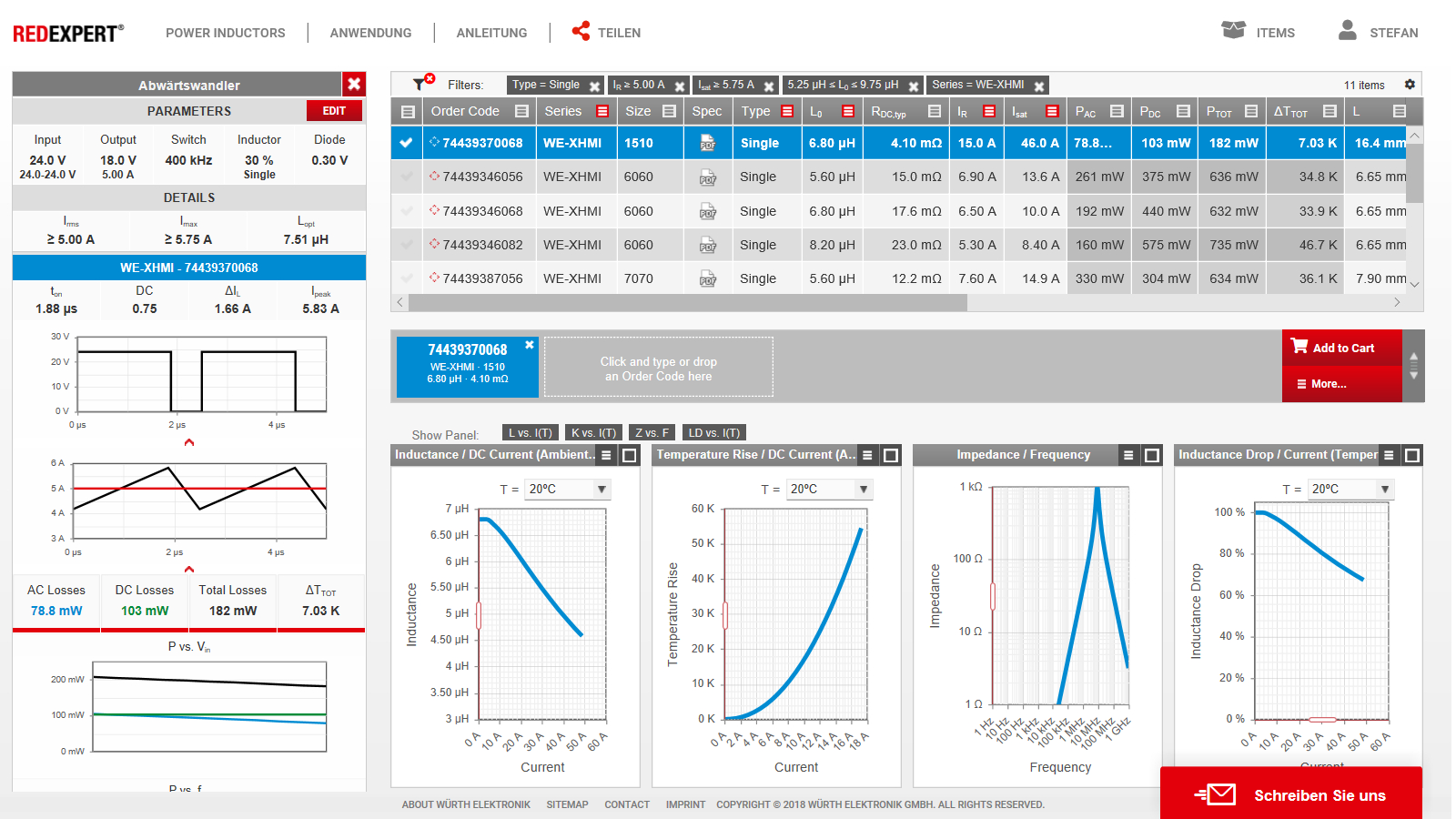

利用REDEXPERT在线平台,可以快速、轻松、精确地选择合适的电感。在此案例中,必须先为降压操作输入一次操作参数(Vin、fsw、Iout、Vout、ΔI),再为升压操作输入一次。

在降压操作中,需求一个更大的电感以及一个更小的最大峰值电流 (7.52 µH/5.83 A)。

在升压操作中,电感减小了,但最大峰值电流会增大 (4.09 µH/7.04 A)。

使用REDEXPERT选择电感的另一个好处是:可以根据不同器件复杂的交流和直流损耗、产生的器件发热以及它们的明显参数(尺寸、额定电流等),对它们进行比较。

在此案例中,选择了WE-XHMI系列屏蔽电感,电感值为6.8μH,额定电流为15A。由于采用现代制造技术,该器件的RDC极低,尺寸极小,仅15x15x10mm(长/宽/高)。其创新的磁芯配比材料还使其具有不受温度影响的软饱和特性。

图 5:WE-XHMI 74439370068 的 REDEXPERT 仿真(降压操作)。

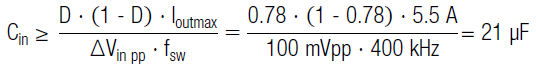

3.2.输入电容器选择

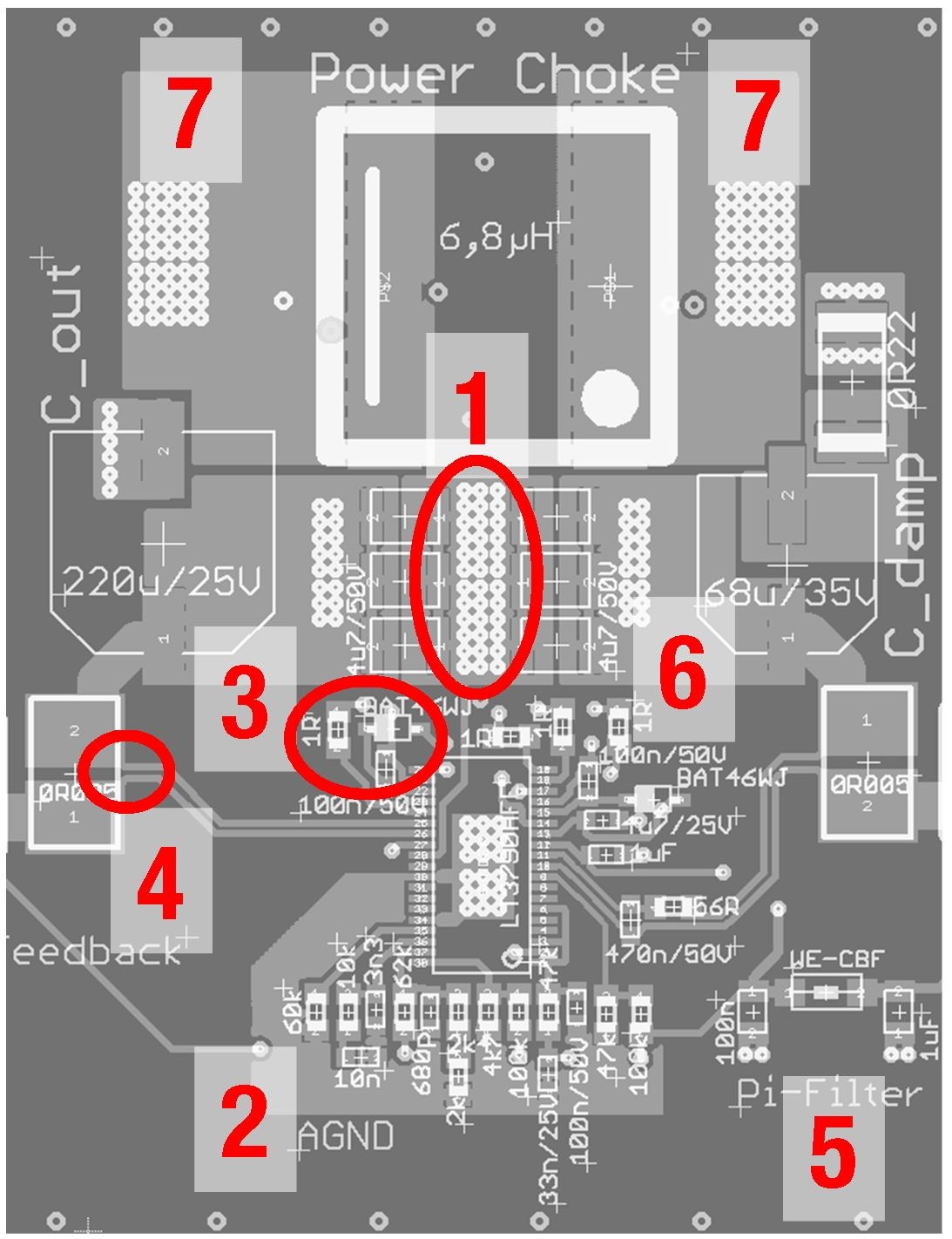

由于流过滤波电容器的脉冲电流较高,并且要确保较低的输出纹波,因此铝聚合物和陶瓷电容器的组合成为最佳选择。一旦最大输入和输出电压纹波设置完成后,可使用以下公式计算所需电容。

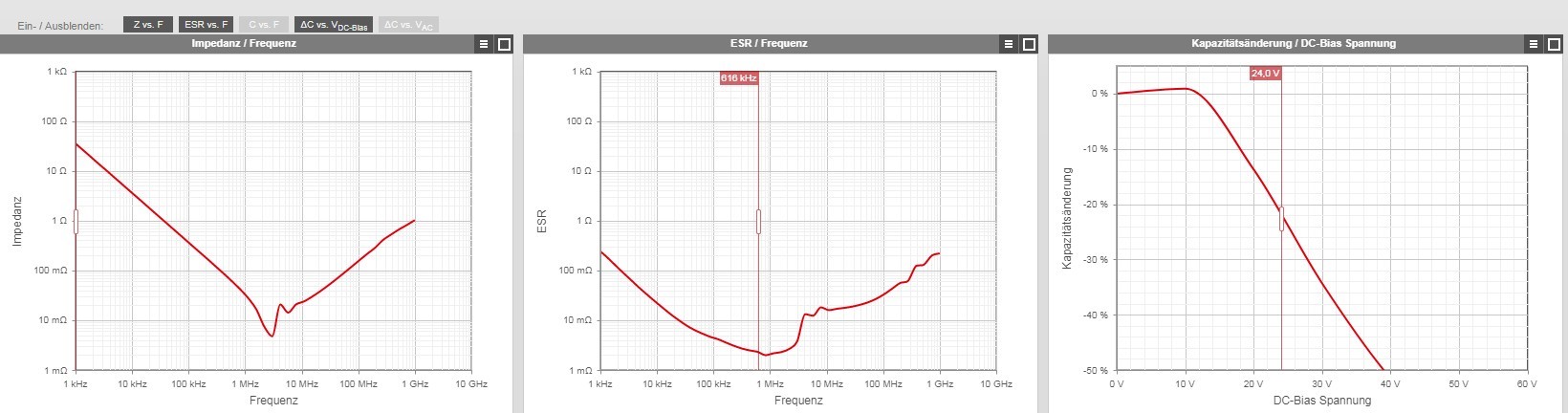

选择的电容:6 x 4.7µF / 50V / X7R = 28.2 µF (WCAP-CSGP 885012209048)

使用REDEXPERT,可以轻松、快速地确定MLCC的直流偏置,得出的值更接近实际,参见图6。结果:必须考虑到输入电压为24V 时电容会减少20%;因此有效容值只有23μF,但已足够。此外,将一个 68μF/35V WCAP-PSLC铝聚合物电容器与陶瓷电容器并联使用,串联一个0.22Ω SMD电阻。这有助于转换器的负输入阻抗与输入滤波器保持稳定(更多信息请参见ANP044)。由于该电容器也会有一定量的高脉冲电流流过,因此铝电解电容器在此案例中不太适用。较高的ESR会导致该类电容器温度过高。

图6:所选MLCC的REDEXPERT阻抗、ESR和直流偏置图。

3.3.输出电容器选择

选择的电容:6 x 4.7 µF / 50 V / X7R = 28.2 µF – 15% 直流偏置 = 24 µF (WCAP-CSGP 885012209048)

另加:1个铝聚合物电容器以快速响应瞬态信号:

WCAP-PSLC 220µF/25V

图7:100W升降压转换器电路图(包括所有滤波器器件)。

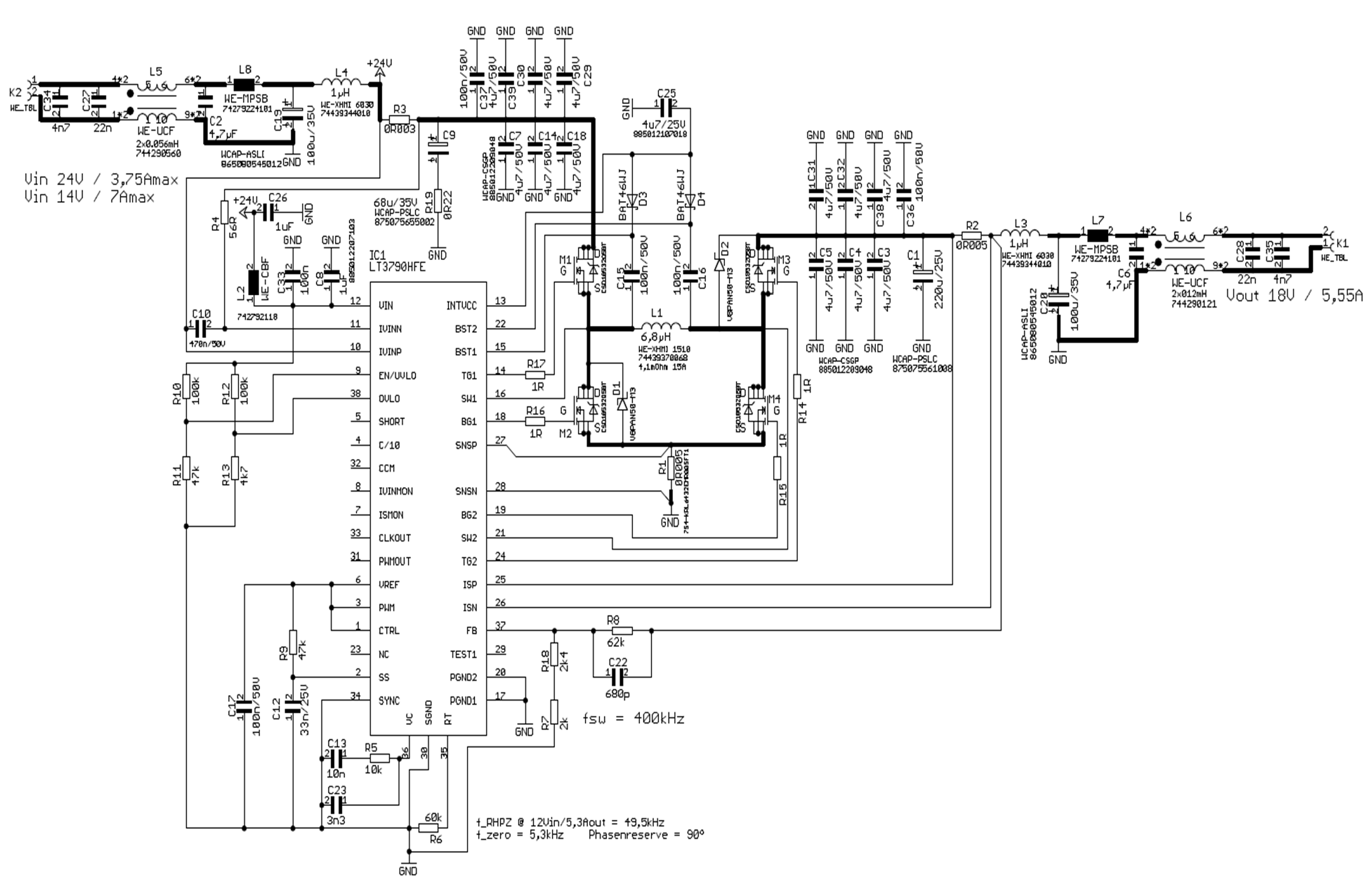

3.4.PCB 顶层布局分析

图8:降压-升压转换器的 EMC 优化顶层布局(省略输入和输出滤波器组)。

1.陶瓷滤波电容器布置紧密,使得高 △l/△t 的输入和输出环路结构非常紧凑。

2.电路中的敏感的、高阻抗的模拟部分的 AGND 覆铜表面分离且顺滑(仅 PIN30 连接到 PGND)。

3.非常靠近开关电源IC的紧凑型自举电路。

4.并联电容的电流测量连接按差分线路布线,采用干净的开尔文连接。

5.通过宽带 π型 滤波器对开关稳压器 IC 的内部电源做去耦滤波

6.为了达到电路板底部和内部PGND层的低电感和低阻抗需使用尽量多的过孔。

7.大面积覆铜可以作为良好的散热片并提供低 RDC,但不得超过必要的面积,特别是在两个“热”△U/△t 开关节点上,以免形成不必要的天线。

3.5.PCB 底层布局分析

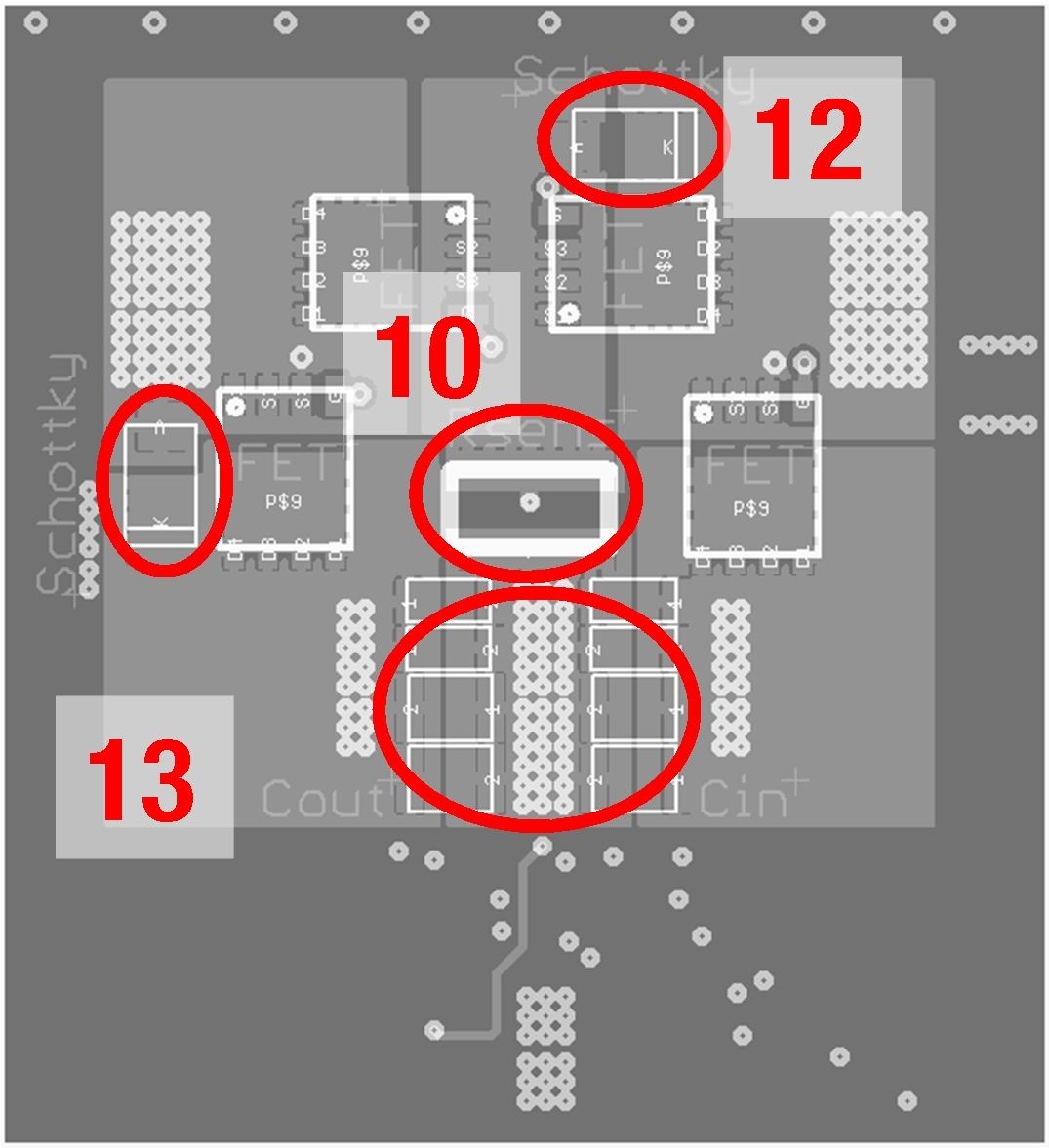

图 9:降压-升压转换器的EMC优化底层布局,包括四个功率MOSFET、剩余的滤波电容器、并联电容和续流二极管。

8.在靠近FET的位置布置陶瓷滤波电容器,使得高△l/△t的输入和输出环路结构非常紧凑。

9.几何形状布局和覆铜表面的使用意味着FET之间以及FET与并联电容之间的连接的阻抗和电感极低。

10.具反向几何形状的电容分流器,可进一步降低寄生电感;因此,HF电流环路也可减至最小。

11.由于没有其它大型器件阻碍热传导,因此PCB底面上的半导体可以得到更好的冷却。

12.超快恢复肖特基二极管紧邻相应的 开关FET布置。

13.大面积覆铜可以作为良好的散热片并提供低RDC,但不得超过必要的面积,特别是在两个“热”△U/△t开关节点上,以免形成不必要的天线。

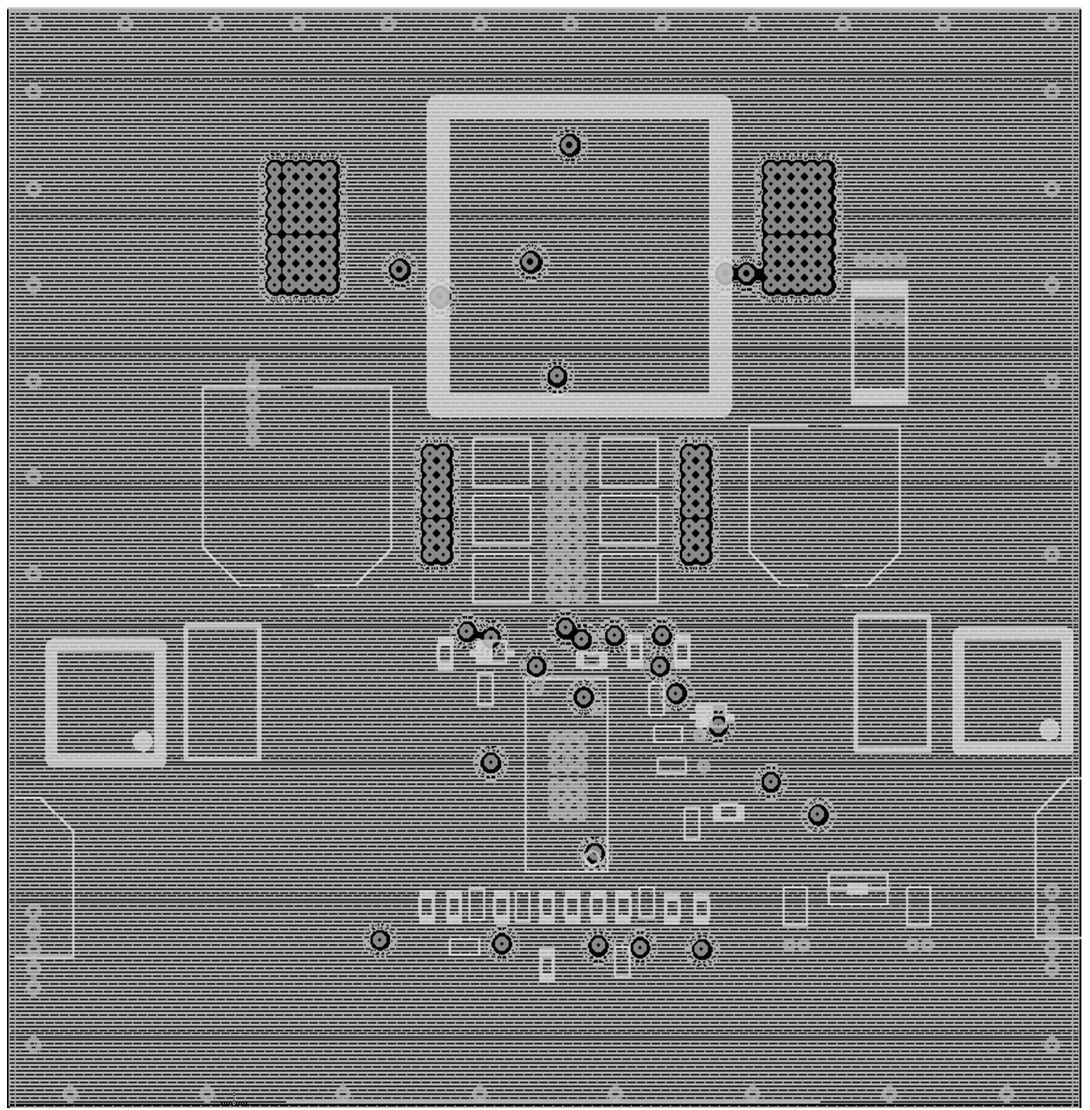

3.6.中间层布局分析

图 10:中间层3的布局。

图 11:中间层2、4、5的布局。

所有四个中间层基本都为PGND覆铜表面,因此具备相应的优点:

热损失分布均匀。

电流馈电和返回路径始终形成尽可能小的环路面积,从而最大限度减少关键EMC环路天线。

一定量的关键EMC高频噪声HF 在PGND表面转换为热量(涡流效应)并因此被吸收。这种效应会随着PGND和HF相关部件之间的距离减小而增加。

部分屏蔽。

MOSFET栅极的引线在两个PGND层内布线,因此可完全屏蔽。

具有GND电位的过孔围绕PGND边缘以规则的间隔布置。这些可以抵消潜在的边缘辐射。

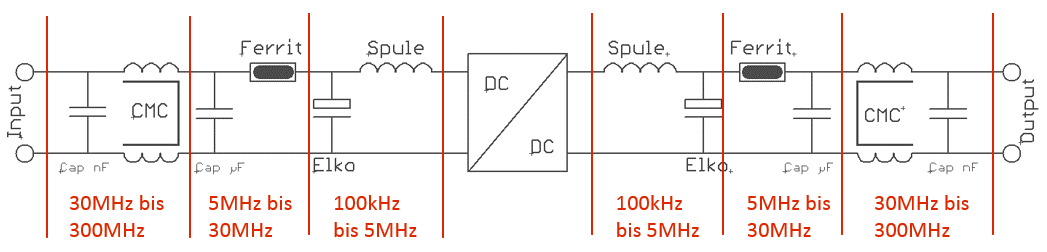

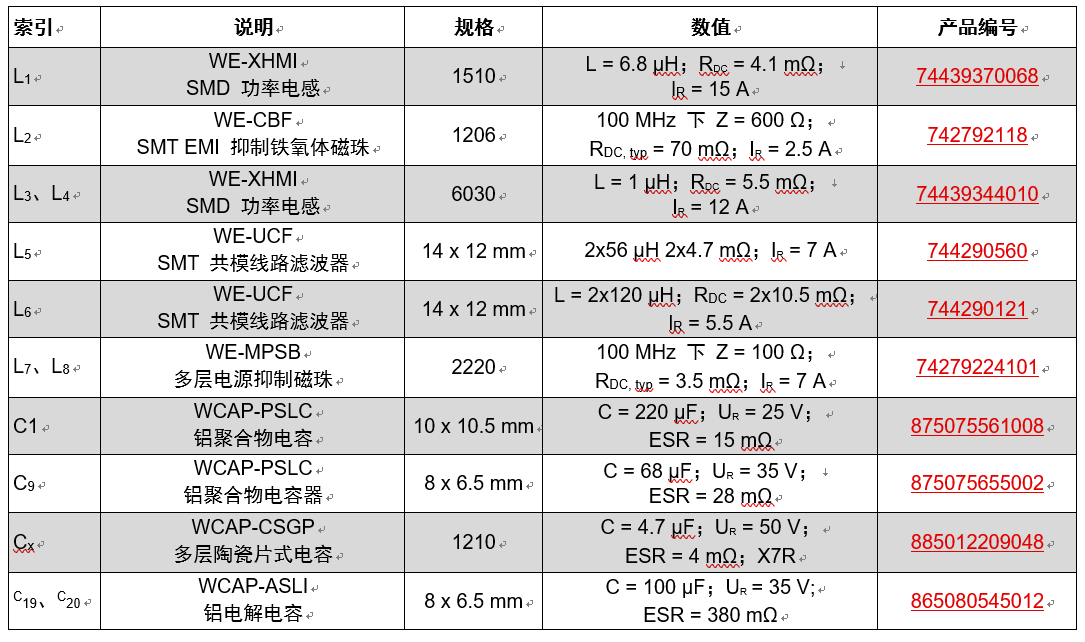

3.7.输入和输出滤波器器件

选择滤波器器件时,必须能够达到150kHz – 300MHz 的宽带干扰抑制。这应足以抑制预期的传导和辐射EMC干扰。但如果输入或输出处使用的线缆被缩短或省略了,则滤波器也可被简化。

3.8.不含滤波器的EMC测量 (100W Pout)

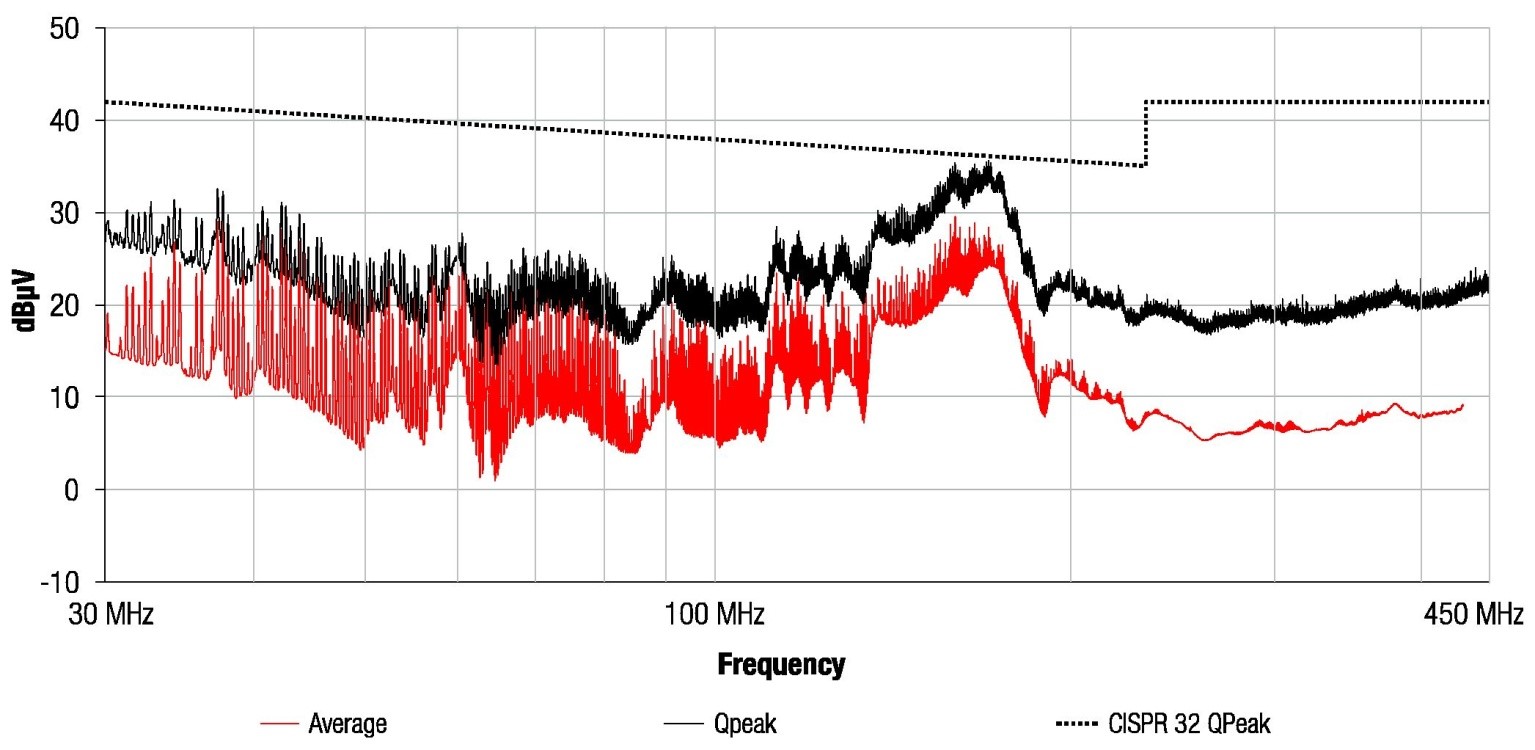

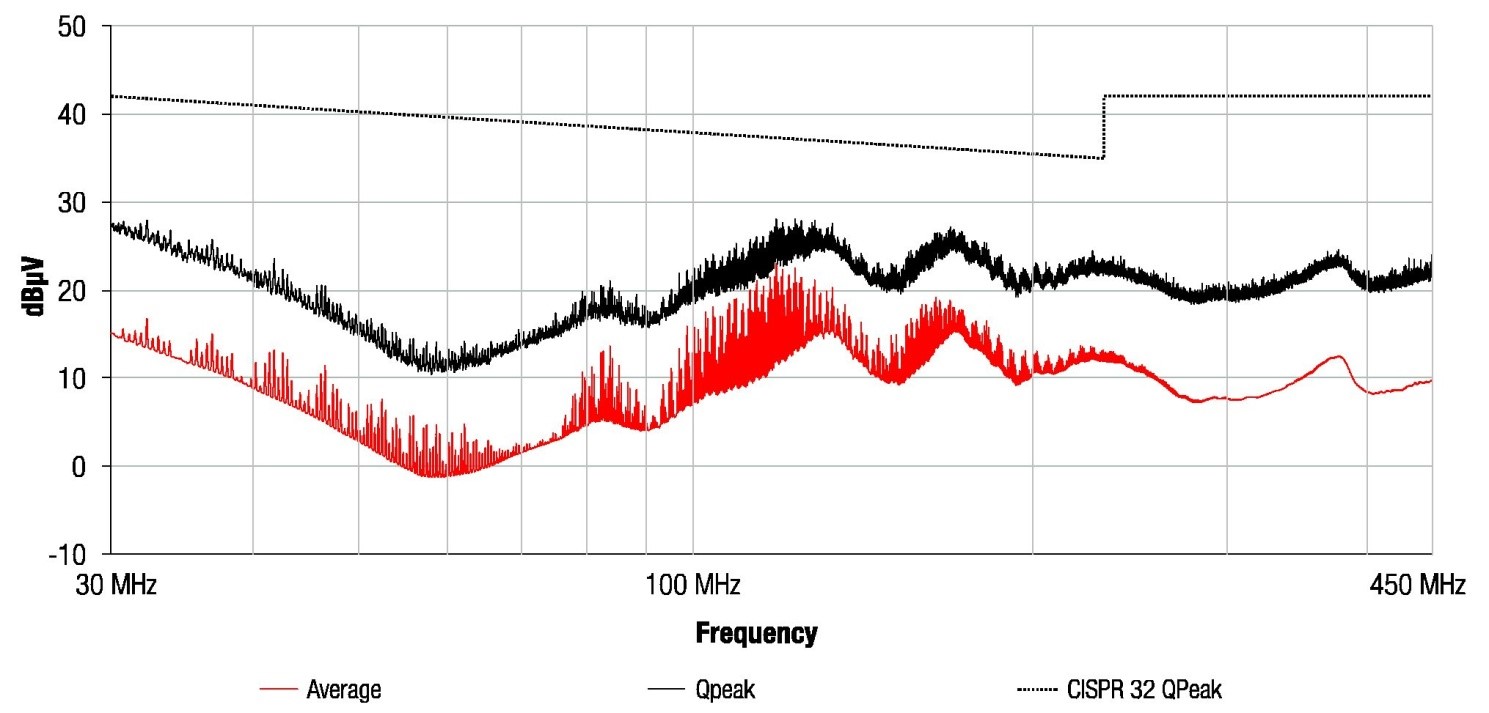

为满足大多数应用的需要,转换器的干扰不得超出Class B (家用)限值,包括传导 (150kHz – 30MHz) 和辐射 (30MHz – 1GHz) 范围,参见图12 和13。

鉴于此处需要的电流,除了插入损耗非常重要之外,电感元件还必须具有尽可能低的RDC,从而将效率和自热保持在一个可接受的水平。遗憾的是,低RDC通常意味着需要增大设计尺寸。因此,使用最先进的元器件在这里也尤为重要,它们可以在RDC、阻抗和尺寸之间达到完美的平衡。WE-MPSB系列以及WE-XHMI系列的紧凑设计特别适合于此案例。廉价的铝电解电容器(如 WCAP-ASLI)适合作为电容值为10μF以上的滤波器的电容器件。与上面提到的刻薄电容器不同,此处不会出现高纹波电流(滤波器电感会有效阻止这些电流),因此它们不需要承受高纹波电流。因此,较高的ESR也不是问题,这甚至还有助于保持低的滤波器系数,从而防止其它不必要的振荡。

图12:不含输入滤波器时的传导干扰测量。果然,尽管布局良好,但干扰超出了B类限值。

图13:不含输入和输出滤波器时的辐射干扰测量。在大约180MHz 下,干扰和限值之间的差异非常小,这可能会导致后续测量出现问题。其原因是肖特基恢复电流的快速反向恢复时间刺激了寄生 LC 谐振。

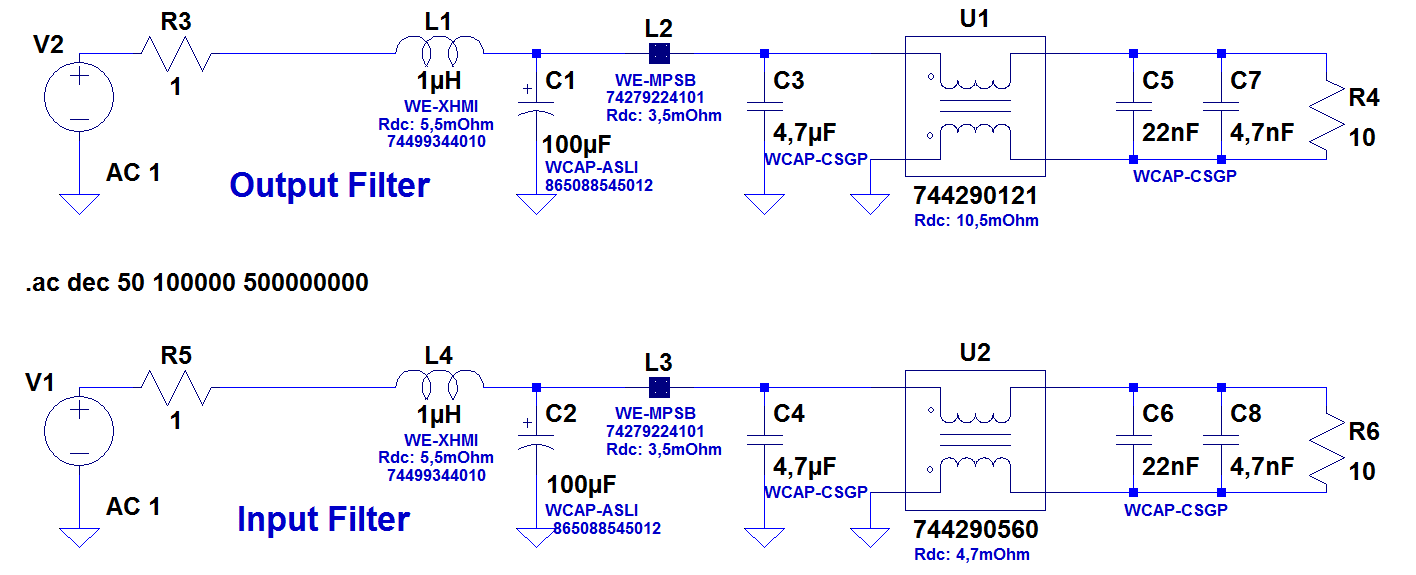

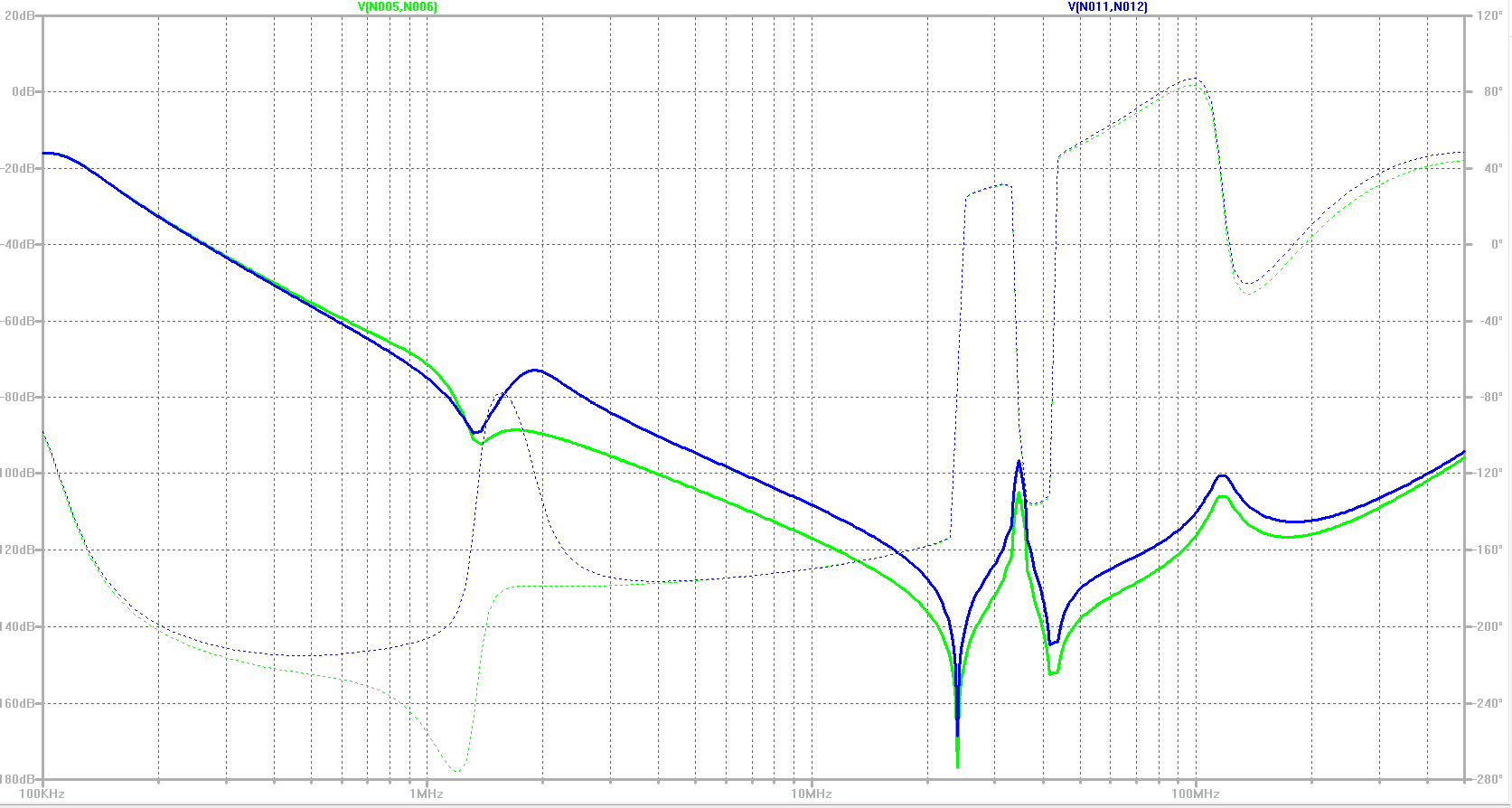

图15 显示了输入和输出滤波器的结构(共模和差模)。图16 显示了该滤波器在EMC相关频率范围内对差模插入阻尼的仿真。

图14:三种不同频率范围的滤波器元件框图。

图15:输入和输出滤波器组差模插入阻尼的LTSpice仿真(仅漏感与CMC相关)。

图16:仿真差模插入衰减与两个滤波器组的寄生特性。最高 500MHz 下,可实现超过80dB的插入损耗。

其它的滤波器损耗由电感器中的欧姆损耗导致:

输出滤波器损耗:I2 • Rdc = 5.5 A2 • 30 mΩ = 907 mW

输入滤波器损耗:|2 • Rdc = 7 A2 • 18.4 mΩ = 902 mW

共模电感的选择标准如下:

在较宽的频率范围内(此案例为150kHz至300MHz)尽可能达到最大共模阻抗。

分段绕组技术,以获尽可能大的漏感(差模干扰抑制)。

低RDC。

紧凑型设计和SMT。

3.9.具输入和输出滤波器的PCB上表面布局分析

1.布置两个滤波器组时,尽可能消除与电路主要部分的电感和电容耦合;否则可能会影响滤波效果。

2.内层中的PGND覆铜表面仅与滤波器的两个铝电解电容器连接。滤波器组下没有覆铜,即便中间层也是如此。这可以避免电流耦合,否则会降低滤波电容器的抑制效果。

图17:使用的两个WE-UCF共模电感的共模和差模阻抗曲线

3.设计T型滤波器时,尽可能消除三个器件内不必要的电容和电感耦合。

4.两个共模电感下方没有覆铜,以便最大限度减少电容耦合

图18:顶层视图,包括符合CISPR32 B类的所有滤波器元件

图 19:顶层测量

3.10. 100 W Pout (Ta = 22 °C)下滤波器的温度和效率测量

100 W Pout 下的效率测量结果:

降压模式 96.5 %

升压模式 95.6 %

元器件的最高温度低于64°C,这为更高的环境温度提供了足够的余量,同时器件上受到的压力也比较低。同样效率也非常高,特别是考虑到这会影响所有过滤器器件。

图20:底层测量

4.总结

尽管具有精细的布局以及合适的有源和无源器件,但此案例中苛刻的规格要求(如长电缆、缺少屏蔽等)意味着如果不额外加装滤波器,就无法符合Class B标准。但是,由于这一问题在意料之中,可以从一开始就设计合适的滤波器。因此,本文档设计了一款灵活、高效且符合B类标准的100W降压-升压转换器。为使电路板更加紧凑,可将两个滤波器组旋转90°或布置在PCB底面。借助如REDEXPERT和LTSpice等设计和仿真软件,可以快速、低成本地得出结果。

图21:含上述输入滤波器时的传导干扰。在整个测量范围内,平均和准峰值干扰均未超出规定限值。

图22:含上述输入和输出滤波器时的辐射干扰。在整个测量范围内,干扰均未超出规定限值(水平和垂直)。

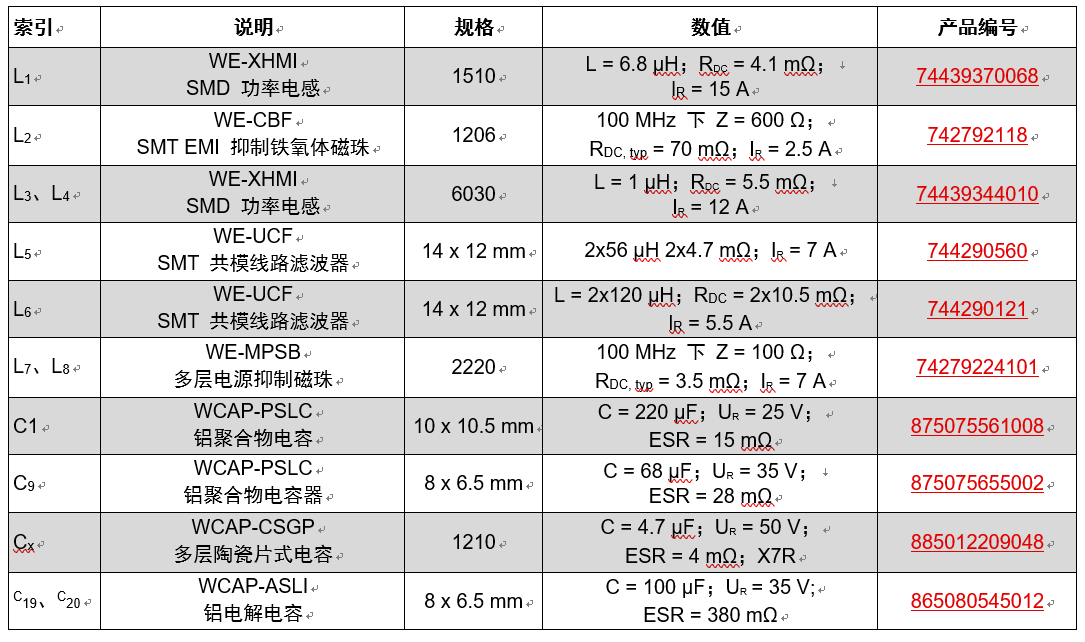

A. 附录

A.1. 物料清单

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SL4016:36V/20A大功率升压DC-DC转换器的核心技术解析2025-09-10 1985

-

助力大功率DC-DC转换器 电池效率提升2023-11-23 1458

-

如何应对USB大功率充电器DC-DC转换器的开关噪声?2023-05-04 2340

-

如何使用SiC功率模块改进DC/DC转换器设计?2023-02-20 8378

-

FP5207非同步DC-DC升压转换器,外置MOS大功率升压芯片2022-12-16 3058

-

DC-DC电源转换器/基准电压源介绍2021-10-28 1902

-

LT1305:带低电池检测器的微功率大功率DC/DC转换器数据表2021-05-21 1019

-

LTC3105:具有最大功率点控制和250 mV启动数据表的400 mA升压式DC/DC转换器2021-04-30 840

-

具最大功率点控制功能和 250mV 启动电压的400mA 同步升压型 DC/DC 转换器适合能量收集应用2021-03-21 911

-

XL4016 大功率降压型DC-DC转换器2020-05-18 3917

-

用Maxi、Mini和Mincro系列DC-DC转换器设计大功率2016-06-02 967

-

使用Maxi、Mini和Mincro系列DC-DC转换器设计大功2016-05-24 1108

-

使用Maxi、Mini和Mincro系列DC-DC转换器设计大功率阵列2016-01-06 1096

-

MAX1708 大功率、升压型DC-DC转换器2011-01-11 2511

全部0条评论

快来发表一下你的评论吧 !