国际大厂们之间的“3D堆叠大战”

电子说

描述

可以不必理会“摩尔定律”是否会失效的争议,但业界多年来一直在追求提升半导体工艺不断降低线宽,而线宽的微缩总是有一个极限的,到了某种程度,因为难度太大,就没了经济效应。许多半导体公司,已经调整了应对这新困难的战略,目前3D堆叠芯片技术备受业界关注。 从世界第一款CPU诞生开始到今天,甚至包括摩尔定律本身,都是在二维层面展开的,也就是说,大家的研究重点都放在如何实现单位面积上元器件数量的增加以及微观精度的改进,但也有不少大厂开始提出3D堆叠的概念,把一块芯片从二维展开至三维。 国际大厂们之间的“3D堆叠大战” 在去年4月的美国加州圣塔克拉拉(Santa Clara)第二十四届年度技术研讨会上,台积电首度对外界公布创新的系统整合单芯片(SoIC)多芯片3D堆叠技术。这在当时被誉为可再次把三星狠狠甩在后头、实现3D IC的高阶封装技术。 SoIC技术是采用硅穿孔(TSV)技术,可以达到无凸起的键合结构,可以把很多不同性质的临近芯片整合在一起,而且当中最关键、最神秘之处,就在于接合的材料,号称是价值高达十亿美元的机密材料,因此能直接透过微小的孔隙沟通多层的芯片,达成在相同的体积增加多倍以上的性能。

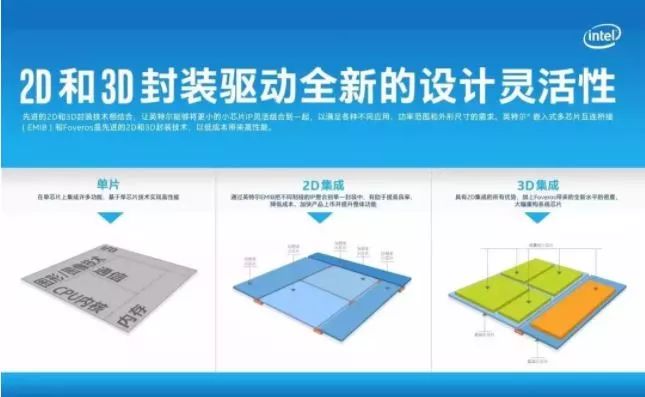

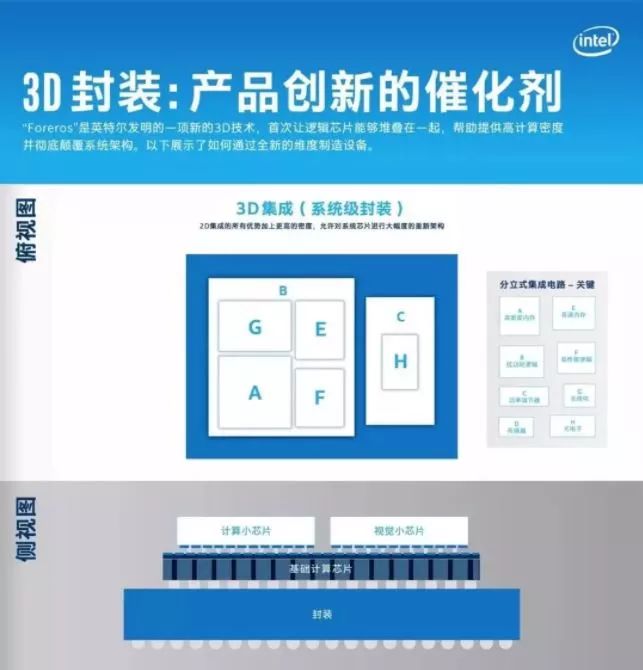

据了解,SoIC是基于台积电的CoWoS(Chip on wafer on Substrate)与多晶圆堆叠(WoW)封装技术开发的新一代创新封装技术,未来将应用于十纳米及以下的先进制程进行晶圆级的键合技术,被视为进一步强化台积电先进纳米制程竞争力的利器。2018年10月,台积电在第三季法说会上,已针对万众瞩目的SoIC技术给出明确量产时间,预期2020年开始挹注台积电的营收贡献,至2021年将会大量生产。 而三星作为台积电的老对头,在先进封装上自然不甘示弱。针对2.5D封装,三星推出了可与台积电CoWoS封装制程相抗衡的I-Cube封装制程,在2018年三星晶圆代工论坛日本会议上,三星公布了其封测领域的路线图,就2.5D/3D封装上来说,三星已经可以提供I-Cube 2.5D封装,今年将会推出3D SiP系统级封装,其中I-Cube 封装已经可以实现4路HBM 2显存堆栈。 困于10nm的Intel也在这方面寻找新的机会,其在去年年底的“架构日”活动中,推出其业界首创的3D逻辑芯片封装技术——Foveros,Foveros首次引入3D堆叠的优势,可实现在逻辑芯片上堆叠逻辑芯片。所以,“Foveros”逻辑芯片3D堆叠实际上并不是一种芯片,而是称之为逻辑晶圆3D堆叠技术。 下面两张图对这项技术作了详细介绍。第一张图展示了Foveros如何与英特尔嵌入式多芯片互连桥接(EMIB)2D封装技术相结合,将不同类型的小芯片IP灵活组合在一起,第二张图则分别从俯视和侧视的角度透视了“Foveros” 3D封装技术。

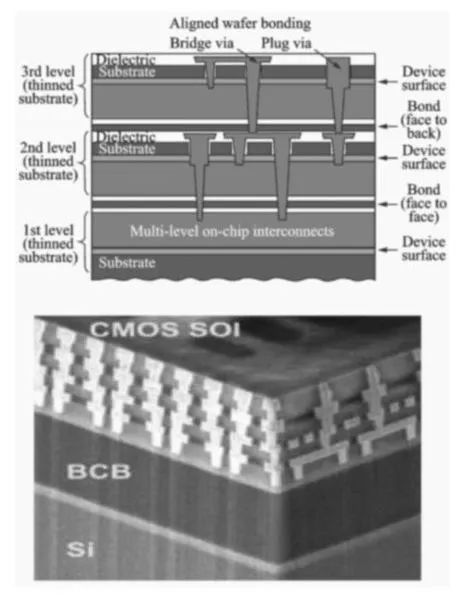

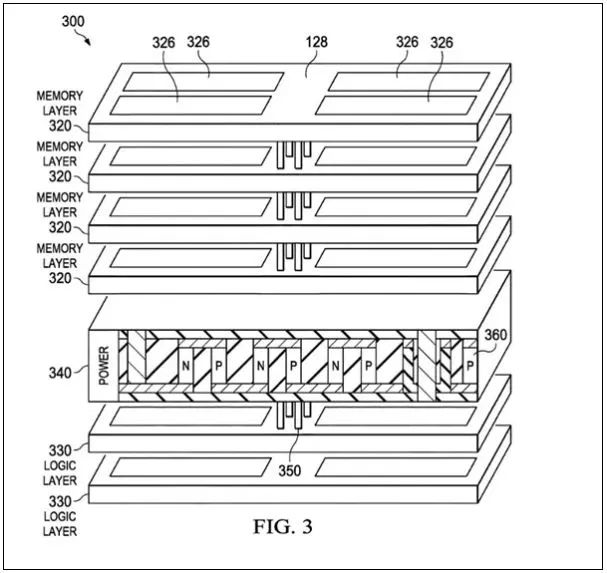

该技术有望首次将晶圆的堆叠从传统的无源中间互连层和堆叠存储芯片扩展到CPU、GPU和AI处理器等高性能逻辑晶圆,为整合高性能、高密度和低功耗矽制程技术的零件和系统铺平了道路。设计人员可在新的产品形态中“混搭”不同的技术专利模组与各种存储芯片和I/O配置。并使得产品能够分解成更小的“经畔组合”,其中I/O、SRAM和电源传输电路可以整合在基础晶圆中,而高性能逻辑“晶圆组合”则堆叠在顶部。 英特尔的老对手AMD在今年3月的活动中透露,他们正致力于在其处理器之上使用3D堆叠DRAM和SRAM的新设计来提高性能。AMD的3D堆叠技术,角度与英特尔的略有不同。此前AMD已经将HBM2内存堆叠在其GPU核心旁边,这意味着内存芯片与处理器位于同一个封装中,这还仅仅属于2.5D方案。但该公司计划在不久的将来转向真正的3D堆叠。AMD正致力于在CPU和GPU之上直接堆叠SRAM和DRAM内存,以提供更高的带宽和性能。 3D堆叠的好处在于缩短了电流传递路径,也就是会降低功耗。不过,3D封装的挑战在于如何控制发热。遗憾的是,AMD并未公布更多技术细节。 格芯于近日宣布推出适用于高性能计算应用的高密度3D堆叠测试芯片,该芯片采用格芯 12nm Leading-Performance (12LP) FinFET 工艺制造,运用Arm 3D 网状互连技术,核心间数据通路更为直接,可降低延迟,提升数据传输率,满足数据中心、边缘计算和高端消费电子应用的需求。此外,两家公司还验证了一种3D可测试性设计(DFT)方法,使用格芯的晶圆与晶圆之间的混合键合,每平方毫米可连接多达100万个3D连接,拓展了12nm设计在未来的应用。 去年年底有报道称英伟达针对AI打造的Volta微处理器的运作也运用3D堆叠技术。通过直接在GPU上面堆叠八层的高频宽存储器,这些芯片在处理效率上创造了新的记录。 还有三星研发的全新的三层堆栈式传感器,每秒可拍摄多达1000张照片,几乎达到了专业摄影机的水准。它在现有大部分CMOS传感器都只有两层的基础上额外加入DRAM,成为实现超高速拍摄的关键。这一技术也将为传感器技术的升级换代带来全新的张力。 由此可见,3D芯片堆叠技术的应用前景广阔。 中国本土有哪些企业加入“3D堆叠大战”? 3D芯片堆叠技术之战正在国际大厂间如火如荼地进行着,中国本土企业也在开始追赶这一热潮。 去年12月3日,武汉新芯对外宣布称,基于其三维集成技术平台的三片晶圆堆叠技术研发成功。此次武汉新芯的晶圆级集成技术可将三片不同功能的晶圆(如逻辑、存储和传感器等)垂直键合,在不同晶圆金属层之间实现电性互连。 武汉新芯早在2012年开始布局三维集成技术,并于2013年成功将三维集成技术应用于背照式影像传感器,良率高达99%,随后陆续推出硅通孔(TSV)堆叠技术、混合键合(Hybrid Bonding)技术和多片晶圆堆叠技术。 今年6月25日,在川商发展大会开幕前夕,紫光集团联席总裁王慧轩表示,四川成为紫光战略性基地,正建设3D堆叠存储芯片工厂。第一期建成之后,将月产10万片,三期都完成后将拥有月产30万片的一个生产能力。 如今,晶方科技是3DIC和TSV晶圆级芯片尺寸封装和测试服务的全球领先供应商。在12英寸3D TSV工艺、12寸异质晶圆三维集成封装技术、汽车及工业制造智能传感器高可靠性封装工艺等多个领域取得创新突破。 硕贝德,其3D先进封装技术目前主要用于COMSSensor芯片封装(WLCSP(晶圆级芯片封装)+TSV(硅通孔技术)技术),未来在MEMS芯片和多芯片内存芯片等封装领域具有广阔前景。但封装不会成为他们核心的业务,会根据客户需求,保持持续稳定的发展,不会有大量固定资产投入。 3D芯片堆叠技术到底是什么? 既然3D芯片堆叠技术有如此之大魅力,它将存储、逻辑、传感器于一体,能够缩小尺寸且提供性能,可以说是朝摩尔定律的方向迈进了一步。那么问题来了,3D芯片堆叠技术到底是什么? 与传统的二维芯片把所有的模块放在平面层相比,三维芯片允许多层堆叠,而过TSV用来提供多个晶片垂直方向的通信。其中,TSV是3D芯片堆叠技术的关键。

3D芯片堆叠结构示意图 3D堆叠技术是把不同功能的芯片或结构,通过堆叠技术或过孔互连等微机械加工技术,使其在Z轴方向上形成立体集成、信号连通及圆片级、芯片级、硅帽封装等封装和可靠性技术为目标的三维立体堆叠加工技术。该技术用于微系统集成,是继片上系统(SOC)、多芯片模块(MCM)之后发展起来的系统级封装的先进制造技术。 从SiP系统级封装的传统意义上来讲,凡是有芯片堆叠的都可以称之为3D,因为在Z轴上有了功能和信号的延伸,无论此堆叠是位于IC内部还是IC外部。目前,3D芯片技术的类别分别为以下几类: 1.基于芯片堆叠式的3D技术 3D IC的初期型态,目前仍广泛应用于SiP领域,是将功能相同的裸芯片从下至上堆在一起,形成3D堆叠,再由两侧的键合线连接,最后以系统级封装(System-in-Package,SiP)的外观呈现。堆叠的方式可为金字塔形、悬臂形、并排堆叠等多种方式,参看下图。

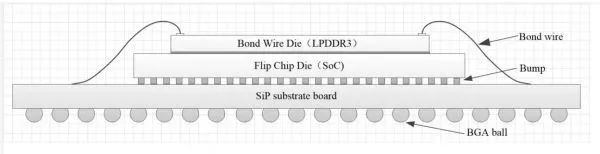

另一种常见的方式是将一颗倒装焊(flip-chip)裸芯片安装在SiP基板上,另外一颗裸芯片以键合的方式安装在其上方,如下图所示,这种3D解决方案在手机中比较常用。

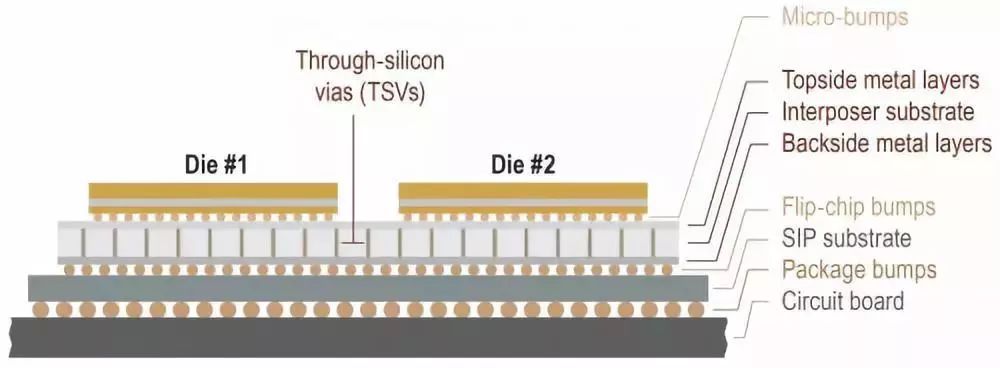

2.基于有源TSV的3D技术 在这种3D集成技术中,至少有一颗裸芯片与另一颗裸芯片叠放在一起,下方的那颗裸芯片是采用TSV技术,通过TSV让上方的裸芯片与下方裸芯片、SiP基板通讯。如下图所示:

下图显示了无源TSV和有源TSV分别对应的2.5D和3D技术。

以上的技术都是指在芯片工艺制作完成后,再进行堆叠形成3D,其实并不能称为真正的3D IC 技术。这些手段基本都是在封装阶段进行,我们可以称之为3D集成、3D封装或者3D SiP技术。 3.基于无源TSV的3D技术 在SiP基板与裸芯片之间放置一个中介层(interposer)硅基板,中介层具备硅通孔(TSV),通过TSV连结硅基板上方与下方表面的金属层。有人将这种技术称为2.5D,因为作为中介层的硅基板是无源被动元件,TSV硅通孔并没有打在芯片本身上。如下图所示:

4.基于芯片制造的3D技术

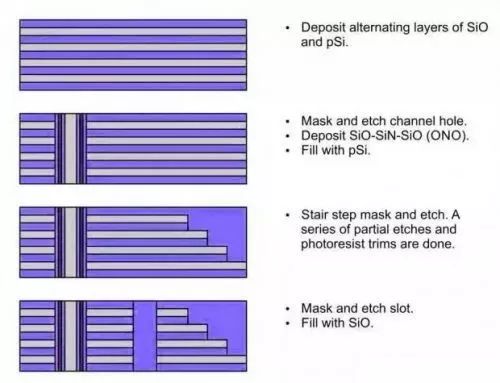

目前,基于芯片制造的3D技术主要应用于3D NAND FLASH上。东芝和三星在 3D NAND 上的开拓性工作带来了两大主要的 3D NAND 技术。3D NAND目前已经能做到64层甚至更高,其产量正在超越 2D NAND。 东芝开发了Bit Cost Scalable(BiCS)的工艺。BiCS工艺采用了一种先栅极方法(gate-first approach),这是通过交替沉积氧化物(SiO)层和多晶硅(pSi)层实现的。然后在这个层堆叠中形成一个通道孔,并填充氧化物-氮化物-氧化物(ONO)和 pSi。然后沉积光刻胶,通过一个连续的蚀刻流程,光刻胶修整并蚀刻出一个阶梯,形成互连。最后再蚀刻出一个槽并填充氧化物。如下图所示:

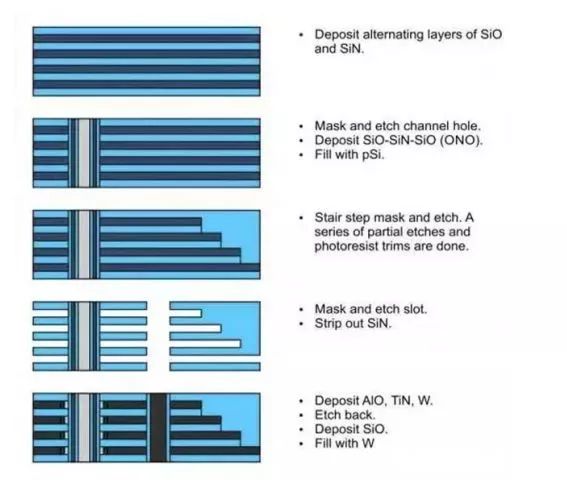

三星则开发了Terabit Cell Array Transistor (TCAT)工艺。TCAT是一种后栅极方法(gate-last approach),其沉积的是交替的氧化物和氮化物层。然后形成一个穿过这些层的通道并填充ONO和pSi。然后与BiCS工艺类似形成阶梯。最后,蚀刻一个穿过这些层的槽并去除其中的氮化物,然后沉积氧化铝(AlO)、氮化钛(TiN)和钨(W)又对其进行回蚀(etch back),最后用坞填充这个槽。如下图所示:

如何解决“3D堆叠”的散热问题? “3D堆叠”随着堆叠元器件的增多,集中的热量如何有效散出去也成了大问题。 目前AMD计划在3D堆栈的内存或逻辑芯片中间插入一个热电效应散热模块(TEC),原理是利用帕尔贴效应(Peltier Effect)。按照AMD的描述,利用帕尔贴效应,位于热电偶上方和下方的上下内存/逻辑芯片,不管哪一个温度更高,都可以利用热电偶将热量吸走,转向温度更低的一侧,进而排走。

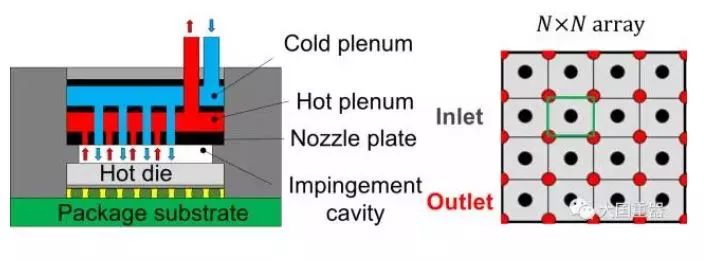

不过也有不少问题AMD没有解释清楚,比如会不会导致上下的元器件温度都比较高?热电偶本身也会耗电发热又如何处理? 在美国国防先进研究计划局资助下,IBM去年研究出嵌入式散热方式解决3D堆叠芯片散热问题。 芯片嵌入式冷却技术通过将热提取电介质流体(如制冷系统中使用的电介质流体)泵入微小间隙中,不超过一根头发直径(?100μm)级别的堆栈。所使用的介电流体可以与电连接接触,因此不限于芯片或堆栈的一部分。该方案非常有利于芯片堆栈的散热,例如将存储器和加速器芯片置于堆栈中的高功率芯片之上,这可以提高从图形渲染到深度学习算法的各种速度。 其实,早在2017年的IEDM大会上,比利时微电子研究中心(IMEC)宣布针对高性能计算系统首次实现了基于冲击射流冷却的高效率、低成本散热技术。主要面向散热问题日益突出的3D堆叠高性能计算系统(High performance computation,HPC)。其散热性能达到0.15cm2K/W, 同时散热系统的泵功率可以降低到0.4W。

-

3D战火延烧台湾 电视大厂正面交锋抢占制高点2010-03-30 766

-

TSMC 和 Cadence 合作开发3D-IC参考流程以实现真正的3D堆叠2013-09-26 1821

-

半导体产业的未来:3D堆叠封装技术2016-06-10 2834

-

在3D NAND新产品技术进入市场之际加快发展步伐2018-06-20 5332

-

3D NAND flash大战开打 三星独霸局面打破2018-12-13 1396

-

英特尔为你解说“Foveros”逻辑芯片3D堆叠技术2018-12-14 9122

-

什么是3D芯片堆叠技术3D芯片堆叠技术的发展历程和详细资料简介2018-12-31 34500

-

2.5D异构和3D晶圆级堆叠正在重塑封装产业2019-02-15 8462

-

3D堆叠技术的诱因资料下载2021-03-31 1553

-

AMD 3D堆叠缓存提升不俗,其他厂商为何不效仿?2022-04-13 7933

-

什么是3D NAND闪存?2023-03-30 4733

-

浅谈400层以上堆叠的3D NAND的技术2023-06-15 3344

-

三星将推出GDDR7产品及280层堆叠的3D QLC NAND技术2024-02-01 1513

-

3D堆叠像素探测器芯片技术详解(72页PPT)2024-11-01 4689

-

3D堆叠发展过程中面临的挑战2024-09-19 2623

全部0条评论

快来发表一下你的评论吧 !