一种基于FPGA的多路视频通道控制系统设计总体分析

可编程逻辑

描述

视频监控以其直观、方便、信息内容丰富而广泛应用于很多场合。视频监控成为人们生活中不可缺少的技术。在一些危险场所,用视频监控代替人工监视,可以保证人们的生命安全。鉴于一路视频的视野范围有限,要充分收集目标的信息,就需要有多路视频来对同一个物体在不同方位进行监控。因此需要有一个良好的控制手段,确保多路视频控制稳定,可靠。针对织布机告警系统的需求,提出一种基于FPGA的多路视频通道控制系统,本系统设计利用FPGA间接控制2块MAX4312选通所需要的视频通道,实现各个视频通道间相互切换。根据开关控制信号的设计思想在FPGA中对拨动开关输进信号做往抖动处理,然后对不同的开关操纵进行编码,最后将信号送给DSP进行处理。

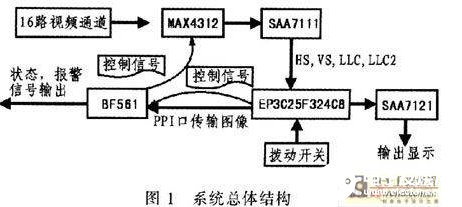

l 系统总体结构

系统总体结构如图1所示。在1台产业织布机上安装了16个CCD图像传感器对布匹进行图像监控,通过2片MAX4312选择16路图像视频信号中的一路,经可编程视频输进器件SAA7111处理后从VP0输出数字图像信号。同时SAA7111输出相应的行、场同步信号HS,VS以及与HS锁定的时钟信号LLC、LLC2,利用这些信号在EP3C25F324C8中对图像进行预处理。然后将处理后的图像通过PPI口送给BF561中进行算法处理,最后将处理结果送给报警和状态指示装置,实现织布机告警功能。为了使图像监控更方便,该系统设计增添了电平拨动开关和脉冲拨动开关。电平开关使输进图像停止切换,固定于其中一路视频输人图像。脉冲开关可以左右拨动,每次向左或向右拨动都会产生一个很短的上升沿脉冲,同时图像向前或向后进行切换,实现手动选择视频输进通道的功能。

2 软件模块设计

2.1 开关控制信号

实际工程中,BF56l连接在FPGA上的PF引脚比较少。为了节约资源,只通过BF561中的BF9来识别2个拨动开关的动作。因此首先需要将2个拨动开关输进信号在FPGA中进行处理整合,得到合适的信号。

本系统开关控制信号的设计思想:由于设计这个信号的目的是识别开关控制动作。因此,只要任何一个开关发生了动作就需要产生一个脉冲。假如只有脉冲信号就只能知道开关发生了动作,而不知道是哪个开关发生了什么动作。所以,要识别具体是哪个开关发生了什么动作就必须配合双口RAM中的数据进行解码。该系统设计的脉冲持续时间对BF561来说并不重要,只要BF561能识别这个脉冲即可。由于系统中的2个拨动开关,一个是电平拨动开关,另一个是脉冲拨动开关,因此,只要根据电平拨动开关的动作制作相应的脉冲信号,再用这个信号与脉冲拨动开关产生的原始信号逻辑相与,就能得到所需要的目的信号。

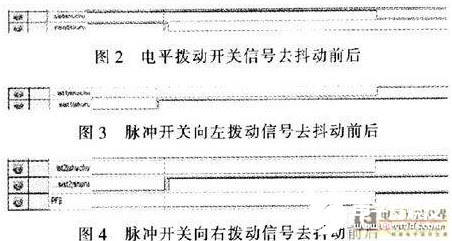

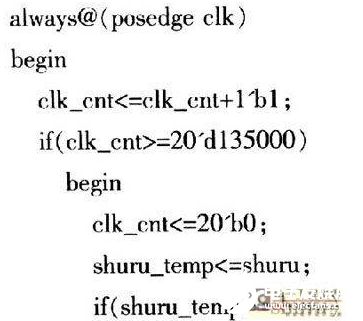

由于拨动开关是机械触点,当其断开、闭合时会有相应的前沿、后沿抖动,为了使每次动作都只做一次响应,就必须对原始开关信号做往抖动处理。抖动信号可以分为2种:一种是时间很短的干扰信号,如高频毛刺;另一种是时间较长的干扰信号,如开关抖动。这里的拨动开关都是人为操纵,因此每次触发的时间都不会很短,一般小于10 Hz。根据上述分析开关抖动信号属于后一种。因此在每次开关操纵后,对其产生的信号进行连续采样,假如每次采样都是低电平或者都是高电平,就以为此信号不是抖动,确实开关状态发生了变化。整个设计过程使用Verilog硬件描述语言编写,然后在QuartusⅡ平台上编译,并采用SignalTapⅡLogic Arlalvzer对信号采样分析,调试通过后连同其他程序一起烧写进FPGA的配置器件EPCSl6中。图2~图4分别是各个开关动作往抖动前和往抖动后的实时信号采样图。往抖动模块中的部分代码如下:

其中,clk为13.5 MHz频率的时钟信号,clk_cnt为采样时间间隔计数器,当clk_cnt为135 000时采样1次,即每隔10 ms采样1次。寄存器shuru_temp存储前一次开关信号状态,shum存储当前开关信号状态。假如shuru_temp的值即是shtlm的值,则计数器test_cnt自动加l。假如连续4次采样值相等,即test_cnt=4时往抖动输出才随输进变化。

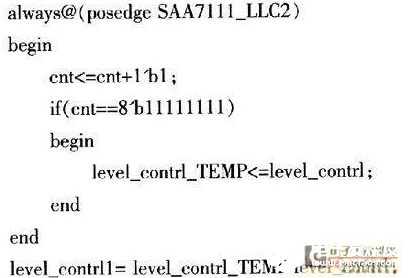

用电平拨动开关信号作为输进,制作了一个脉冲信号用于识别开关动作,其代码如下:

代码中寄存器level_contrl_TEMP存储level_contrl延时256个时钟周期后的信号,然后用level_eontrl_TEMP中存储的信号与level_co-ntrl的值相异或产生所需要的脉冲信号。

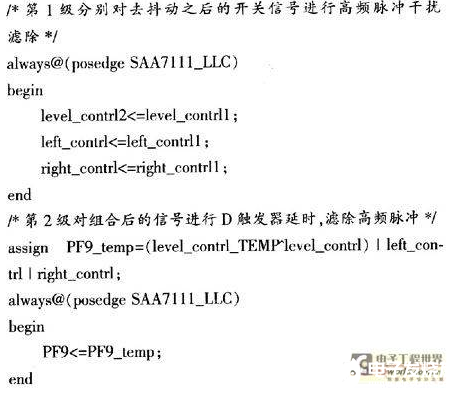

调试中发现,往抖动后的信号经常混有持续时间很短的高频脉冲干扰信号,因此设计中使用两级D触发器延时来彻底消除高频脉冲干扰,其程序代码如下:

2.2 双口RAM及开关信号编码设计

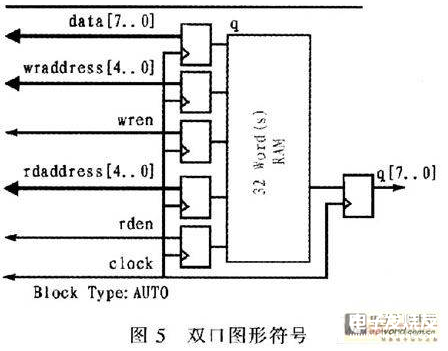

双口RAM分为真、假2种双口。真双口2个端口都可以读写,互不干扰。本次设计根据实际需要,添加的RAM模块一端只读,另一端只写,读写互不干扰。根据上述分析可知,开关控制信号只能知道有开关控制动作发生,但是不能识别具体哪个开关发生了动作。因此,设计中首先利用MegaWizardPlug_In Manager中的宏功能块RAM:2_PORT产生1个双口RAM存储块,然后对这个宏功能模块的参数进行适当调整,产生一个满足自己特定要求的模块,如图5所示。

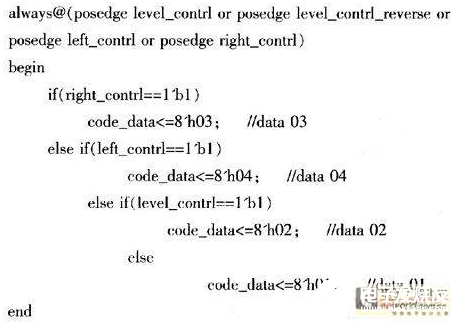

设计过程中,首先将开关动作进行编码。然后将编码后的数据存进空间大小为8的双口RAM中。当BF561检测到PF9上的脉冲后,在PF中断中读取RAM中指定地址的数据,然后根据这个数据进行开关状态解码并按解码后的控制信息对2块MAX4312器件进行操纵以控制视频通道。对开关动作进行的编码程序代码如下:

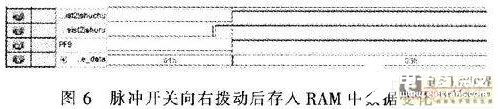

整个设计有4种开关动作,程序中分别将其编码成数据0l、02、03、04,然后将编码后的这4个数据存进双口模块中,等待BF561来读取并进行解码。图6是SignalTapⅡLogic Analyzer中对脉冲开关向右拨动后存进RAM中的数据进行采样。

程序中RAM的读信号rden_signal是由DSP发送的地址信号DSP_A、BANK选择信号DSP_AMSl以及DSP读信号DSP_ARE进行控制的。当DSP不从双口读取数据时,必须给DSP的数据线赋值高阻,以免影响SDRAM对DSP数据线的操纵。赋值指令如下:assignDSP_D=(rden_signal=l'b1)?DSP_D_TEMP;8 'hzz;其中DSP_D_TEMP是从双口中读取的数据。

3 结论

首先先容了整个系统的产业背景和硬件架构,然后着重阐述了怎样在FPGA中处理开关控制信号,以达到可靠响应每个开关动作的目的。整个设计程序是在QuartusⅡ平台上用Verilog硬件描述语言编写,利用QuartusⅡ中的下载工具和SignalTapⅡLogic Analyzer工具进行下载、实时采样,并多次调试验证。本次设计已经成功应用于布机告警系统中,每次拨动开关都能正确、可靠的切换视频通道。固然此系统中只有两种开关,但是整个程序的设计思想对多种开关控制也是通用的,只需在细节上稍作改变就能识别多种开关动作。

-

一种新型的电梯门机控制系统2009-10-06 8867

-

基于DSP+FPGA多视频通道的切换控2012-12-12 3333

-

一种基于MODBUS协议的工业控制系统设计2018-10-16 2385

-

一种基于DSP+FPGA的多通道视频监控系统设计2019-06-24 1674

-

一种基于FPGA的多通道频率测量系统的实现方法介绍2019-06-27 1852

-

基于FPGA的多路视频通道控制系统该怎么设计?2019-09-04 2726

-

基于FPGA怎么实现各个视频通道间相互切换?2019-10-17 2887

-

分享一种不错的基于FPGA的多路视频通道控制系统设计2021-04-29 986

-

介绍一种基于FPGA的电机控制系统2022-02-17 1043

-

一种基于DSP+FPGA的控制系统方案设计2009-12-22 1176

-

基于FPGA的多路视频合成系统的设计2012-09-12 1227

-

一种基于DSP_FPGA的辅助逆变器核心控制系统_吴瑕杰2017-01-08 796

-

一种基于FPGA的高速多路视频数据采集系统设计详解2019-02-11 2669

-

如何使用FPGA和ARM设计和实现多路视频采集系统2019-11-19 1645

-

一种基于FPGA-的步进电机控制系统的设计2022-06-23 855

全部0条评论

快来发表一下你的评论吧 !