基于IAP流程的两片Flash拼接的Flash控制器方案设计

控制/MCU

描述

0 引言

随着智能化的发展以及物联网的兴起,微控制器(Micro Control Unit,MCU)主控芯片得到了越来越多的应用。当前MCU主控芯片一般都用NOR Flash作为片上系统存储器,进行指令和数据存取,根据应用,用户可以对片上Flash的指定区域进行擦写。在工业电力控制的应用中,在线升级(In Application Programming,IAP)是一种常用的操作,意思是“在应用编程”,即在程序运行时,程序存储器可由程序自身进行擦写。具体来说,就是将片上Flash存储器分为bootloader(IAP)程序和USER APP程序两部分,当需要在线升级时,bootloader中的IAP程序通过外部通信接口接收数据,然后擦除和写入USER APP部分,同时写入更新标志,然后系统重新启动执行USER APP程序,达到在线升级的目的。

通常有些主控芯片会要求IAP程序调用的Flash擦写程序要在SRAM中执行,IAP程序到USER APP程序跳转需要进行中断向量表重映射。擦写Flash USER APP程序区域过程中,要求CPU不能对Flash发起读操作,如果发生,则不能正确返回读取结果。

本文给出了一种支持IAP流程的两片Flash拼接的Flash控制器方案,IAP程序直接在Flash执行,IAP程序到USER APP程序跳转提供一种快速方法,通过硬件直接完成地址映射。IAP程序执行过程中,CPU可以对Flash发起读指令操作,擦写结束能正确返回读结果。

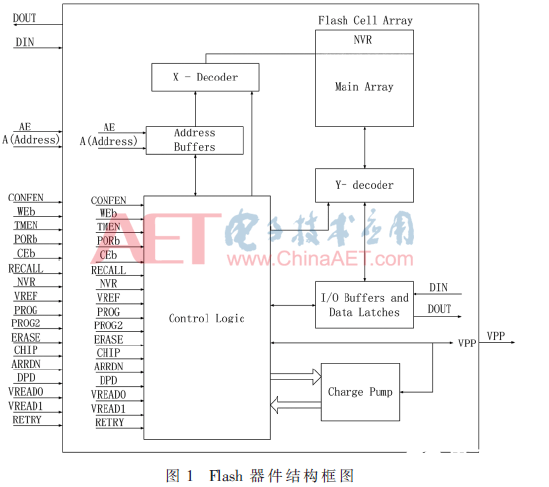

1 NOR Flash器件

本文采用的NOR Flash IP基于UMC55 nm工艺,型号是UM055EFLLP128KX032CBA,读写位宽32 bit,地址线17 bit。main区总容量4 Mb(1 K×128×32 bit),1 K个扇区;NVR区总容量16 Kb(4×128×32 bit),4个扇区。每个扇区容量为128×32 bit=4 Kb,每个扇区包含2个页,每个页包含64个word(1个word为32 bit)。结构框图如图1所示。

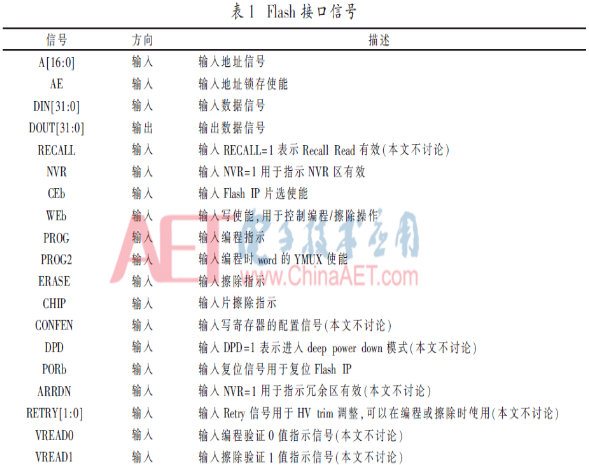

Flash接口信号如表1所示。

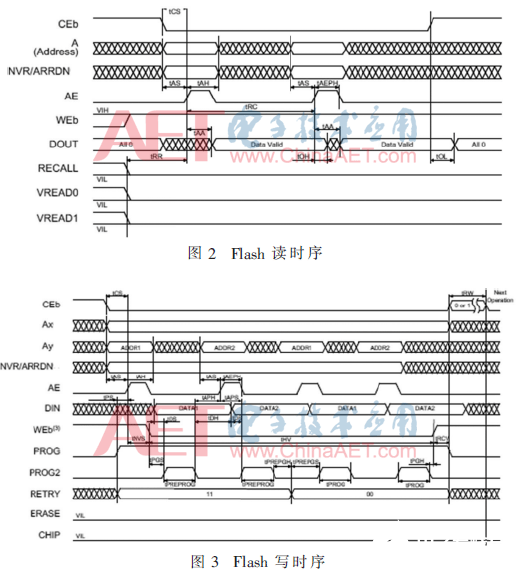

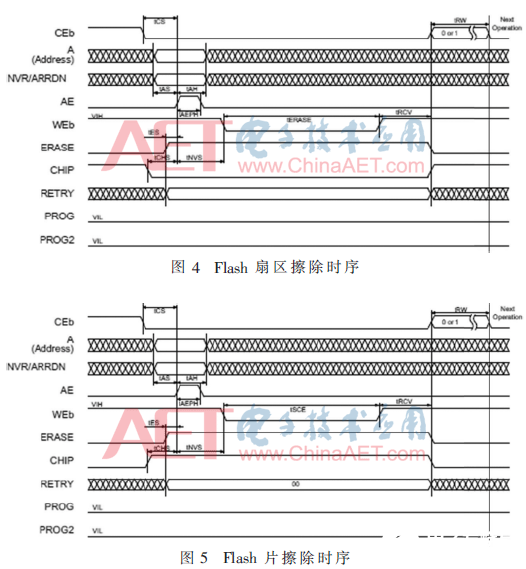

NOR Flash器件的操作分为读、写、扇区擦除、片擦除操作。时序图如图2~图5所示。

Flash读时序,发起AE脉冲锁定地址,tAA时间之后读出数据有效。

Flash写时序,先拉高PROG信号,然后AE脉冲锁定地址,产生PROG2脉冲写入对应数据。PROG拉高持续时间是tHV,也就是说写入时间是用户自己控制的。根据tHV的时间不同,可写入的word个数也不同。本文只讨论单个word的写入。

Flash扇区擦除时序,扇区擦除起始要用AE锁定扇区地址,拉起ERASE信号,执行擦除时序。ERASE时间由tERASE时间参数控制。

Flash片擦除时序,擦除起始要用AE锁定任意地址,片擦除除了拉高ERASE信号,还要拉起CHIP信号。ERASE时间由tSCE时间参数控制。

2 控制器方案

2.1 结构框图

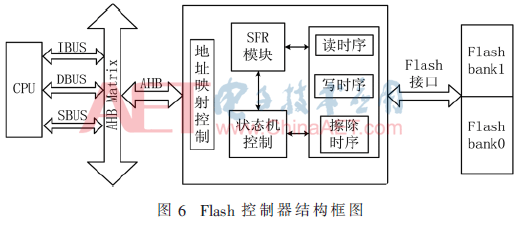

Flash控制器模块在SoC系统中位于AHB matrix总线矩阵和Flash器件之间,CPU为ARM Cortex M4,总线为哈佛结构。CPU可以通过IBUS和DBUS对Flash器件进行访问。Flash控制器结构框图如图6所示。

Flash控制器实现了CPU对Flash器件的读、写和擦除。支持CPU在Flash中执行程序的同时可以对Flash其他区域进行擦写。Flash支持在大于1 MHz的多种频率下能对Flash器件进行擦写。

Flash控制器包含地址映射控制模块、SFR模块、状态机控制模块、时序转化模块。地址映射控制模块用于在线升级时对AHB访问地址进行映射;SFR模块用于Flash控制器的模式控制选择,配置和状态寄存器寄存等;状态机控制模块用于Flash控制器对各种模式的工作状态控制;时序转换模块用于根据状态机的当前状态来产生对应的Flash器件的时序。

2.2 状态机设计

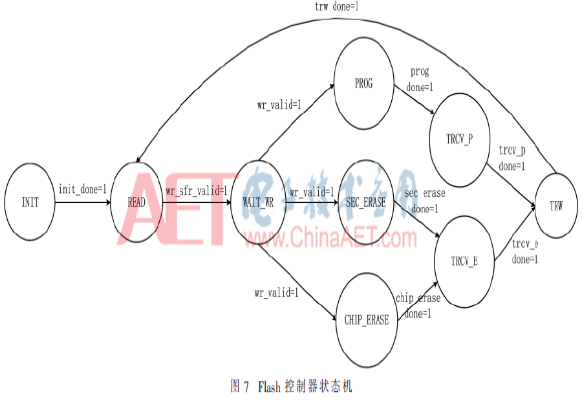

Flash控制器的状态机如图7所示,包含9个状态,INIT状态完成Flash上电启动,init_done之后进入READ状态。READ状态下支持AHB总线读操作。

如果要执行擦写,第一步则在READ状态下配置SFR模块的模式寄存器(PROG或者SEC_ERASE或者CHIP_ERASE),然后状态机跳转至WAIT_WR状态(注:在WAIT_WR状态也支持AHB总线读操作)。

第二步当AHB总线有写操作,则状态机跳转至对应的PROG或SEC_ERASE或CHIP_ERASE状态,开始对应的擦写时序转化。时序转化结束后,PROG跳转到TRCV_P,SEC_ERASE和CHIP_ERASE跳转到TRCV_E。之后跳转到TRW状态,结束后返回READ状态。

3 控制器实现分析

3.1 AHB总线数据相位扩展原理

AMBA AHB总线的写数据总线用来将数据从主机传输到从机上,而读数据总线用来将数据从从机传输到主机上。

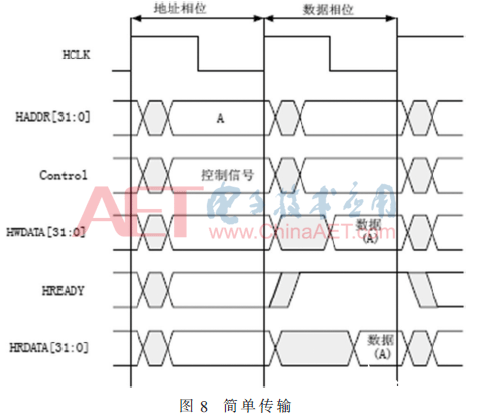

AHB总线基本传输包含两个截然不同的部分:地址相位,只持续单个周期;数据相位,可能需要多个周期,这通过使用hready信号实现。

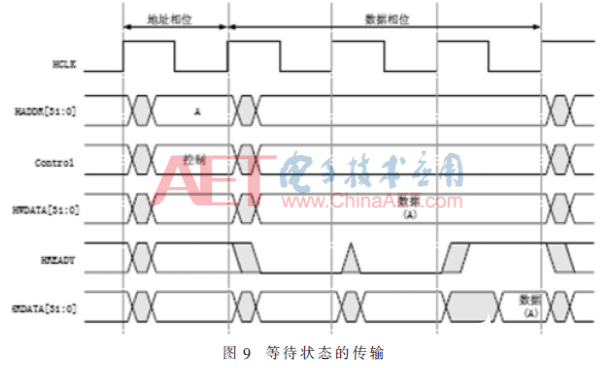

地址不长期有效,所以所有从机必须在这个时段(传输地址时)采样地址。然而,通过hready信号可以延长数据。当该信号为低时导致在传输中插入等待状态同时允许从机有额外的时间提供或者采样数据。

图8表示最简单的传输,没有等待状态。在这个没有等待状态的简单传输中,主机在HCLK的上升沿之后将地址和控制信号驱动到总线上;然后在时钟的下一个上升沿从机采样地址和控制信息;在从机采样了地址和控制信号后能够开始驱动适当的响应并且该响应被总线主机在第三个时钟的上升沿采样。

图9为具有等待状态的传输。从机插入等待周期(HREADY拉低)到任意传输中,这样扩展了传输完成允许的附加时间。对写操作而言,总线主机必须保持数据在整个扩展周期中稳定。

Flash控制器设计的擦写模式状态跳转利用了数据相位扩展阶段数据保持的原理。

3.2 SFR区的位置

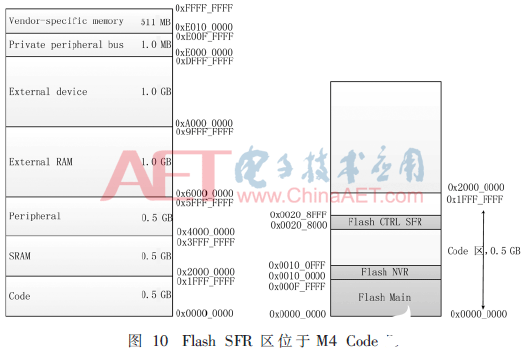

如图10所示,Flash擦写模式寄存器SFR区放在ARM cortex M4的Code区,Code区指0.5 GB以下,即小于0x2000_0000地址的空间,Code区只能IBus/DBus总线通过AHB接口进行访问。不放在Peripheral区APB总线访问,是为了避免IBus/DBus和SBus操作Flash的冲突。

以Flash写操作为例,如果模式寄存器放在Peripheral区APB总线访问,则CPU SBus配置完PROG模式寄存器(访问Peripheral区),准备开始PROG时序转换时,CPU IBus/DBus可能还在读取Flash操作中(访问Code区),这样控制器状态机需要等待判断读结束才能跳转,控制不好可能Flash的PROG写操作和读操作会冲突。

如果模式寄存器放在Code区,则会避免这种情况。配置写模式寄存器的总线是CPU DBus(访问Code区),配置同时必然不会有读Flash(IBus/DBus访问Code区)的操作,因此下一刻即可以开始进行状态机从READ到WAIT_WR或WAIT_WR到PROG的跳转,WAIT_WR跳转到PROG后会开始Flash PROG时序转化。

3.3 Flash读操作

Flash读操作,控制器可以直接将AHB总线读操作进行Flash读时序转换。Flash控制器的READ状态和WAIT_WR状态都支持AHB总线读操作。

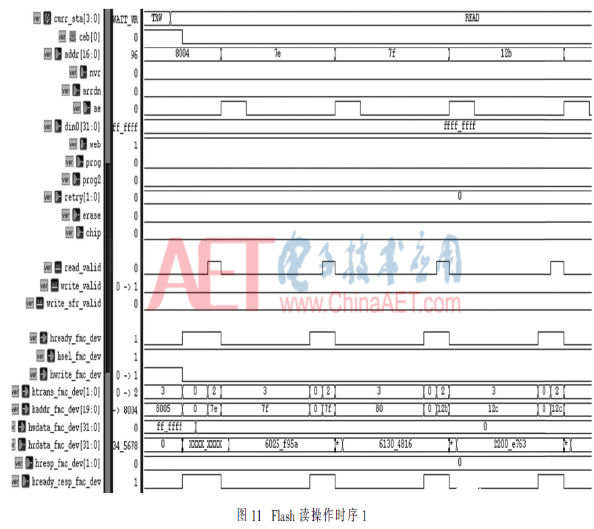

READ状态的读操作时序图如图11所示。

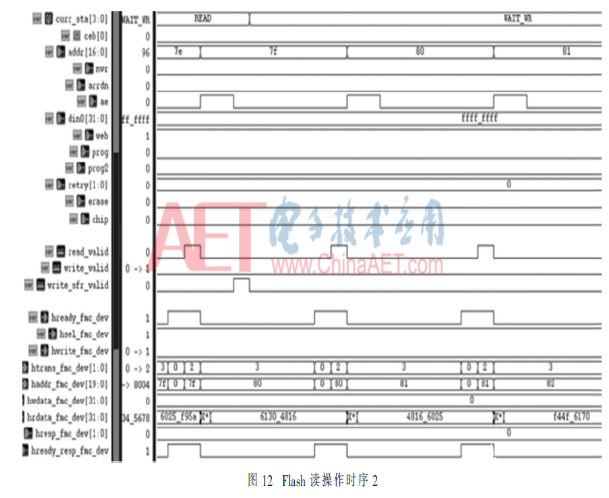

WAIT_WR状态的读操作时序图如图12所示。

3.4 Flash写操作

控制器在PROG状态可以完成Flash写操作的时序转化,采用hready拉总线方式。

进入PROG状态需要CPU执行两步总线写操作,第一步,总线配置写模式,第二步,总线写操作给出写地址,写数据的采样利用的就是AHB总线写操作的数据在扩展周期稳定的原理。

详细的Flash写操作的步骤是:

(1)配置写模式,READ状态跳转到WAIT_WR状态;

(2)在WAIT_WR状态,向目的地址发起AHB总线写,状态机跳转到PROG状态,同时锁定总线的写地址,然后利用hready拉低时数据保持的原理,锁定总线的写数据,然后进行PROG时序转化;

(3)在PROG状态,PROG信号拉高,PROG2产生写脉冲,完成word的写入。之后hready信号被释放拉高,状态机跳到TRCV_P,之后TRW,返回READ态。

注:如果在PROG状态有AHB总线读操作,hready会被拉低,读控制信号和读地址被锁存,持续到编程时间结束,直到返回READ态,正确返回读结果。

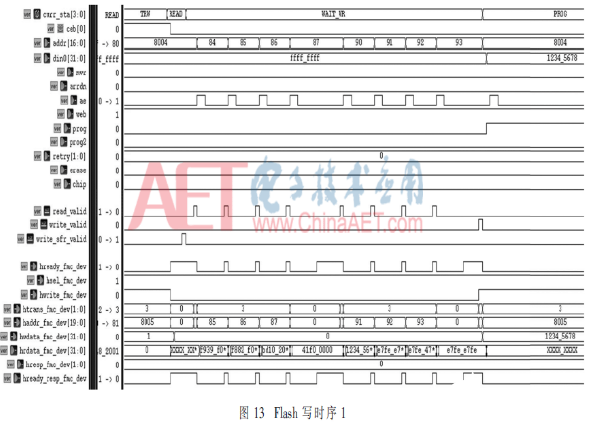

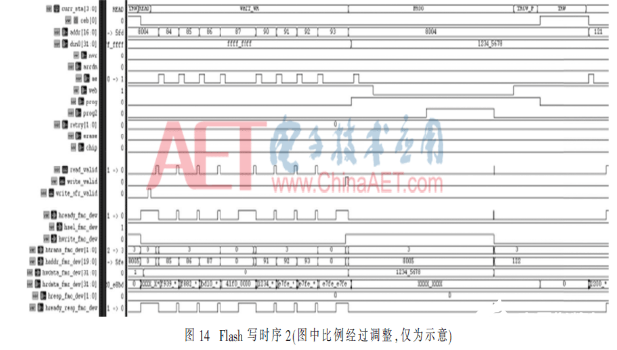

举例:以图13、图14为例说明Flash写操作时序。比如向0x00_8004地址(CPU地址0x0002_0010)写入0x1234_5678数据。write_sfr_valid信号(配置PROG模式脉冲)触发READ状态跳到WAIT_WR状态,然后write_valid信号(AHB总线写0x0002_0010地址,数据为0x1234_5678)触发WAIT_WR状态跳到PROG,开始时序转化。

READ-》WAIT_WR-》PROG写操作时序图如图13所示。

完整的写操作PROG时序示意图如图14所示。

3.5 Flash擦除操作

Flash在SEC_ERASE和CHIP_ERASE状态可以完成擦除操作的时序转化。

进入擦除操作需要CPU执行两步总线写操作,第一步,配置擦除模式,第二步,总线写操作给出擦除地址,对于扇区擦除,总线写操作地址即是擦除地址,片擦除可以是任意地址。

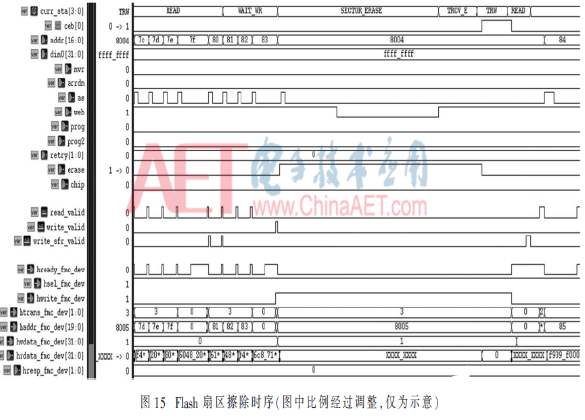

以扇区擦除为例,详细的步骤是:

(1)配置扇区擦除模式,READ状态跳转到WAIT_WR状态;

(2)在WAIT_WR状态,向目的扇区地址发起AHB总线写,状态机跳转到SEC_ERASE状态,同时锁定总线的写地址,提取待擦除的扇区地址,然后hready信号拉低,进行扇区擦除时序转化;

(3)在SEC_ERASE状态,ERASE信号拉高,WEB信号拉低,ERASE信号持续时间达到配置Thv的值时,状态机跳到TRCV_E,之后TRW,返回READ态。

举例:以图15为例说明Flash扇区擦除时序。比如擦除0x00_8004扇区(CPU地址为0x0002_0010)。write_sfr_valid信号(配置SEC_ERASE模式脉冲)触发READ状态跳到WAIT_WR状态,然后write_valid 信号(AHB总线写0x0002_0010地址)触发WAIT_WR状态跳到SEC_ERASE,开始时序转化。

3.6 Flash自编程操作

Flash自编程操作即是Flash写程序在Flash内部执行,同时对Flash其他区域进行扇区擦除和写操作的过程。

CPU每执行一条指令的操作一般分为取指令、分析指令、执行指令。转化为对Flash的操作就是读或写。利用写Flash操作之后hready拉低,锁定总线,进行Flash读写时序转化。

扇区擦除操作的分解步骤如下:

(1)(READ状态)读Flash操作取指令;

(2)发起总线写操作,配置扇区擦除模式寄存器(从READ跳转到WAIT_WR);

(3)(WAIT_WR状态)读Flash操作取指令;

(4)发起总线写操作(从WAIT_WR跳转到PROG);

(5)hready拉低,锁定总线,同时从总线写地址高bit提取Flash扇区地址(当前总线写数据不必关心),然后发起扇区擦除时序转化;

(6)(从PROG跳转到TRCV_E,然后TRW,返回READ)hready拉高,释放总线,返回步骤(1)。

写操作的分解步骤如下:

(1)(READ状态)读Flash操作取指令;

(2)发起总线写操作,配置写模式寄存器(从READ跳转到WAIT_WR);

(3)(WAIT_WR状态)读Flash操作取指令;

(4)发起总线写操作(从WAIT_WR跳转到PROG);

(5)hready拉低,锁定总线,同时锁定总线当前地址作为写地址,利用hready拉低AHB总线数据扩展周期期间写数据不变原理锁定当前写数据,发起word写时序转化;

(6)(从PROG跳转到TRCV_P,然后TRW,返回READ)hready拉高,释放总线,返回步骤(1)。

3.7 IAP硬件地址映射

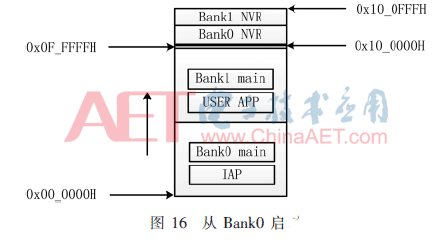

Flash控制器支持两片Flash器件工作,Flash器件为UM055EFLLP128KX032CBA型号,深度方向拼接,统一编址,main区(CPU地址)范围从0x00_0000H~0x0F_FFFFH,NVR区(CPU地址)从0x10_0000~0x10_0FFFH。

正常情况下Flash Bank0位于低地址区域,FlashBank1位于高地址区域。正常启动时CPU从Bank0低地址区域开始执行程序,如图16所示。

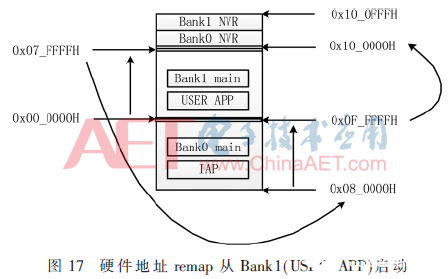

在IAP流程中,如果判断待升级程序容量小于一个Bank容量,则可以使用这种快速在线升级方法,Boot-loader IAP程序放在Flash Bank0,将用户程序USER APP程序写入Flash Bank1中,然后写入更新标志位(标志位放在Flash NVR区)。发起系统软复位,硬件将地址重映射,系统从Bank1高地址区域开始执行程序,如图17所示。

该设计不需要做中断向量重映射,减少了软件的复杂度,方便用户使用。

3.8 时序参数随频率变化

Flash器件要在系统中正常工作,读写擦除的时序参数要满足器件要求。而Flash控制器根据系统的要求,必须能在多种频率下进行正常读写和擦除,这些时序参数值是内部若干个counter计数器根据频率产生的。如果在每个特定频率下,用软件进行一一重新配置所有的时序参数是比较繁琐的。

本控制器将时序参数分为了两类考虑,做了如下设计:

(1)读时序参数

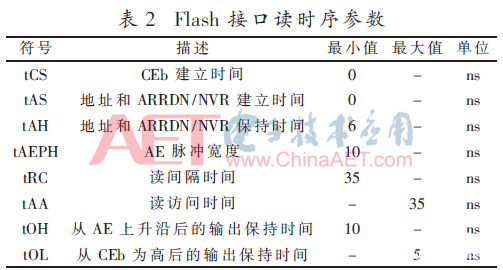

Flash读操作的各时序参数设计上已经给出默认值,能保证系统启动正常工作。需要考虑的主要参数是tAA,表示AE有效到dout数据有效的选通时间,Flash器件要求必须大于35 ns。本控制器设计了读延迟参数值read_latency_cnt,根据不同频率可以配置不同值以满足要求并得到最快访问速度。比如在Flash控制器工作时钟为100 MHz时,周期为10 ns,为满足大于35 ns的时间,read_latency_cnt最小值需要配置为4。读时序参数如表2所示。

(2)擦写时序参数

擦写时序各时序参数值设计上已经给出默认值,能保证系统启动正常工作。当系统工作频率变化时,擦写的各时序参数值也要满足器件要求。

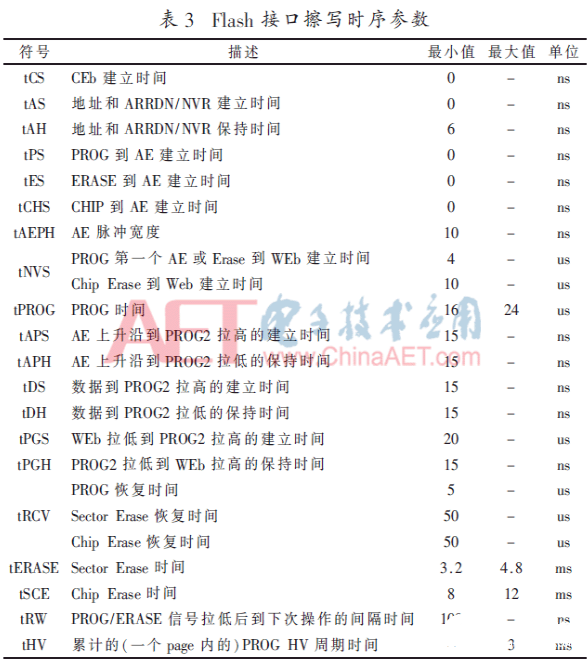

本控制器设计了工作频率寄存器T1US_REF,含义是1 μs需要多少个时钟周期,如果为60 MHz,则配置该寄存器为60,如果为100 MHz,则配置该寄存器为100。内部的微秒级的各时序参数会自动以该寄存器为基准同步变化,这样就减少了软件根据不同频率频繁修改多个时序参数寄存器的复杂度。擦写时序参数如表3所示。

4 结论

本文给出了基于ARM cortex m4 SoC架构下两片UMC55 nm Flash macro IP拼接工作的NOR Flash控制器的设计,介绍了NOR Flash的读、写、擦各种时序的设计流程。

本控制器的特点如下:

(1)利用AMBA AHB hready信号为低时数据相位扩展的原理,支持Flash在线编程,执行过程中支持Flash读操作。

(2)在IAP程序跳转USER APP程序时不需要中断向量表重定向,直接硬件地址映射实现。

(3)通过设定1 μs工作频率配置寄存器,硬件自动计算满足不同频率下的正常擦写时序参数,减少了软件逐个配置多个时序参数的复杂度。

含有该Flash控制器的MCU主控芯片已经通过仿真和FPGA验证,且在UMC55 nm工艺上流片成功,芯片样品经过测试,Flash控制器功能良好,方便使用。

参考文献

[1] 谢同同,李天阳。一种嵌入式NOR Flash 控制器IP的设计[J]。电子与封装,2016(7):18-21,43.

[2] 田鹏,聂泽东,张正平,等。一种兼容AHB总线的Nor Flash控制器IP设计[J]。微电子学与计算机,2013(6):88-91,96.

[3] 周芝梅,赵东艳,张海峰,等。基于IR46标准的双芯电能表主控关键技术研究[J]。电子技术应用,2017,43(10):7-11,19.

[4] 蒋劲松,黄凯,陈辰,等。基于预取和缓存原理的片上Flash加速控制器设计[J]。计算机工程与科学,2016(12):2381-2391.

[5] ARM.AMBA Specification(Rev 2.0)[Z].1999.

-

jf_51190942

2023-05-29

0 回复 举报没有源代码吗 收起回复

jf_51190942

2023-05-29

0 回复 举报没有源代码吗 收起回复

-

MCU片上Flash2025-05-06 1535

-

使用VHDL实现Flash读写控制器设计2023-08-03 2224

-

Flash基本操作——Flash基础(1)#多媒体技术未来加油dz 2023-05-24

-

CH579中有Data Flash和Info Flash,请问这两片Flash有什么不一样?2022-08-04 651

-

8-bit USB Flash MCU的IAP功能应用须知2022-06-26 738

-

瑞萨推出SH7216系列32-位片上Flash存储器MCU2021-12-02 853

-

IAP编程的流程及IAP的应用场所2021-08-11 5598

-

NAND Flash控制器的设计与验证2021-03-29 1321

-

缓存原理的片上Flash加速控制器设计2017-11-23 1188

-

NAND FLASH在WINCENET系统中的应用设计2016-03-14 995

-

基于FPGA的SPI Flash控制器的设计方案2013-09-24 6967

-

ARM片外FIash存储器IAP解决方案2011-11-30 2464

-

一种在片上系统中实现Nand Flash控制器的方法2010-01-12 1293

全部0条评论

快来发表一下你的评论吧 !