FPGA时序约束的建立和保持时间方法

电子说

1.4w人已加入

描述

周期约束理论

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

周期约束就是告诉软件我们的时钟周期是多少,让它PAR后要保证在这样的时钟周期内时序不违规。大多数的约束都是周期约束,因为时序约束约的最多是时钟。

在讲具体的时序约束前,我们先介绍两个概念,在下面的讲解中,会多次用到:

• 发起端/发起寄存器/发起时钟/发起沿:指的是产生数据的源端

• 接收端/接收寄存器/捕获时钟/捕获沿:指的是接收数据的目的端

建立/保持时间

讲时序约束,这两个概念要首先介绍,因为我们做时序约束其实就是为了满足建立/保持时间。

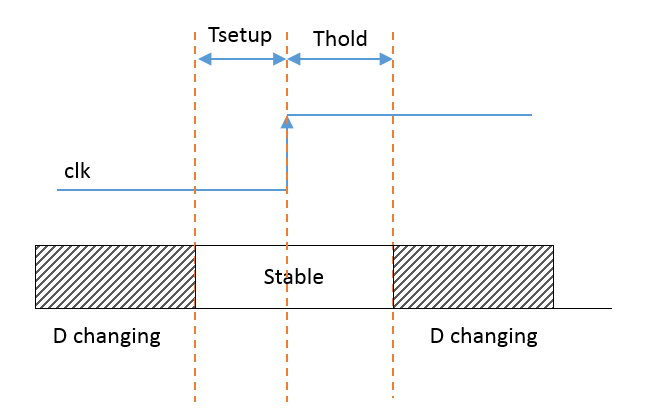

对于DFF的输入而言,

• 在clk上升沿到来之前,数据提前一个最小时间量“预先准备好”,这个最小时间量就是建立时间;

• 在clk上升沿来之后,数据必须保持一个最小时间量“不能变化”,这个最小时间量就是保持时间。

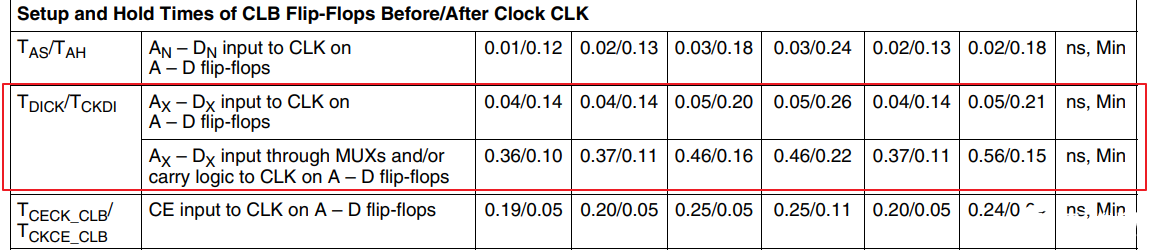

建立和保持时间是由器件特性决定了,当我们决定了使用哪个FPGA,就意味着建立和保持时间也就确定了。Xilinx FPGA的setup time基本都在0.04ns的量级,hold time基本在0.2ns的量级,不同器件会有所差异,具体可以查对应器件的DC and AC Switching Characteristics,下图列出K7系列的建立保持时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

jf_00671415

2025-01-16

0 回复 举报不错 收起回复

jf_00671415

2025-01-16

0 回复 举报不错 收起回复

-

深度解析FPGA中的时序约束2024-08-06 2837

-

FPGA时序约束--基础理论篇2023-11-15 863

-

FPGA时序约束之建立时间和保持时间2023-08-14 2372

-

FPGA时序约束的原理是什么?2023-06-26 1403

-

FPGA时序约束的基础知识2023-06-06 2074

-

静态时序之建立时间和保持时间分析2022-08-22 5788

-

FPGA时序约束一如何查看具体错误的时序路径2022-08-04 1161

-

时序约束的步骤分析2019-12-23 2947

-

VGA驱动接口时序设计数据的建立时间和保持时间2019-04-10 2265

-

FPGA中的时序约束设计2017-11-17 3097

-

关于FPGA时序约束的一点总结2016-09-13 9880

-

FPGA时序约束方法2015-12-14 1007

-

FPGA实战演练逻辑篇57:VGA驱动接口时序设计之4建立和保持时间分析2015-08-02 5886

全部0条评论

快来发表一下你的评论吧 !