对于嵌入式系统该如何实现低功耗设计

嵌入式技术

描述

(文章来源:润欣科技)

在嵌入式系统中,低功耗设计是在产品规划以及设计过程中必须要面对的问题。半导体芯片每18个月性能翻倍。但同时,电池的技术却跟不上半导体的步伐,同体积的电池10年容量才能翻一倍。嵌入式系统对于使用时间以及待机时间的要求也越来越高,这就需要在设计产品的时候充分考虑到整个系统的低功耗设计。功耗控制是一个系统的工程,需要从低功耗的器件选型、硬件的低功耗设计与制造技术、软件的低功耗优化等多个方面来统筹考虑。作者就在润欣科技工作期间服务过的项目,总结从以上多个角度来阐述嵌入式系统中低功耗设计要点。

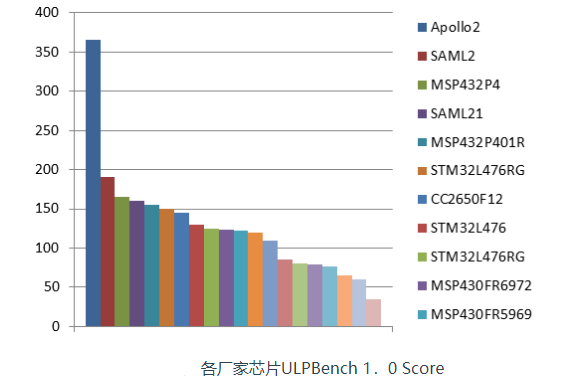

随着半导体工艺的不断发展,半导体的制造工艺也在不断进步,选用先进工艺以及低功耗设计的元器件可以从源头上降低整个系统的功耗。主控芯片的选型要充分考虑到系统的使用场景,对于那些运算任务比较多的应用场景下,可以选用能耗比高的芯片来设计,比如像ambiq的Apollo系列芯片,该芯片采用具有专利的SPOT技术,芯片在亚阈值稳定运行,可减少能源消耗近13倍,实现极致的低功耗技术。

对于嵌入式系统,电源芯片对于低功耗设计是一个很重要的器件。电源芯片自身的功耗以及转换效率在很大程度影响电池的使用时间。进行低功耗的稳压电路设计,需采用低功耗的LDO或者DCDC芯片,如TI的TPS797系列,自身功耗仅1.2uA。

在满足功能需求的情况下,尽量选用带触发输出功能外部器件而非需要轮询的外部器件,这样可以减少MCU的运行时间,平时MCU可以一直处于睡眠状态下,在满足触发条件时有外部器件通过中断唤醒MCU工作。对外围元器件的电源控制,采用带关断功能的器件,进入低功耗模式下不需要工作的外设,可以使用MOS管电路配合MCU控制对局部的电路进行电源管理。在该设备不需要工作时,尽量关断该部分电源,以达到更低的功耗。

多级电压设计,电压和功耗有着密切的联系。因此功耗的降低可以考虑对于不同的电路模块,使用不同的电压等级,可以采用DVFS动态电压频率技术,通过将不同电路模块的工作电压及工作频率降低到恰好满足系统最低要求,来实时降低系统中不同电路模块功耗的方法。

硬件设计对于MCU的每个IO口都要避免IO口漏电流。当外设掉电时,IO口仍然会有潜在的电源输出,所以IO口需要默认配置成低电平或者高电平状态,避免漏电流。适当的降低CPU的运行频率,降低MCU的运行速度,可以有效的降低运行时需要消耗的电流,芯片的功耗和主频是线性的关系,更高的时钟频率意味着更快的MCU运行速度,那么MCU内部CMOS电路就更快的开关频率,导致更高的运行电流和待机电流。

合理的使用MCU的待机模式,在当前没有任务需要处理时,将MCU进入到低功耗的睡眠模式。对于使用嵌入式操作系统的嵌入式产品,一般都是在idle空闲任务中进入睡眠模式,但是为了进一步降低功耗,实现低功耗最优设计,我们还不能直接把睡眠或者停机模式直接放在空闲任务就可以了,需要设计一种更先进的休眠机制,比如在freertos操作系统中使用tickless 低功耗机制,进入空闲任务后,首先要计算可以执行低功耗的最大时间,也就是求出下一个要执行的高优先级任务还剩多少时间。然后就是把低功耗的唤醒时间设置为这个求出的时间,到时间后系统会从低功耗模式被唤醒,继续执行多任务。

关注每一个GPIO口电平状态,在进入睡眠之前配置所有的GPIO口到高电平或者低电平以降低漏电流。对于外挂的传感器以及外围设备,也需要在进入睡眠之前配置其功耗模式以降低消耗的电流。

合理关闭MCU内部模块,对于在Deep Sleep模式下不需要工作的内部模块都要关闭时钟以及电源以节省功耗,同时要重点关注模拟IO口,模拟功能一般是耗电大户,在AD/DA功能不使用的时候尽快关闭,减小使用模拟功能的时间。此外,芯片内部SRAM由于需要不停的刷新,在睡眠模式下也需要消耗一定的电流,可以配置部分SRAM在睡眠模式下保持刷新降低功耗。

对于包含有无线功能的芯片,配置合理的待机参数以降低功耗。如比对于BLE芯片CSR1010,在进行BLE的广播模式下,60ms的广播间隔的待机电流时394A,如果将广播时间增大到1.28S,则待机电流降低到28A。对于wifi芯片,比如高通QCA4004芯片,在DTIM1情况下对应功耗是1.5mA,在DTIM10情况下则降低到334A。

嵌入式系统低功耗需要综合考虑各种可能的因素、条件和状态,需要对各种细节进行认真的斟酌和分析,需要对各种可能的方案和方法进行计算和分析,尽最大的努力优化整个系统的功耗,达到最节省电能的目的。

(责任编辑:fqj)

-

超低功耗嵌入式系统设计技巧2012-08-18 2351

-

嵌入式系统中的低功耗设计2014-01-21 3873

-

基于嵌入式DSP系统的低功耗优化设计2016-08-20 2028

-

低功耗嵌入式系统该怎么设计?2019-09-02 2088

-

什么是嵌入式系统面向低功耗的协同设计系统?2019-09-19 1996

-

低功耗嵌入式设计是什么?2021-04-23 1385

-

嵌入式系统低功耗管理相关资料分享2021-12-21 1113

-

基于μCOS-II嵌入式系统的低功耗开发2009-12-23 1135

-

嵌入式系统设计中的低功耗技术2011-10-12 1691

-

基于μC/OS-II嵌入式系统丌发中低功耗系统的设计2017-11-06 947

-

嵌入式系统的组成及其低功耗的设计2017-12-06 944

-

嵌入式系统低功耗设计2019-09-09 6971

-

在嵌入式系统中如何实现低功耗设计2020-03-27 2476

-

嵌入式Linux的低功耗策略2021-11-01 1151

-

低功耗嵌入式设计的提示和技巧2022-12-28 1483

全部0条评论

快来发表一下你的评论吧 !