I2S接口概述和与DSP的连接方法

电子说

描述

I2S接口概述

I²S或I2S(Inter-IC Sound或Integrated Interchip Sound)是由飞利浦公司(现NXP)在1986年制定的一种用于音频IC或者设备之间传输数字PCM信息的一种接口标准。I2S常被使用在各种音源到音频DAC中。由于I2S将信号以及时钟分开传送,它的jitter失真十分地小。I2S和I2C名字非常的像,但是切记,他们完全不是一个东西,甚至连时序都不太像,要说同I2S最像的还是SPI。I2S规范最终的修订是在1996年。

I2S接口硬件定义

NXP公司的I2S是一套硬件+时序规范。I2S硬件上有3个主要信号:

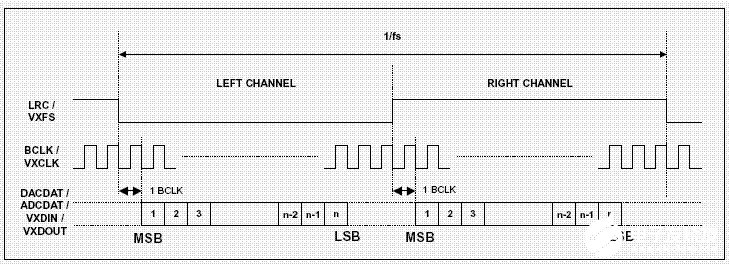

continuous serial clock,连续串行时钟SCK,在一些资料中也就SCLK或者BCLK,即对应数字音频的每一位数据,SCLK有1个脉冲。SCLK的频率=2×采样频率×采样位数。

word select,字选择WS,又叫帧时钟LRCK,用于切换左右声道的数据。WS为“0”表示代表传输的是左声道的数据,为“1”则表示正在传输的是右声道的数据。WS的频率等于采样频率。

serial data,串行数据SD,又叫SDATA,是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍,这个信号在后面会单独讲到。

I2S接口时序与对齐

I2S接口有着统一的硬件定义,但是数据的传输格式又各有不同,我们把他们分成三类:

I2S格式

左对齐格式,left justified

右对齐格式,right justified,也叫EIAJ或者SONY格式

这三种传输格式,基本都是相同的,不同之处在于SD数据同WS信号的对齐位置。I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在WS变化(也就是一帧开始)后的第2个SCK脉冲处,见下面I2S格式图:

i2s timing

故名思议,左对齐(left justified)、右对齐(right justified)指的是数据信号对齐的方式,左对齐的时候最高位数据在第一个时钟就出现,而右对齐的时候数据最低位在最后一个时钟出现。这就是他们的本质区别。左右对齐模式随具体的芯片不同而不同,在使用的时候需要仔细阅读芯片手册。I2S允许接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

I2S接口的Master和Slave模式以及其同DSP的连接方法

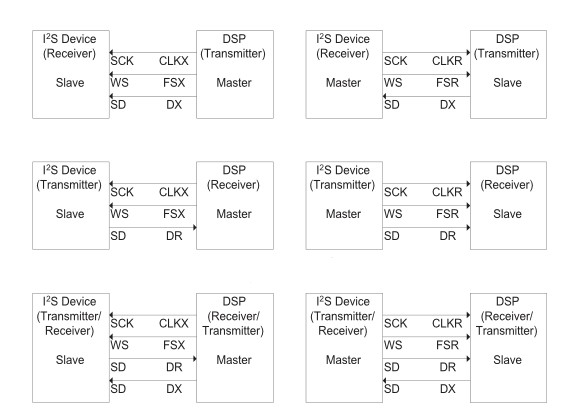

TI公司的DSP可用的I2S接口有McBSP以及McASP,两个接口大同小异,下图代表了不同模式下的DSP同I2S设备的连接关系:

TI DSP I2S connecting mode

图中,箭头代表了信号的传输方向,主模式(Master)以及从模式(Slave)的区别就在于时钟信号是由哪一边给出的。在使用的时候需要参考McASP以及McBSP的资料。在DSP上使用I2S主要分为以下几个步骤:

器件选型,确定连接模式(Slave or Master)

设计原理图,正确连接电器关系

McBSP或者McASP寄存器配置

从(往)FIFO中Put or Get 数据即可

I2S接口的MCLK作用

MCLK是Master clock的缩写,在DAC内部的delta-sigma调制器以及数字滤波器都需要用到这个时钟,大部分的DAC可以使用内部的振荡器产生这个时钟,在某些要求较高的场合,例如HIFI音响系统等,需要使用一个额外的高质量的时钟用以获得最好的性能。这时候就需要用到MCLK信号了。切记,MCLK并不是必须的。可有可无,看设计要求。MCLK一般是Fs*256或者Fs*384。

-

请问PCM4204是I2S接口吗?2024-09-27 509

-

雅特力AT32 MCU SPI/I2S入门指南2023-03-08 8474

-

AN5086_如何使用标准SPI和Timer来模拟I2S接口2022-11-21 652

-

#硬声创作季 #STM32 手把手教你学STM32-082 I2S简介和实验硬件连接-1水管工 2022-10-29

-

I2S、TDM、PCM音频总线2022-09-20 7582

-

智能硬件设计中I2S、PDM、TDM选什么音频接口2022-02-23 14240

-

TN:将I2S兼容音频设备连接到ADSP-21065L2021-04-27 1029

-

音频总线I2S协议:I2S收发模块FPGA的仿真设计2020-12-14 10148

-

I2S接口工作原理_I2S接口介绍2018-01-29 115636

-

基于FPGA和AD1836的I2S接口设计2011-03-29 7342

-

音频接口I2S实验2010-12-29 1728

-

利用MAXIICPLD实现SPI至I2S的接口2010-07-05 739

全部0条评论

快来发表一下你的评论吧 !