微控制器如何来实现内部可编程逻辑

可编程逻辑

描述

(文章来源:OFweek)

四家公司(Atmel、赛普拉斯、Microchip和NXP)均可提供“胶连”逻辑,帮助减轻主处理器的负荷,或是无需使用外部逻辑。就提供的逻辑模块类型和这些逻辑模块彼此互联的方式以及与定时器、UART和IO引脚等板载模块互联的方式而言,每家公司都采取了不同的方法。

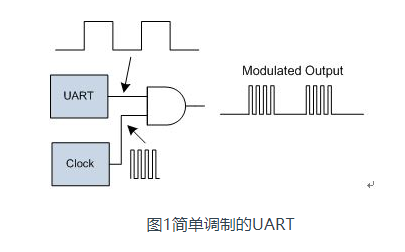

因此有必要了解这些厂家各自是如何实现内部可编程逻辑的,以便为选择最适合自己项目的解决方案做出最佳决策。只要一个简单的内部AND或者OR门控就足以避免使用外部组件,或是改善CPU性能。所有四种方法都支持用定制逻辑门控输入和输出信号。这类方法可借助时钟门控输入,以便使用计数器测量外部时钟频率。这四类逻辑模块均支持的一个简单例子是一种调制UART输出,使之用于IR通信的方法。在此例中,不仅有图1所示的内部AND门控,还能够将来自时钟或计数器的信号及UARTTX输出路由到AND门控。

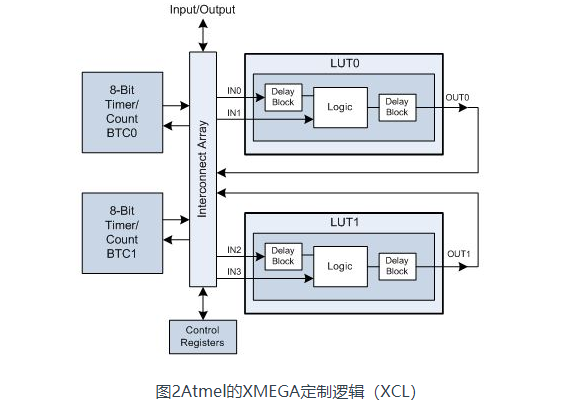

AtmelXCL模块内置两个LUT(查找表)模块,配套两个8位定时器/计数器模块。这两个LUT不必连接到定时器/计数器模块,而是与UART、EVENT模块或IO引脚互联。这两个LUT可用作两个独立的2输入单元或一个单独的3输入单元。该逻辑模块可配置为组合逻辑。它们也可配置为顺序逻辑功能,例如D触发器、D锁存器或RS锁存器。由于能够与其它逻辑模块和IO引脚互联,这些简单的LUT模块能够方便地让设计人员避免使用某些外部逻辑,或者节省CPU周期。例如AtmelXCL模块应用手册解释了如何配置XCL模块,以避免在产生额外CPU开销或使用外部逻辑的情况下,为UART输出提供曼彻斯特编码。AVRXMEGAE器件内置一个XCL模块。

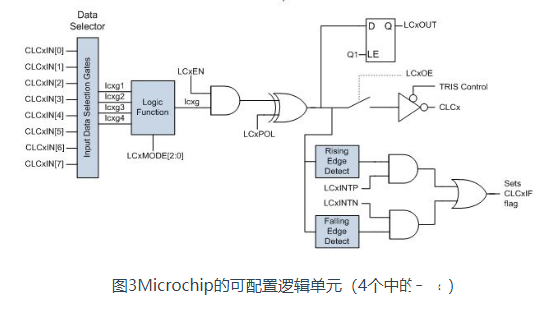

MicrochipCLC允许用户从八路输入中选择最多四个信号。这些输入可以是两个IO引脚、内部时钟、外设或寄存器位的组合。这四个信号随后路由到可编程逻辑模块中。该逻辑模块可编程为AND-OR、OR-XOR、4输入AND、S-R锁存器的8种组合之一,也可配置为4种其它触发器组合之一。其中的实例之一演示了如何配置这些模块以解码正交信号。在不使用这些额外的逻辑模块情况下,CPU需要以高得多的速率采样信号,才能避免正处于转换阶段的信号发生伪旋转,让CPU只被有效转换中断。MicrochipPIC10(L)F320/322器件每个都包含一个CLC模块,而每个CLC模块都包含四个图3所示的模块。

NXP提供的用户可配置逻辑被称为模式匹配引擎。该逻辑模块的输入可选择最大八个GPIO输入。这八个输入可为复杂的布尔表达生成乘积项。这些输出可用于触发中断,驱动特殊IO引脚,或是路由到下一个逻辑模块或slice。其它特性则支持上升或下降信号以及反相信号的边缘检测。该附加硬件经配置后,只有发生复杂(或简单)事件组合时才中断CPU。NXPLPC81x器件内置一个模式匹配引擎。

(责任编辑:fqj)

-

什么是可编程逻辑控制器?可编程逻辑控制器有哪些特点?2021-07-05 3202

-

可编程逻辑控制器简析2021-09-07 1368

-

PLC可编程逻辑控制器的设计原则2021-09-09 1796

-

可编程逻辑控制器的特点及应用2021-10-11 2255

-

三菱PLC(可编程逻辑控制器)编程实例项目例程-电机2022-03-22 1034

-

三菱PLC(可编程逻辑控制器)编程实例——弯管机plc程序2022-05-17 1514

-

三菱PLC(可编程逻辑控制器)编程实例——自动门2022-06-06 950

-

小型水电站的PLC(可编程逻辑控制器)编程实例2022-06-26 754

-

可编程逻辑控制器是什么_可编程逻辑控制器原理2019-07-31 13169

-

可编程逻辑控制器的概念2020-05-29 5188

-

可编程逻辑控制器的作用2022-07-12 3324

-

可编程逻辑控制继电器2022-11-01 1601

-

可编程逻辑控制器的原理与组成2023-03-24 1999

-

可编程控制器PLC概述2023-04-19 1293

-

可编程逻辑控制器和微控制器的区别2024-06-03 2245

全部0条评论

快来发表一下你的评论吧 !