基于CPCI总线接口和LVDS接口的接收和传输测试数据实验设计

接口/总线/驱动

描述

0 引言

随着科学技术的迅猛发展,越来越大的数据传输量和越来越高的数据传输速率成为信号处理系统亟待解决的问题。因而,开发一种能够实时处理大量高速数据,同时兼具稳定性和通用性的新总线成为整个数据链技术中迫切需要解决的瓶颈之一。CPCI (紧凑外围设备互联总线)结合了PCI总线的电气特性和欧式卡的机械标准,可提供132 MB/s的峰值带宽[1],同时CPCI构架开放,性能优良,在可靠性、兼容性和机械性能等方面均有优势。 因此,CPCI总线已成为当今应用最广泛的工业计算机总线,基于CPCI总线的工业控制计算机已经成为解决大量高速数据处理的一个新方向。

基于某测试任务,本文详细阐述了通过CPCI总线接口和LVDS接口接收和传输测试数据,在保证可靠性的前期下,提高了地面设备接收和处理数据的速度。测试结果表明,此方法可行可靠,圆满完成了测试任务。

1 总体设计

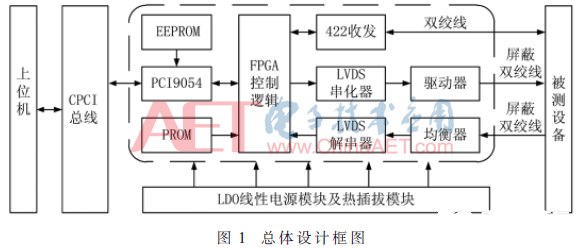

本设计的主要工作是对外接CPCI设备进行命令下发、状态检测及数据接收操作。其主要工作流程是:由上位机下发命令字控制整个系统的正常运行,主控芯片XC3S400通过PCI9054桥接从背板总线接收主机卡发出的命令字,完成逻辑控制;通过RS422接口与外接设备进行通信,控制外接设备进入相应的工作状态以及接收其相应的状态返回;通过LVDS接口接收外接设备的高速数据,将数据写入FPGA的FIFO后,由PCI9054通过DMA控制器将接收的数据回传至主机卡。总体设计框图如图1所示。

整个设计以FPGA为控制核心,充分利用其强大的可编程能力[2],能够灵活控制总线传输速率等多个指标,在增加系统通用性的同时,也充分发挥了CPCI总线高速传输的优势。

2 RS422接口设计

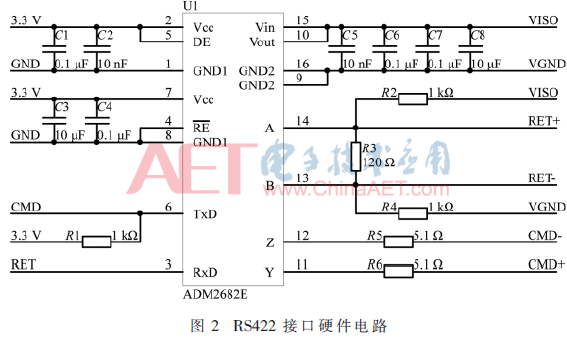

RS422接口用来下发命令字和接收状态字,由于信号码率较低,为625 kb/s,因此设计中主要考虑传输的稳定性和可靠性。本设计针对此问题首先选择了抗干扰性强的差分对信号传输数字量,同时对信号采取隔离措施,以防止前后级设备之间的互相干扰。接口电路示意图如图2所示。

该接口电路选用ADI公司的磁隔离全双工收发器ADM2682E,无需外接DC/DC隔离模块。但是输入输出的供电引脚需要电源旁路,噪声抑制需要一个低电感高频电容,纹波抑制需要一个大容量电容。为了抑制噪声和降低纹波,至少需要并联两个电容,其中容值较小的电容靠近器件摆放。因此,在器件的VCC与GND1,VISOIN、VISOOUT与GND2之间均要加去耦电容。

差分输入端R2将差分输入正端上拉至VISO,R4将差分输入负端接地,这样做的好处是可以防止因为差分信号长距离传输造成的信号削弱,阻值均选择1 kΩ;因为数据传输电缆为特性阻抗为100 Ω的第五类屏蔽双绞线,R3的作用是可以减少信号的反射和衰减,提高数据传输的可靠性,阻值选为120 Ω。

3 LVDS接口设计

3.1 硬件接口

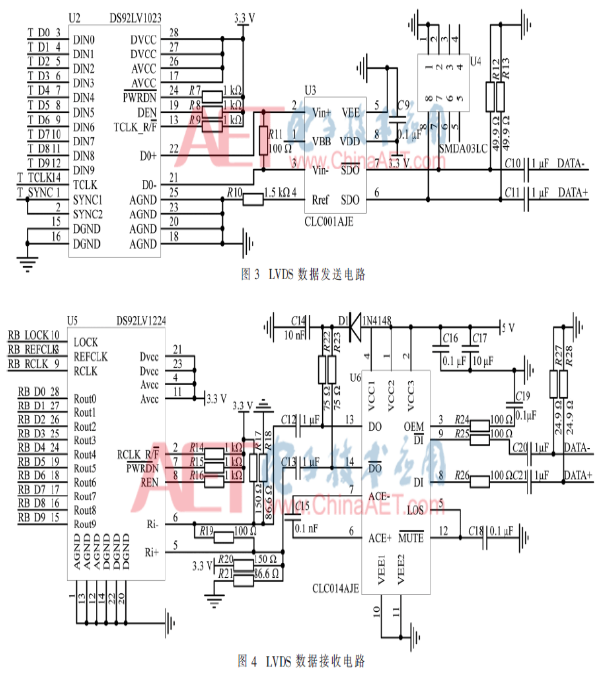

LVDS技术采用低压摆幅和和低电流驱动输出,具有很强的抗干扰性[2-4]。TI公司的DS92LV1023和DS92LV1224分别是高速串行差分数据流串化器和解串器。

在系统上电后,DS92LV1023和DS92LV1224将所有输出引脚置为三态后,启动锁相环跟踪并锁定本地的全局时钟。LVDS串化器连续给数据接收端的解串器发送同步信号,当解串器锁相环成功锁定同步时钟后,LVDS接口将串行数据送出。同理,LVDS解串器也需要与发送端同步后才能接收数据。若在数据传输的过程中解串器锁相环失锁,时钟紊乱,则LOCK信号会置高电平以通知串化器进行再同步的操作。

为了延长LVDS数据的传输距离,在发送端和接收端分别增加了电缆驱动器和电缆均衡器,以此来增强差分信号的驱动和补偿能力。驱动器CLC001AJE的传输速率最高可达622 Mb/s,通过配置外围电阻将DS92LV1023输出的低压差分信号压差从200 mV提升至0.9 V~1.1 V,有效增强了信号的驱动能力。在信号的接收端,信号经过屏蔽双绞线传输,衰减后很容易造成码间串扰,均衡器CLC014AJE可针对带宽50 Mb/s~650 Mb/s的信号进行补偿。恢复信号强度后,再通过DS92LV1224将串行数据解串[5]。LVDS数据发送、数据接收电路分别如图3、图4所示。

3.2 软件逻辑设计

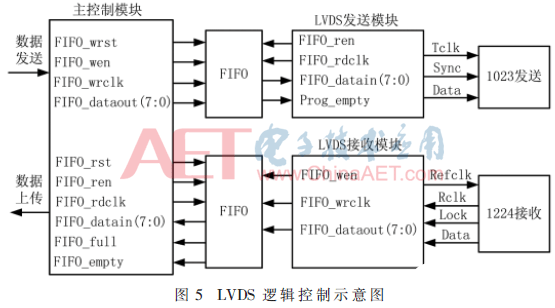

LVDS逻辑控制示意图如图5所示,控制模块由FPGA内部的FIFO完成数据的缓存。上电后,LVDS发送模块向外部发送同步信号Sync,FIFO空标志信号Prog_empty为0时,FIFO读使能信号FIFO_rden_reg置1,将FIFO中的数据读出,然后向外部接口发送,线上空闲时发送无效数据[6-7]。

LVDS接收模块在时钟Rclk的上升沿,对从被测设备接收到的数据进行纠错;在时钟Rclk的下降沿,判断若接收到的数据为有效数,则内部的数据有效信号置1,将有效数据发送给FIFO,通过主控制模块上传至CPCI总线。

4 CPCI总线接口实现

目前,CPCI总线接口的实现主要有2种方法:(1)使用可编程逻辑器件自行设计;(2)使用专用的协议转换芯片,将CPCI总线转换为用户自定义的本地总线[8]。第二种傻瓜式的实现方法虽然不如第一种方法灵活,但胜在省时省力,简单易用,开发周期短,因此应用较为广泛。

4.1 PCI9054工作模式

本设计采用PLX公司的PCI9054协议转换芯片,其本地工作模式采用逻辑控制简单、开发难度较低的C模式,该模式下PCI9054芯片内部的地址线和数据线相互独立,用户可以自行定义需要的本地时序,实现CPCI接口的通信功能。CPCI接口与本地总线之间的数据传输有3种方式:PCI Initiator模式、PCI Target和DMA模式。PCI Target模式是CPCI主设备通过PCI9054发起对本地总线上资源的访问;DMA模式即PCI9054通过控制CPCI和本地两条总线来实现数据的突发传输。本设计主要工作是命令字的下发和数据的上传,考虑操作的简易度,对于命令字的下发采用Target模式下的单周期访问模式,对于数据的上传采用DMA模式突发传输[9]。

PCI9054与CPCI总线的连接是通过CPCI连接器J1实现的,即PCI9054的CPCI信号通过串接10 Ω匹配电阻与J1的相应信号引脚连接,串接10 Ω电阻是为了减少总线分支因为较大的背板阻抗对总线产生的瞬态干扰,保证信号传输的准确性。PCI9054的本地时钟由外部有源晶振提供,且与FPGA端的时钟同步。在FPGA内部划分一块FIFO作为数据缓存,利用其双口操作的特性实现数据的跨时钟域传输,同时也方便了本地时序的设计。

4.2 CPCI本地总线接口实现

CPCI本地总线接口是本设计的核心所在。整个CPCI接口的设计思路是:主控芯片FPGA通过桥接PCI9054与CPCI总线交互,由其内部逻辑自定义本地总线的工作时序实现对总线的状态控制,同时产生片内读写及地址信号完成单周期读写和突发传输的功能。在FPGA内部划分一块FIFO作为数据缓存来实现数据突发读取,由其半满信号作为上位机的读取标志。基于这种设计思路,为了保证通信的可靠性,本文设计了类似握手协议的通信方式,具体操作如图6所示。

系统上电复位后状态机在S0状态循环等待。当上位机下发指令时,CPCI总线将Lhold信号拉高来申请本地总线,本地总线将Lholda信号拉高作为应答信号将总线控制权交给PCI9054。然后CPCI总线将Ads#拉低,开启新的总线传输,将命令字写入约定好的地址LA0。FPGA在检测到Ads#有效后离开S0进入S1状态。判断Blast#为低,进入单周期传输模式,判断LW/R#为低,执行Target读操作,即从CPCI总线接收上位机下发的命令字,然后拉高Ready#和Blast#表示单周期读操作结束。接着状态机返回S0继续检测Ads#信号。根据协议,FPGA会接着执行一次单周期Target写操作,将收到的命令字向上位机返回,由上位机对比两次命令字,结果一致表明命令下发成功,否则重新发送。这种增加反馈确认程序的命令下发模式有效保证了命令发送的准确性。

当下发的命令字要求上传数据时,FPGA将内部FIFO缓存的半满标志根据协议写入固定地址,上位机每间隔一定个CLK会自动执行一次单周期读操作,读取该地址的标示内容,若标示有效,则状态机进入DMA突发传输模式时,结束后返回S0状态,继续读取半满标示,直到命令结束。

这种结合PCI Target单周期模式读写指令和DMA突发模式传输数据的传输模式,既在节省CPU资源的同时保证了命令的准确下发和反馈,也有效发挥了CPCI总线的高速传输数据的优势[10]。

5 仿真与试验结果分析

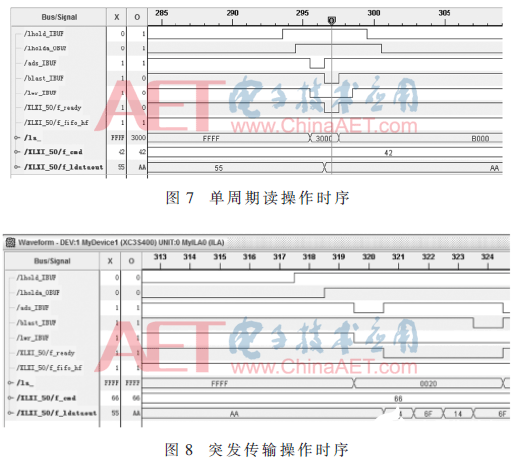

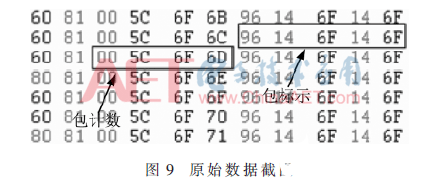

调试使用ISE配套的ChipScope Pro软件实时分析本地总线操作时序,图7为单周期读操作时序。在上位机下发上传数据的指令42H后,CPCI总线每400个CLK自动执行一次单周期读操作,判断地址0x3000内的数据标示是否为AA,如果是,说明缓存已准备好有效数据,上位机可以突发取数。经过390个CLK后,上位机开始突发取数,图8为突发取数操作时序,上位机从地址0x0020~0x1820取走FPGA写入的2K数据,每次突发4 B。实际工作时序与CPCI本地接口的理论时序一致。图9是上位机解包后的原始数据,其中包标示用于区分模拟量和数字量,包计数用于鉴定丢包。整个数据文件帧结构完整,包计数连续,没有丢数现象,进一步证明了本设计中CPCI接口与本地接口衔接合理,方案可行。

6 结论

本设计以PCI9054和FPGA控制器为核心,以LVDS为数据传输接口,从软硬件两个方面介绍了CPCI总线和本地总线的交互设计,通过协议转换芯片简化了整个设计,完成了数据传输卡与上位机之间的通信。测试结果表明,本设计方案可行、可靠,同时也可以为PCI、PXI平台的设计提供参考价值。

参考文献

[1] 金海平。基于FPGA及CPCI总线的数据采集系统设计[D]。长沙:国防科学技术大学,2013.

[2] 李北国,杨圣龙,李辉景。基于FPGA的LVDS高可靠性传输优化设计[J]。电子技术应用,2018,44(8):78-81,85.

[3] 赵阳刚,郭涛,黄玉岗。基于FPGA和LVDS的弹载数据回读系统设计[J]。电子器件,2017,40(1):113-117.

[4] 郭虎峰,陈香香,李楠。基于LVDS总线和8b/10 b编码技术的高速远距离传输设计[J]。自动化与仪表,2015,30(5):32-36.

[5] 任勇峰,彭巧君,刘占峰。基于FPGA的CPCI高速读数接口设计[J]。电子器件,2015,38(1):148-151.

[6] 郭柳柳,储成君,甄国涌,等。基于PXI总线高速数据传输卡的设计[J]。计算机测量与控制,2014,22(6):1899-1901.

[7] 魏丽玲,朱平,石永亮。基于FPGA的图像采集与存储系统设计[J]。电子技术应用,2015,41(11):67-69,73.

[8] PLX Technology.PCI 9054 Data Book.Version 2.1[Z].2000.

[9] 李昕龙,刘亚斌,周强。基于PXI/CPCI总线的LVDS数据收发模块设计[J]。微计算机信息,2012,28(9):105-106,273.

[10] 王晓君,宇文英,罗跃东。基于FPGA的CPCI和LVDS接口技术及应用[J]。半导体技术,2007,32(3):248-251.

-

lvds接口传输距离限制 lvds接口优势及劣势分析2024-11-21 3833

-

LVDS接口有哪些分类2024-01-18 3688

-

怎么实现基于CPCI接口的AFDX终端测试板卡通讯模块设计?2021-05-24 1390

-

探究CPCI总线的PMC载板设计2021-05-05 4742

-

FPGA视频拼接项目LVDS视频传输数据接口介绍2019-12-11 3138

-

LVDS接口的传输速率是怎么计算的?2017-01-02 25093

-

基于FPGA的cPCI接口数据采集系统设计2016-01-06 925

-

基于FPGA的LVDS接口应用2012-01-11 1206

-

CPCI数据总线接口的设计与实现2011-07-17 15826

-

基于LVDS 技术的传输接口设计2010-09-22 1572

-

基于cPCI总线的高速数据光纤传输系统的实现2009-06-17 765

-

LVDS接口电路及设计2009-06-16 6162

-

lvds接口定义2008-07-01 18469

全部0条评论

快来发表一下你的评论吧 !