以FPGA为基础的ASI/SDI码流播放器设计介绍

可编程逻辑

描述

在各种测试工作中,码流的传输是必不可少的,常用的接口有:异步串行接口(ASI)、串行数字接口(SDI)、同步并行接口(SPI)、同步串行接口(SSI)。其中,ASI与SDI接口因为连线简单(只需一根同轴电缆线传输),传输距离长,抗干扰能力强,输入反射损耗较小等原因被广泛应用为码流的传输接口。

PC机是各种测试过程中最常用的测试工具,作为PC机最常用的接口的通用串行总线USB,因为标准统一,支持热插拔,可连接多个设备等优点,逐渐成为测试工具的常用接口,若能实现USB接口与传输码流的ASI/SDI接口的连接,将给数字电视测试工作带来极大便利。

设计ASI/SDI码流播放器的目的是设计出手机大小的电路板,一端是USB接口,另一端是则ASI/SDI接口,通过FPGA、UB2.0等芯片实现ASI/SDI接口与USB接口之间的转换,以达到TS流的录制与播放和对码流进行分析的目的。

1 码流播放器的整体结构设计

目前,DVB-ASI接口的实现大多采用Cypress公司的CY78933和CY78923芯片与CPLD或FPGA相结合的方案,这种方法固然可以实现ASI信号的收发,但芯片费用和PCB面积的占用却是数字电视前端设备追求低成本和微型化的障碍,针对这种情况,文中设计的ASI信号接收与发送系统采用同轴电缆作为其底层物理信道,用FPGA芯片完成了CY7B933和CY78923芯片的ASI信号的接收与发送功能,可有效节约成本,降低PCB的设计难度,并可用FPGA芯片完成其他功能。

国内外绝大多数是使用PCI或PCI-E接口,只能在台式机或服务器上使用,随着PC机的微型化,笔记本电脑的普及,PCI或PCI-E接口已经无法完全满足数字电视测试工作的需求,所以本设计使用的是最通用的USB接口,大大降低数字电视测试工作的难度。

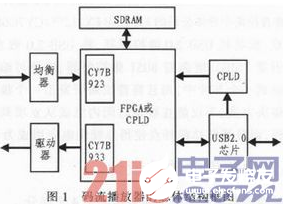

如图1所示,ASI/SDI码流播放器的设计是基于FPGA和USB2.0芯片来实现的,集成度高,方便轻巧,能在PC机上轻松实现码流捕捉,分析,监控和播放ASI/SDI数字流,现场录制和分析MPEG-2码流,还可以作为便携式的演示设备。

2 码流播放器的硬件模块设计

使用FPGA实现了CY7B933和CY7B923芯片的功能,节约了大量成本;同时,用Cypress公司的USB2.0芯片CY7C68013A替代PCI或PCI-E接口,因为传输的码率较大,理论最大值为216 Mb,FPGA内部资源RAM资源无法满足要求,添加一个SDRAM作为缓存,缓冲数据,以免丢数。

另外,由于选择了低端的FPGA芯片,在编写版本FPGA程序时发现,其内部逻辑资源较少,无法装下实现ASI和SDI的全部功能程序,而且实际工程应用中并不需要同时实现ASI和SDI的功能,故添加了一个的CPLD,实现FPGA的PS模式的动态加载功能。

2.1 均衡器/驱动器

输入前端均衡器(Equaliser)选用的GS9064是第二代的双向性高速集成电路,均衡和恢复收到的信号(75Ω同轴电缆,速率从143 Mb/s到540 Mb/s),支持SMPTE 344 M和SMPTE 259 M标准,且270 Mb/s时性能最佳。具有自动检测线长并根据信号强弱自动匹配均衡的功能,也可根据特定需要设置均衡参数。

Driver选择CLC001驱动器,CLC001是集成高速电缆驱动器,可用来传输SMPTE 259M标准的串行数字视频和ITU-TG.703标准的串行数字数据(75Ω传输线,速率高达622Mb/s)。CLC001输出功耗小,十分适合长距离高速传输。

2.2 数据处理

输入输出信号都经由差分线进入FPGA,出于成本的考虑,选择性价比较高的Altera公司生产的低端Cyclone I系列EP1C6F256C6。在FPGA内部实现ASI/SDI输入输出的控制,信号的串/并转换,码流分析,数据缓存(读写SDRAM),码流传输等功能。

因为TS流数据量较大,同样出于成本的考虑,选择在FPGA上外挂一个SDRAM,作为缓存(如果使用高性能FPGA,就可以使用FPGA内部RAM资源,但是成本较高)。FPGA程序的编写,尤其是控制SDRAM读写作为缓存的部分,是本设计的难点之一。

2.3 USB微控制器

FPGA控制的输入输出码流都经由USB2.0芯片传送至PC机。赛普拉斯半导体公司的EZ-USB FX2LP(CY7C68013A)是高集成、低功耗USB 2.0微控制器,将USB 2.0收发器、串行接口引擎(SIE)、增强型8051微控制器,以及可编程外设接口集成到一个芯片中,而且赛普拉斯研发出一个极具成本优势的解决方案,不仅能在极短时间内完成从立项到投放市场的过程,而且其低功耗特点使得总线供电应用成为可能。

3 码流播放器的软件设计

码流播放器软件系统主要包括以下4个部分。

3.1 FPGA程序功能模块

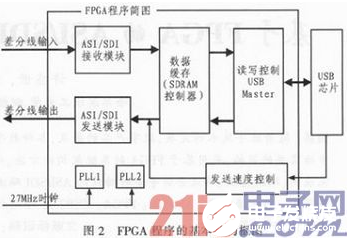

如图2所示,系统输入时钟为27 MHz,由两个PLL锁相环倍频得到270 MHz,135 MHz和两个相位差90度的337.5 MHz时钟。其中270 MHz是为ASI Transmitter提供,其余3个均为ASI Receiver所需。

ASI Transmitter模块的作用是,先进行8B10B编码,再把并行的27 MHz数据按照标准协议转成270 MHz的串行数据。

ASI Receiver模块则是ASI Transmitter的逆过程,先进行串并转换,用5倍时钟采样对数据进行校准,然后分析同步包头等信息,再进行8B10B解码,得到8位并行数据。

SDI部分与ASI十分相似,不重复介绍。

码流播放器是全双工设计,但是,因为FPGA与USB芯片之间的数据传输管脚是复用的,不能同时双向传输。所以,在FPGA与USB芯片之间需要不停的快速切换读和写(1μs切换一次),即可实现“同时”发送和接收数据。

同时发送和接收数据时,受切换的影响,速率减半,且USB接口时钟最大支持仅为48 MHz,所以当收发同时进行的时候,传输速度无法达到理论最大的216 Mbps。如果只是单向发送或者接受数据,系统会自动切换成接收或者发送模式,基本可以达到数据传输理论最大值的216 Mbps。

发送码流时,可以在上位机软件的操作界面上输入发送速率(从0到216,000,000 bps),上位机通过USB芯片,把发送速率传到FPGA,FPGA就可以按照所得速率,精确控制发送码流的速度。

为了达到码流收发的理论最大值,在FPGA上外挂一个RAM,通过对RAM的读写的控制,实现先入先出(FIFO)的缓存功能。FPGA对RAM的读写控制是编写Verilog HDL的难点之一,为了节约成本,码流播放器选择价格低、体积小、速度快、容量大的SDRAM,给Verilog程序编写增加了不少难度。相比控制简单的SRAM,DRAM每隔一段时间必须自刷新和预充,且数据线与行列地址都是复用的,切换读写时极容易出现时序上的偏差,出现写错,读错,重复读,丢数等等问题。

SDRAM上电复位后,计数器控制在200μs后,进行SDRAM初始化配置,对所有BANK进行预充,接着是多个Reflash,然后进入SDRAM工作模式设置。之后进入空闲状态,执行读写数据和自刷新等任务。

由于USB程序设置为Slave-FIFO模式,将FIFO的空满状态发送到FPGA,而FPGA作为Master,需要根据USB内FIFO的空满信号,综合SDRAM的空满状态,对读写状态进行判断,并给出读写使能。

3.2 USB收发器及控制器固件程序

赛普拉斯公司提供了非常好的程序框架,免去了用户自己编写一些通用性比较强、模式化的程序。在框架的基础上,用户只需在相应的地方写相应的代码即可完成USB工作。

码流传输因为数据量大,而且传输和接受数据上又没有带宽和间隔时间要求所以采用的是Bulk传输方式。

计算机和USB外设端点0(EP0)之间的传输是典型的控制传输,主要进行查询配置和给USB设备发送通用的命令;控制传输是双向传输,数据量通常较小,而且数据传送是无损性的。

3.3 CPLD动态加载配置程序

CPLD通过USB芯片,接收上位机传输过来的FPGA配置文件(.rbf格式),然后按照固定的时序对FPGA进行配置。需要注意的是,在动态加载过程中,FPGA的模式选择需配置为PS模式,不同的FPGA芯片之间配置模式略有不同,电位要求也不尽相同。

配置过程为:CPLD将nCONFIG置低再拉高来初始化配置;等待FPGA返回应答信号nSTATUS,检测到nSTATUS变高后,将配置数据和移位时钟分别送到DATA0和DCLK管脚;送完配置数据后,检测CONF_DONE是否变高,若未变高,说明配置失败,应该重新启动配置过程。在检测CONF_D ONE变高后,根据器件的定时参数再送一定数量(40个)的时钟到DCLK管脚;待FPGA初始化完毕后进入用户模式。

3.4 PC界面控制程序

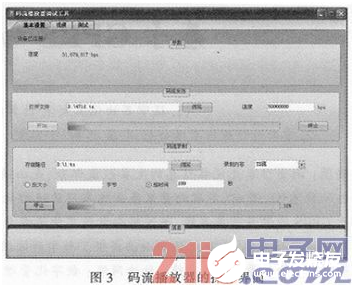

由C#编写的控制界面,主要实现与USB芯片间的码流传输,发送控制命令,接收码流分析结果等信息,如图3所示。

4 结论

码流播放器是USB供电,无需额外电源,轻巧方便携带;能轻松捕捉,播放,录制和分析码流;精确控制码流发送速度;全双工,同时进行码流的发送和接收。

用户界面简单明了。发送时选择发送文件,再输入发送速度,点击开始即可;接收时选择存储路径和录制内容,再选择录制方式,点击开始。同时,用户界面还能实时接收到FPGA分析得到的各种码流参数信息。目前,本文所介绍的码流播放器已进入稳定性测试阶段,各项功能也在不断完善和优化中。

码流播放器的电路板仅为6 mm*9 mm,小巧轻便,方便携带;操作简单,界面友好;因为设计时严格控制成本,价格低廉,性价比高,是数字电视专业人员理想的测试工具。

-

ASI信号和SDI信号的区别2024-08-20 7833

-

基于RT-thread柿饼派实现一个网络音频流播放器的设计2022-09-21 2641

-

基于RT-thread柿饼派实现一个网络音频流播放器设计2022-04-20 2456

-

基于FPGA的ASI/SDI码流播放器该怎么设计?2019-09-29 2667

-

多流媒体同步播放器ActiveX控件解析2017-11-01 1490

-

基于蓝牙车载的音频流播放器的设计2017-09-19 942

-

基于FPGA的ASI_SDI码流播放器的设计与实现2013-07-26 1510

-

蓝牙车载音频流播放器的设计2012-10-23 4459

-

csf文件播放器中文版2012-09-19 1900

-

高清硬盘播放器2009-12-22 3355

-

MPEG-2 TS流播放器 FOR WIN32的程序源码vl2009-02-25 2076

-

csf格式播放器-下载2008-12-26 2224

-

基于FPGA NiosII的MPEG-4视频播放器2008-10-09 2030

-

CSF文件播放器2007-06-10 5583

全部0条评论

快来发表一下你的评论吧 !