知存科技数模混合存算一体AI芯片专利解析

电子说

描述

知存科技的该项专利是关于数模混合存算一体芯片技术,除能有效降低设计复杂度和制造成本外,还特别适用于人工智能神经网络的运算。

集微网消息,近年来,存算一体芯片架构开始得到人们的广泛关注与研究,尤其是在AI快速发展的时代,人们对这种架构的需求也越来越多。近期,新兴独角兽存算一体芯片公司——“知存科技”就获得了近亿元人民币的A轮融资,此次融资主要用来完成“存算一体”新品的量产。

传统存算一体芯片架构的基本思想是通过在存储器中内置逻辑计算单元,从而把一些简单但数据量又很大的逻辑计算功能放在存储器中完成,以减少存储器与处理器之间的数据传输量以及传输距离。但随着人工智能技术的迅速发展,神经网络作为人工智能中的主要技术分支得到了广泛的应用,各种神经网络算法层出不穷。但是,当前实现神经网络算法主要依赖于计算机或大规模的处理器,使得终端设备体积受限、成本较高,不利于神经网络的推广应用。

为了解决以上问题,知存科技申请了一项名为“一种数模混合存算一体芯片以及用于神经网络的运算装置”的实用新型专利(申请号:201821979648.8),申请人为北京知存科技有限公司。

该专利提出的数模混合存算一体芯片能有效降低设计复杂度和制造成本,利于大规模产业化,并增加了设计的灵活性,延长闪存的使用寿命,可以用于神经网络运算等场合。

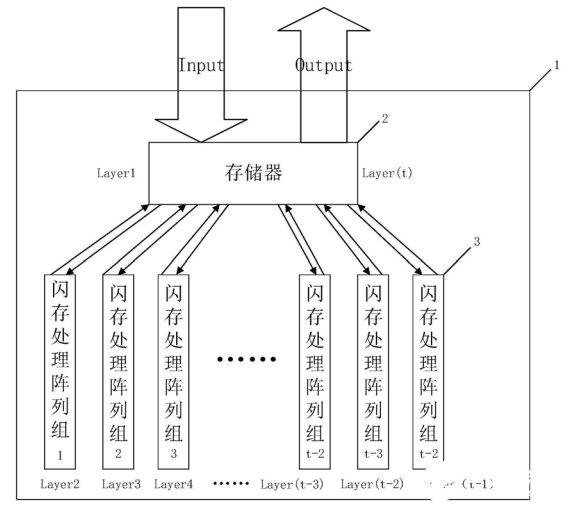

图1

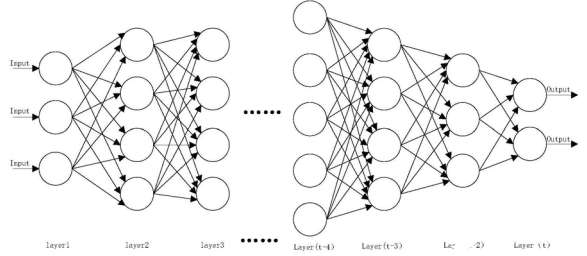

图2

图1为利用本实用新型实例一种数模混合存算一体芯片实现图2所示神经网络运算的系统图。如图1所示,该存算一体芯片1包括:片上存储器2以及多个闪存处理阵列。

其中,片上存储器用于实现图2所示的Layer1和Layer(t)层,即接收从外部设备传来的待处理数据并将Layer(t-1)层得到的运算结果进行输出,在此基础上,该片上存储器还用于存储各个闪存处理阵列的待处理数据。然后对多个闪存处理阵列进行分组,得到t-2个闪存处理阵列组,其中,每个闪存处理阵列都用于实现神经网络中部分神经元的运算,并将运算结果存储于片上存储器。第1闪存处理阵列组~第t-2闪存处理阵列组分别用于实现图2中示出的Layer2~Layer(t-1) 层。

当图中所示的神经网络为训练合格的神经网络时,该存算一体芯片可以用于这个模型的应用,即根据训练合格的神经网络的权重参数,设置各可编程半导体器件的阈值电压,然后将待处理数据输入至该数模混合存算一体芯片进行运算,即可实现神经网络的前向传播应用过程,而最终运算结果将作为实际结果用于后续流程使用。

当该神经网络为未合格的神经网络时,需要对该神经网络进行训练,此时,该存算一体芯片也能适应模型训练需求。该芯片将最终结果输出至外部设备,外部设备对该最终结果进行判断,若满足要求,则神经网络训练合格,若不满足需求,还需要利用此芯片中的控制器、编程电路配合,调节各可编程半导体器件的阈值电压,实现对神经网络参数的反向调节,之后再将训练数据输入至网络进行正向传播,再进行反向调节,如此反复操作,即可完成模型训练的整个流程。

通过上述分析可知,本专利所提出的数模混合存算一体芯片不仅适用于已训练好的成熟的神经网络模型的应用,还适于神经网络模型的训练过程,其适用性较好。而且集成度高、体积小,利于在电子设备中集成,极大降低了神经网络运算的硬件成本,通过在芯片内部集成片上存储器,还可以减少与芯片外部设备的交互。

“存算一体”架构的芯片打破了传统的冯诺依曼架构(存储器和处理器分离),知存科技在“存算一体”架构的基础上,又实现了神经网络计算的功能,为“存算一体”芯片的发展又推动了一步,希望该此类芯片量产后可以尽快的投入到市场中,为人工智能的发展做出更大的努力。

-

知存科技助力AI应用落地:WTMDK2101-ZT1评估板实地评测与性能揭秘2024-05-16 913

-

知存科技完成亿元A+轮融资用于存算一体芯片的量产2020-10-22 4411

-

知存科技:多款存算一体芯片已批量试产2020-12-02 6957

-

存算一体大算力AI芯片将逐渐走向落地应用2022-05-31 6591

-

存算一体技术路线如何选2022-06-21 10977

-

存算一体芯片在可穿戴设备市场有哪些机会2022-10-14 1755

-

2023年存算一体是芯片设计的技术趋势2023-01-13 3384

-

特斯拉的下一代AI芯片:存算一体2023-03-09 3492

-

知存科技再推存算一体芯片,用AI技术推动助听器智能化2023-03-10 4684

-

【AI简报20230310】知存科技再推存算一体芯片、微软:多模态大模型GPT-4就在下周2023-03-12 3559

-

展示存算一体商用赋能 知存科技参展2023WAIC亮点回顾2023-07-08 1146

-

存算一体芯片的技术壁垒2023-09-22 2683

-

存算一体芯片新突破!清华大学研制出首颗存算一体芯片2023-10-11 2174

-

浅谈为AI大算力而生的存算-体芯片2023-12-06 962

-

知存科技王绍迪:AI可穿戴需求爆发,存算一体成主流AI芯片架构2025-12-23 10594

全部0条评论

快来发表一下你的评论吧 !