如何在基于NAND闪存系统中实现最低的故障率

存储技术

描述

(文章来源:海派世通)

随着NAND闪存的工艺几何尺寸缩小,误码率不断增加,从而导致系统故障率降低。任何了解SD卡,USB闪存驱动器和其他基于NAND闪存的解决方案基础知识的人都知道,控制这些最小化故障率的关键组件是NAND闪存控制器。您可能熟悉此组件并讨论过纠错码(ECC)强度。是否想过在这个小包装里面究竟出现什么?闪存控制器为防止故障发生做了什么? ECC是一组不同构建块当中的一个单元。系统设计相当良好,其可靠性和防错功能在整个进程阵列中交错,包括用于不可避免的位错误的ECC。

甚至在系统组装之前,无论是在内部还是通过系统集成商,都有一个重要的规划标准进入闪存认证。换句话说,闪存控制器应该与正确的闪存策略配对。那么资格认定究竟是什么意思呢?资格认证不仅意味着控制器将使用选定的闪存。最重要的是,它意味着测试,而且不仅仅是少数。在海派世通,我们确保组合已经彻底测试过。首先是表征闪存本身。通过不同使用情况在所有生命周期阶段中广泛测试NAND闪存来完成表征。该知识有助于正确设计纠错单元,提取用于纠错的软解码的对数似然比(LLR)表,并实现最有效的整体错误恢复流程。

在规划设计时,大多数公司会讨论与总体成本相关的闪存,但许多人忘记考虑闪存的行为,因为它们的体系结构,环境和它们所暴露的用例。每种方案都需要独特的处理,校正和恢复选项,以实现最佳结果。这种表征活动非常重要,因为所有收集的数据都能够以最准确和最有效的方式验证工具。复杂且经过深思熟虑的资格认证是稳健和稳定系统的基础工作。对于要求苛刻的系统,与系统集成商一起质疑和讨论资格认证过程是值得的。或者,如果内部设计解决方案以获得更大的灵活性,请直接向控制器公司咨询。虽然可靠的认证设置了成功的系统,但校准和控制器功能更像是直接的错误预防。

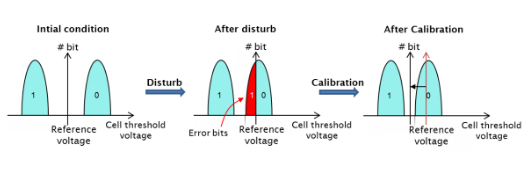

有效的校准过程可以在器件的整个寿命期间保持低误码率,同时动态地适应存储器单元中的阈值电压的变化。有许多干扰会影响电池的阈值电压:编程和擦除循环,读取干扰,数据保留温度变化等。闪存不会自动跟踪阈值变化。相反,闪存控制器会决定何时需要校准并执行合适的操作序列。

如下所述,校准改变了电池的参考电压。由于不同的块或页面可能会遇到不同的干扰,因此一页的最佳校准不一定适用于另一页。

此外,诸如磨损均衡,读干扰管理,迹近错失ECC和动态数据刷新之类的错误预防机制协同工作,以管理数据到闪存上有效和可靠的传输。磨损均衡可确保闪存或存储系统中的所有块同时接近其定义的擦除周期预算,而不是之前接近它的某些块。迹近错失ECC刷新应用程序读取的所有数据超过配置的错误阈值,而动态数据刷新扫描读取所有数据并将所有块的错误状态标识为后台操作。这些功能通常由不同的控制器公司以不同的方式命名,并最终以其背后的逻辑和算法为目标,同时针对共同的目标,以不同的方式达到它人们应该与他们的控制器公司建立密切的关系,以便了解这些功能如何与合格的闪光灯协同工作。

最后,纠错已经成为闪存控制器中最着名和最重要的任务之一,而错误预防应该在其价值方面承担更多的重量,错误纠正的复杂性和强度最终使它成为最有价值的蛋糕控制器的机制。在考虑面积和功率限制时,纠错编码变得越来越困难。随着对纠错能力的需求不断增加,旧代码不再能够基于最新闪存中可用的有限备用区域来提供所需的校正性能。

为了提供最佳解决方案,海派世通开发了自己的纠错引擎,这是一种基于广义级联码的硬判决和软判决纠错模块。该代码构造提供的巨大优势在于一个特定方面:可以分析地确定每个代码字中的可校正错误的数量。这意味着对于每个码字,纠错可以保证一定程度的校正性能。对于所有可用的闪存,指定了保证误码率,可以保证在指定参数内的可靠操作。

当数据从闪存中读回并传递到纠错模块时,判断哪些位错误仅基于添加到码字中的冗余信息。仅使用此信息意味着对于每个比特,它同样可能是正确的或不正确的。使用所谓的软信息考虑概率,其指示接收的比特是接收的比特的可能性或者是否是另一个值的可能性。这些概率取自所谓的对数似然表,这些表已经生成并且已经存储在控制器中的查找表中。使用该信息,纠错现在具有更多输入:对于每个单独的比特,概率信息现在指示该比特被接收的可能性,例如,收到零,有74%的信心,原始值为零。纠错具有明确的指示,哪些位可能是错误的,哪些位不太可能是错误的。该附加信息显着增加了纠错的纠正能力。

闪存控制器是确保闪存可靠和安全处理的关键组件。它们处理一系列功能,旨在有效地管理闪存上的数据传输,并且不仅可以进行纠错,还可以防止错误。但是,这些功能都是以不同的方式设计,并且取决于公司的业务模式和重点,您的控制器可以做到最低限度。在海派世通,我们称之为高质量的功能,机制和复杂过程,旨在提高FlashXE?eXtendedEndurance生态系统的耐用性,从而提高闪存的可靠性。

(责任编辑:fqj)

-

降低UPS电源故障率 电池组寿命的要点2014-02-13 1337

-

ADC08B200的故障率是多少?2024-12-27 389

-

电子行业有没有行业故障率标准2016-11-14 25496

-

NAND闪存存储系统的低故障率如何实现?2019-08-01 1735

-

NOR闪存/NAND闪存是什么意思2010-03-24 9080

-

降低流量计故障率的方法及目的介绍2017-09-30 955

-

MacBook键盘故障率奇高,你遇到了吗?2018-06-14 6975

-

一文解析NAND闪存存储系统中实现低故障率不仅需要强大的ECC代码2019-06-07 4500

-

如何在基于NAND闪存的系统中实现最低的故障率?2019-07-05 2817

-

Backblaze发布2019年度硬盘故障率报告 这款硬盘年化故障率为零2020-02-13 9560

-

评估残余故障率λRF、传感器、单点故障率λSPF和单点故障度量MSPFM的方法2020-10-22 4827

-

NAND闪存的应用中的磨损均衡2022-10-24 2553

-

降低UPS电源总故障率的关键因素2023-11-15 553

-

磁环共模电感器应用中故障率高的原因2024-01-22 497

-

电力电容器运行故障率偏高的原因2024-08-13 1840

全部0条评论

快来发表一下你的评论吧 !