PIC单片机驱动LCD模块的设计

控制/MCU

描述

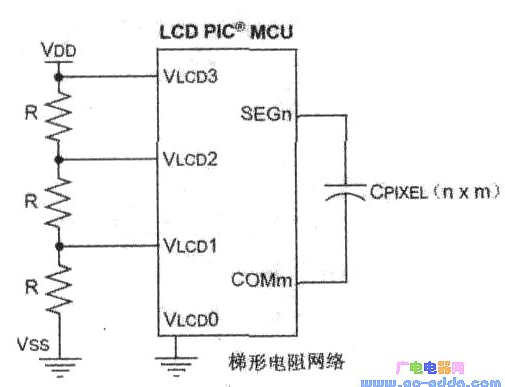

偏置电压是通过使用外部梯形电阻网络(电路见下图)而产生。因为梯形电阻网络连接在VDD和Vss之间,所以会有电流通过梯形电阻网络,电流大小与电阻成反比。也就是说,电阻越大,通过梯形电阻网络的电流就越小。如果使用10kΩ电阻,且VDD=5V,则梯形电阻网络将不断消耗166μA的电流。这对于一些使用电池供电的应用来说是很大的电流。

如何最大程度增大电阻,而又不会对显示质量产生负面影响?一些基本的电路分析可以帮助确定梯形网络中电阻增大的程度。

LCD模块实际上就是一个模拟多路开关,它交替地将LCD电压连接到各个段和公共引脚(段电极和公共电极交叉于每一个LCD像素点)。LCD像素可用电容进行模拟。梯形电阻网络中的每个分接点可以用戴维南(Thevenin)等效电路进行模拟。对于VLCD3和VLCD0,戴维南电阻为0;如它不为0的两种情况,即对于VLCD2和VLCD1。

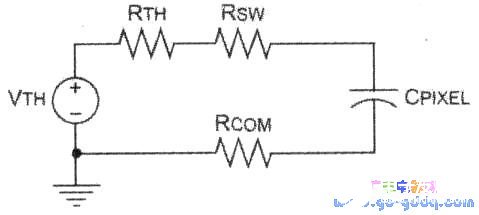

电路可以简化为如下图所示的电路。

RSW是段多路开关的电阻;RCOM是公共多路开关的电阻。

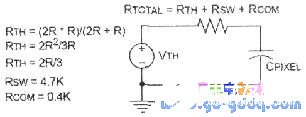

对于戴维南电阻不为0的情况,戴维南电压等于2/3 VDD或1/3 VDD。戴维南电阻等于梯形电阻网络上部和下部的串联电阻,其估算电阻的等效电路见右图所示。

例如.可以用RC电路来模拟单个像素的驱动器,在该电路中电压在0V~VLCD2之间切换。对于LCD和PIC单片机,可以估算段和公共开关电路的电阻分别大约为4.7kΩ和0.4kΩ。可以看到,经过像素的电压从0变为VTH的时间将取决于像素的电容和总电阻,而梯形电阻网络戴维南电阻构成了总电阻最主要的部分。

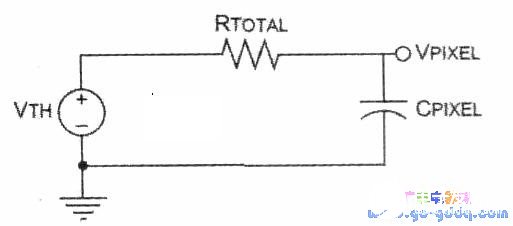

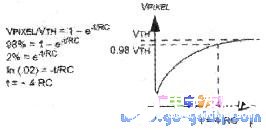

经过像素(等效电路见下图所示)的电压的阶跃响应遵循以下公式:

通过处理公式.可以看到,像素电压达到偏置电压98%所需的时间等于4个时间常数(其阶跃响应见左图)。

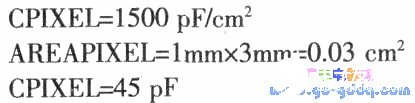

现在,需要估算电容。电容大小正比于像素的面积。我们可以测量像素的面积,并根据以下公式估算电容。很显然,较大的显示器(如数字墙钟)将具有较大的像素和较高的电容。

希望时间常数远小于LCD驱动波形的周期,以便最大程度地减少在VPIXEL上升到VTH的时间段内出现一个以上的LCD驱动波形的可能性。如果希望RC等于100μs,那么总电阻可以根据以下公式计算:

RTOTAL=l00μs/45pF=2.22MΩ

RTH=2.22MΩ-5.1kΩ≈2.2MΩ

LCD模块内的开关电路电阻相对于该电阻来说很小,所以梯形电阻网络在VLCD2和VLCD1时的戴维南电阻可以视为就是RTOTAL。然后,可以计算R的值,从而得到正确的戴维南电阻。

R=3RTH/2=3.3MΩ

现在.可以计算通过梯形电阻网络的电流(假设使用3.3MΩ的电阻)。

RLADDER=9.9MΩ,ILADDER=5V/9.9M=0.5μA

使用该过程估算梯形电阻网络的最大电阻值,将可以显着降低LCD应用的功耗。不要忘记观察显示屏在其工作条件下(如温度、电压,甚至是湿度)的显示情况.以确保对比度和显示质量良好。

责任编辑;zl

-

PIC单片机实现LCD1602滚动显示字符串2021-11-16 1251

-

51单片机驱动超声波测距模块2021-07-22 2007

-

PIC单片机驱动LCD段驱动器的设计2019-12-19 2045

-

PIC单片机对清洁护理机的设计2018-11-30 1733

-

美国微芯科技推出PIC16F946 PIC®单片机,可满足对LCD段数的不同需求2018-09-27 2923

-

Microchip超低功耗LCD单片机PIC18F87K902018-06-08 6481

-

PIC单片机简介2017-11-22 8210

-

PIC中档单片机系列-LCD2017-10-16 948

-

PIC单片机教程_PIC单片机学习要点2012-06-28 16734

-

PIC单片机复位系统模块介绍2011-06-23 2737

-

PIC单片机定时器模块应用2011-03-03 977

-

PIC单片机概述2010-12-19 827

-

基于PIC18F458单片机的LCD显示2009-10-16 2486

-

PIC单片机基础知识2009-01-18 1427

全部0条评论

快来发表一下你的评论吧 !