福建晋华随机动态处理存储器元件的形成方法专利

电子说

描述

福建晋华目前只专注于DRAM 的制造,虽然相对于国外半导体存储三巨头而言,技术在某些方面会有不足,但是从16年成立至今,短短三年内,就已经达到DRAM技术的较高水平,其实力仍不容小觑。

集微网消息,现如今全球范围内的半导体存储行业已经形成了三星、SK海力士和镁光三足鼎立之势,而放眼国内,福建晋华、兆易创新、紫光集团等企业也逐渐开始抗起我国半导体存储行业的大旗。

随着各种电子产品朝小型化发展的趋势,动态随机存取存储器(dynamic randomaccess memory ,DRAM)单元的设计也必须符合高集成度及高密度的要求。对于具备凹入式栅极结构的DRAM单元而言,由于它可以在相同的半导体基底内获得更长的载流子通道长度,进而减少电容结构的漏电情形产生,因此在目前主流发展趋势下,具备凹入式栅极结构的DRAM单元已逐渐取代仅具备平面栅极结构的DRAM单元。

然而,受限于制作工艺技术之故,现有具备凹入式栅极结构的DRAM单元仍存在有许多缺陷,还待进一步改良并有效提升相关存储器元件的效能及可靠度。

为了解决这一问题,早在2016年福建晋华就申请了一项名为“动态随机存取存储器元件的形成方法”的发明专利(申请号:201611198384 .8),申请人为福建省晋华集成电路有限公司。

该专利提供了一种随机动态处理存储器元件的形成方法,主要是利用单一制作工艺在其位线内形成密度高且厚度较小的阻障层,所以,该方法可以在制作工艺简化的前提下降低阻障层的阻值。

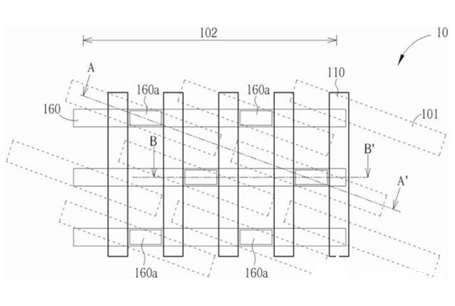

图1

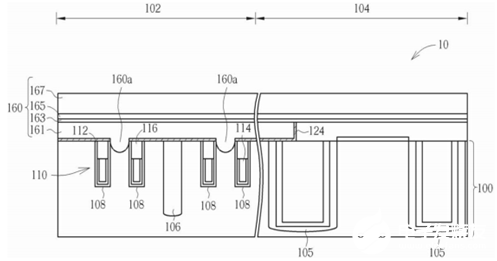

图2

上图1是该专利中提出的动态随机存取存储器元件10,图2是图1中沿着切线B-B’的剖面示意图。由上面两图我们可以看到,该专利提出的动态随机存取存储器元件10主要包括:基底100、存储区(记忆体区) 102、周边区104、字线(字符线)110以及位线160。

一般来说,基底100由硅基底、含硅基底(如SiC、SiGe)或硅覆绝缘(silicon-on-insulator ,SOI)基底等构成。除了存储区102和周边区104均置在了基底100上面之外,基底100上还形成有多个主动区(active area ,AA)101,相互平行地沿着第一方向延伸。另外其内部还形成有多个埋藏式栅极114,埋藏式栅极114是相互平行地沿着第二方向延伸,并横跨第一方向。

此外,基底100上还有多个位线160,其主要在埋藏式栅极114上产生,且它们相互平行地沿着第三方向延伸,并同时横跨主动区101与字线110,如图1所示。位线160与字线110之间通过位线接触插塞(bit line contact ,BLC)160a来电连接至各该晶体管元件的源极/漏极区,并且位线接触插塞160a位于两字线110之间。

在该专利提出的方法是利用射频物理气相沉积制作工艺来形成位线160的阻障层163,使其具有双层结构,这样就降低了阻碍层的厚度,使位线160具有较低的阻值与较小的整体厚度。另一方面,阻障层163虽然具有双层结构,但其整体厚度仅介于40埃至50埃之间,因而可以很好地改善位线160的高度并且简化了制作工艺。

福建晋华目前只专注于DRAM 的制造,虽然相对于国外半导体存储三巨头而言,技术在某些方面会有不足,但是从16年成立至今,短短三年内,就已经达到DRAM技术的较高水平,其实力仍不容小觑。

-

内存储器分为随机存储器和什么2024-10-14 4924

-

福建晋华获无罪判决,美光与福建晋华达成全球和解2024-02-29 1342

-

浅析动态随机存储器DRAM集成工艺2023-02-08 1598

-

如何辨别SRAM是否属于动态随机存储器2022-02-07 683

-

SRAM随机存储器的特点及结构2020-04-30 4073

-

从晋华事件剖析我国存储芯片产业瓶颈2018-11-20 6670

-

联电为何突然宣布暂停协助福建晋华2018-11-06 4799

-

福建晋华成了第二个中兴,福建晋华与美光恩怨未了2018-10-31 12989

-

美国对福建晋华有限公司实施禁售令,福建晋华将成为第二个中兴2018-10-30 3720

全部0条评论

快来发表一下你的评论吧 !