NVMe时代的全闪存阵列有哪些变和没变

存储技术

描述

根据2018年底IDC发布的报告“Data Age 2025:The Digitization of the World From Edge to Core”显示,伴随5G/IoT和车联网等新兴技术落地,越来越多的终端以及越来越高的带宽催生越来越多的数据产生,到2025年,全球将每年产生约175ZB数据;同时随着大数据/AI技术的广泛应用,数据的价值得到更加充分的挖掘,被存储和被分析的数据量指数增长。

另一方面,相比机械盘(HDD),基于NAND Flash介质的SSD可提供更高性能、更高密度、更低能耗,随着技术不断进度,成本进一步下降,已经被市场广泛接受,发货量超过HDD;传统针对HDD盘设计的SATA/SAS接口,无法充分发挥SSD的性能潜力,针对SSD设计的NVMe标准接口一经出现,便展现了强大生命力。根据2019年全球闪存峰会(Flash Memory Summit,FMS)的预测,2020年将有50%以上的服务器,40%以上的阵列支持NVMe SSD,NVMe将很快超过SATA/SAS成为SSD使用的主流存储接口,宣告NVMe时代的到来。

应用数据量和数据热度同时增加,对于存储系统的设计提出了新的挑战,使用NVMe SSD构建的全闪存存储系统成为业界共识,而如何构建各自又有不同的理解。本文对这个问题做一个粗浅的探讨。

全闪系统的性能指标,低时延比高IOPS更为关键。降低时延,关键是缩短IO路径,提升IO路径的处理效率。在系统设计选择上,要求针对NVMe特点做出新的调整。

为达到更低的IO时延和更高的效率,前端支持NVMe over Fabric是必选。后端NVMe SSD的组网可在PCIe和NVMe over Fabric(FC或RoCE)之间选择,PCIe时延为亚微秒,但扩展能力比较局限;NVMe over Fabric扩展能力强,而时延则在10微秒级。

NVMe SSD单盘性能相当强大(100k iops),控制器往往构成系统性能瓶颈,串接盘柜的扩容方式,只能增加容量,并不能带来性能的增长,因此,全闪系统应考虑scale-out的架构。 从降低时延的角度,数据的跨控制器转发应尽量避免。但为了提供数据跨控制器冗余,或者提升单对象多控制器并发访问能力,又要求数据在不同控制器之间转发,一个系统需要在有冲突的多个需求间寻求平衡。

而另一方面,无论技术如何发展,高可用性是对存储系统的一贯要求,对于更多承担关键业务的全NVMe闪存系统来说,高可用性更是一个不容让步的目标。Scale-out系统有了更多的硬件部件,合适的架构可以达成相比双控阵列更高的可用性,而不合适的架构选择可能形成整体串联的可靠性模型,反而降低了系统的可用性,这是系统设计者和用户都值得注意的。

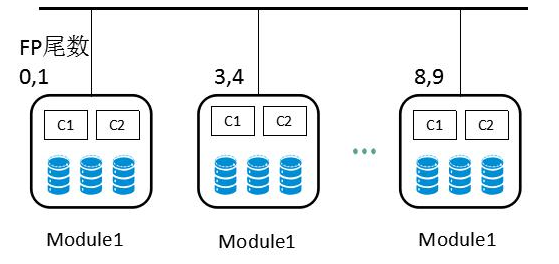

例如一些系统为追求全局去重效果,将所有的数据按其指纹的HASH来确定数据存储和处理的模块,这种设计不仅在正常工作时存在大量的模块间数据转发,更为严重的是,在单个模块故障后,可能导致全系统数据不可用(如图1,不同模块处理不同尾数的指纹。例如Module1故障后,所有指纹尾数是0、1的数据将不可用,从而整个系统不可用);这种系统的可用性模型是各模块的串联,假设单个模块可用性是5个9,全系统可用性必然低于5个9。

图 1 按模块处理指纹的全局去重设计示意

中兴通讯基于多年存储研发技术的积累,全新发布全NVMe全闪存阵列KF8200。秉承一贯脚踏实地的风格,以系统可靠稳定为基石,同时积极拥抱技术最新发展,在软硬件架构上全面创新,KF8200成为全NVMe时代中兴通讯存储的旗舰产品。

图 2 ZXCLOUD KF8200全NVMe闪存阵列

全系统由一个或多个双控机柜通过RoCE网络连接,组成一个scale-out系统。每个双控机柜都可以提供NVMe over Fabric访问接口;单机柜支持30块NVMe SSD,可提供超过200w IOPS以及亚ms的响应时间。

所有NVMe SSD都位于控制器柜中,通过PCIe直接与控制器相连,避免了复杂的后端组网,硬件设计上保证极低时延;软件上,数据冗余使用机柜内专用通道在机柜内双控间完成,避免了机柜间数据转发导致的时延;数据分布策略设计上,做到了系统正常工作时,基本无跨模块数据转发,IO数据路径做到业界最短。

由于消除了正常工作时模块间数据转发,基本实现了真正意义上的scale-out,即性能和容量都随着节点(以机柜为单位)增加而线性增加。各个节点间正常工作状态呈现为松耦合,而在异常发生时各节点业务又可以互为倒换,在可靠性和性能二者之间达成较为理想的均衡。

责任编辑:ct

-

中国全闪存市场有哪些特点与趋势?2024-01-03 2389

-

HK-ATTO 光纤通道卡利用FC-NVMe 提升全闪存存储阵列性能2023-09-21 1586

-

Brocade Fabric技术与Kaminario K2全闪存阵列验证测试报告2023-08-30 488

-

Dell EMC正在建立比NetApp更大的全闪存阵列收入领先优势2021-04-01 3926

-

数据中心如何一步一步接纳NVMe2020-12-25 1225

-

全闪存阵列来袭 NVMe SSD该如何准备2019-05-06 5244

-

NVMe能否发挥更大价值,全闪存阵列的架构是关键2019-03-22 4790

-

IBM大波存储阵列新增对NVMe-oF的支持2018-11-05 4632

-

NVMe全闪存阵列产品PowerMax,目前全球速度最快的全闪存阵列2018-07-24 4140

-

选择全闪存阵列时需要咨询的12个关键问题2018-07-11 5154

-

HPE全闪存阵列市场份额遭遇下滑2018-06-14 3577

-

浅谈全闪存阵列市场发展的七大预测2018-05-04 1467

-

NetApp_全闪存阵列助力拍拍贷应对P2P市场新挑战2016-12-29 1014

-

SolidFire推面向云服务的全闪存阵列2012-03-10 1124

全部0条评论

快来发表一下你的评论吧 !