基于FPGA技术的LVDS传输模式如何实现PCIE接口卡设计

电子说

描述

提出了一种通过FPGA实现PCI-Express(简称PCIE)接口卡的方法,对LVDS信号以及PCIE接口技术进行了充分的研究,设计未采用FPGA自带的PCIE硬核,而是根据PCIE总线桥接芯片对接口时序直接控制,最大程度优化接口逻辑,提高接口传输速率和稳定性;试验中LVDS器件接收LVDS总线上大小为513(列)*512(行)*8(位)的渐变图像,像素时钟为15MHz,帧频率为10帧/s,并传输到FPGA控制部分,FPGA控制部分向PCIE接口发送中断并完成图像数据上传;文中详细讨论了不同模块的实现原理,完成了实际测试和分析,测试结果表明该设计性能稳定,可以实现PCIE接口卡高速数据通信。

随着电子技术的飞速发展,微处理器、存储器技术的不断革新,传统的并行总线PCI逐渐成为系统整体性能的瓶颈。新一代的PCIE总线是最新的总线接口标准,它变革了PCI总线并行传输的传输模式,采用高速串行双通道传输,克服了PCI总线传输速率以及传输带宽的固有缺陷,从本质上把接口的传输速率、稳定性提升到了一个新的台阶。本文提出了一种基于LVDS传输模式的PCIE接口卡设计,主控单元采用现场可编程门阵列FPGA完成,FPGA内部丰富灵活的设计资源和高效快速的设计流程足以完成接口设计工作,最大程度地提升了系统的可靠性。

1 、LVDS传输和PCIE总线

LVDS传输是一种低压差分的传输模式,是一种串行传输,可以点对点传输,也可以一点对多点传输,具有传输速率快、抗干扰能力强和传输距离远等优点,广泛应用于高速数据的长距离传输。传输线多采用双绞线,由于信号路径的对称性,使其对共模噪声具有良好的抗干扰性能。

PCIE总线是取代PCI总线的新一代I/O标准,无论是传输速率、传输带宽还是稳定性都是PCI总线无法比拟的。与PCI总线的并行传输模式不同,PCIE是一种基于SERDES技术的串行通信技术,数据传输由两对LVDS线对组成,一对负责接收,一对负责发送,采用点对点双通道高带宽传输,接口可以为每个设备分配独享的通道资源,充分保障所有连接设备的通道带宽,提高每个设备的通道传输率。最新的PCIE3.0其比特率可达8GT/s,同时包含发射器和接收器均衡、时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据保护性能。

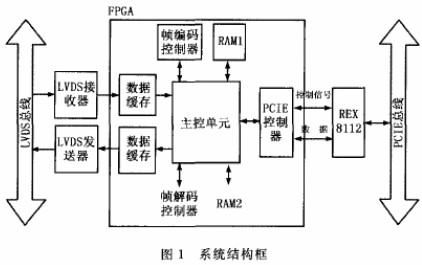

2 、系统总体框架

构成PCIE接口卡设计方案主要包括LVDS差分传输技术、FPGA硬件逻辑设计和PCIE接口技术。本设计是基于FPGA的PCIE接口卡设计,系统结构如图1所示,主要包含三部分:LVDS接口部分、以FPGA为核心的逻辑设计部分和桥接器件构成的PCIE接口控制部分。系统以FPGA为核心,通过LVDS接收器和发送器与LVDS总线相连,构成一个LVDS双向传输通道,同时利用PCIE桥接芯片PXE8112与PICE总线通信,实现LVDS总线与PCIE总线间的数据通信。本设计的主要功能是通过LVDS接收器接收LVDS总线上的图像数据,图像数据经过数据缓存后进行帧编码,然后以整帧的形式存储到FPGA内部的RAM1中,并向PCIE总线发送中断请求,要求上传数据;或者根据上位机的下传操作,FP-GA系统接收PCIE总线下传的图像数据或命令,进行帧解码后以整帧的形式存储到RAM2中,再经过数据缓存通过LVDS发送器输出到LVDS总线,实现LVDS总线与PCIE总线的双向通信。

3 、FPGA逻辑设计部分

可编程逻辑器件FPGA是一种方便快捷、高效稳定的嵌入式系统解决方案,以硬件描述语言完成电路设计,经过简单的综合与布局,快速烧制硬件电路,即可进行测试或开发,是现行电子设计的主流技术,其丰富的逻辑资源足以完成任何接口时序的逻辑控制。本设计所用的FPGA为Altera公司生产的Cyclone II系列的EP2C20F484I8N,采用硬件描述语言直接与PCIE桥接器件进行接口设计,代码设计精简,省去了不必要的中转等待周期,最大程度优化了接口卡的性能。FPGA逻辑设计部分包括主控单元、帧编/解码控制器、内部RAM和PCIE控制器。数据缓存部分用来缓存LVDS与FPGA间的数据传输,采用FPGA的IP核FIFO实现,两个内部RAM分别用来存储上传和下传的编/解码后的整帧图像,帧编码控制器用来给每帧图像添加特定的帧信息量,帧解码控制器则根据帧信息量解出原始图像,PCIE控制器用来控制PEX8112接口时序,进行PCIE总线与LVDS总线间图像和命令的通信。

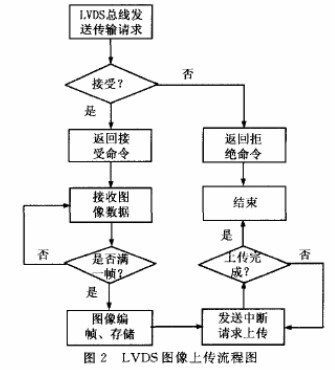

当LVDS总线上传图像时,首先会向FPGA主控单元发送传输请求信号,主控单元会根据FPGA运行状态返回一个接收或者拒绝的命令,发送接收命令后,FPGA开始准备接收图像数据,直到满一帧后进行编帧存储,并向PCIE接口发送中断信号请求上传,上传完成后结束该流程,流程图如图2所示。

4、 高速通信接口

LVDS差分接口采用MAX9247作为发送器,采用MAX9218作为接收器,完成图像数据的双向传输。MAX9247和MAX9218均为3.3V供电的LVDS接口芯片,芯片包含一路18位的图像数据传输通道和一路9位的命令传输通道,通过DE_IN管脚切换,图像通道最大转换速率630 Mbps。PCIE接口芯片采用PLX公司生产的PEX8112,PEX8112是一款PCIE接口的桥接芯片,利用PEX8112可以方便的将FP-GA、DSP等逻辑电路升级为PCIE接口,简化复杂的PCIE接口设计。PEX8112内部集成了单通道、全双工2.5 Gbps的PCIE端口,并提供完整的本地总线到PCIE接口,包括地址转换、包生产与解码、信号中断支持及并串转换等。

5 桥接电路通信

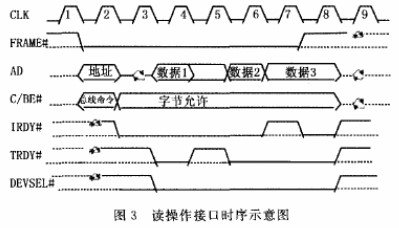

PCIE桥接器件PEX8112是FPGA系统与PCIE接口通信的桥梁,它负责图像数据和命令的双向通信。为提高PCIE接口传输速度和稳定性,可编程逻辑器件程序设计避免了不必要的等待周期,消除了因干扰等因素引起的接口冲突响应。当主设备(上位机)进行读操作时,FRAME#为低表示读操作开始进行,同时主设备下发读操作命令和地址,第二个周期为转换周期,主设备将总线的控制权交给从设备(FPGA系统),同时IRDY#(主设备准备好信号)信号置为有效,从第三个周期开始进行数据上传,从设备将DEVSEL#(从设备被选择信号)置为有效,每当TRDY#(从设备准备好信号)和IRDY#同时有效都意味着数据总线上存在着一个有效数据,TRDY#和IRDY#不同时有效视为等待周期,当FRAME#无效表示正在传输最后一个有效数据,读操作接口时序示意图如图3所示。

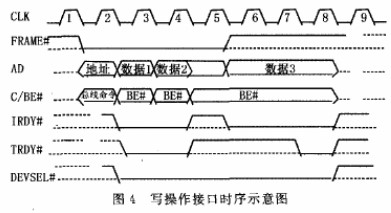

在写操作过程中,由于主设备无需对总线控制权进行转让,所以没有转换周期,当FRAME#有效后数据总线传完地址后直接传输有效数据,IRDY#或TRDY#无效视为插入等待周期,FRAME#无效表示正在传输最后一个有效数据,写操作接口时序示意图如图4所示。

6 、系统调试结果

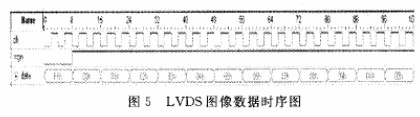

图5为在读操作过程中SignalTapII逻辑分析仪对LVDS总线的波形采集图,输入图像为513(列)*512(行)*8(位)的渐变图像,像素时钟为15MHz,vsyn为帧同步,高电平有效,data为8位图像数据,每两个像素点数值递增1。图6为上位机接收到的渐变图像,如图可见,图像大小为513(列)*512(行),每行图像由左及右逐渐变亮(渐变图像),与LVDS总线上的图像数据相符。上位机共接收到24帧渐变图像,每帧渐变图像均无异常。

7 、结论

本文提出了一种基于FPGA可编程逻辑器件的PCIE接口卡设计方案,在图像传输中采用LVDS高速差分传输接口作为图像数据通道,通过PCIE桥接器件保证了图像数据与PCIE总线的无缝传输,程序在设计过程中优化了时序逻辑,删除了不必要的等待周期,使整个系统的性能和稳定性得到了最大的提升,系统在数据采集、图像传输中有着广泛的应用前景。

责任编辑:gt

-

盘点 | ZLG致远电子PCle EtherCAT通讯接口卡2025-08-11 1173

-

如何去实现一种LonWorks接口卡的设计?求解2021-05-28 1518

-

哪些卡可以插在多媒体的接口卡上2019-08-21 2858

-

采用FPGA实现PCIe接口设计2019-05-21 4450

-

PCI接口卡中的DMA传输模块软硬件设计.pdf2013-07-21 3197

-

基于DSP与FPGA的ARINC429总线接口卡设计2013-03-12 1661

-

基于PCI总线的ARINC429接口卡设计2012-05-09 1466

-

基于FPGA的LVDS接口应用2012-01-11 1208

-

基于USB的多通道串行总线接口卡实现2011-09-08 1235

-

基于PowerPCA40的光纤通道接口卡设计2011-01-17 862

-

基于FPGA的IDE硬盘接口卡的实现2010-08-09 856

-

网络接口卡,什么是网络接口卡2010-04-03 2370

-

模块接口卡2010-01-07 912

-

基于FPGA 的IDE硬盘接口卡的实现2009-07-22 741

全部0条评论

快来发表一下你的评论吧 !