一种SpaceWire节点控制器实现方法全面介绍

控制/MCU

描述

0 引言

随着空间探测领域的逐渐扩大,航天器上的载荷设备对系统的数据通信需求也相应的越来越高。同时星载电子设备产生和待处理的数据总量迅猛增长,对数据总线处理能力提出更高的要求。数据总线的速度、可靠性和灵活性直接影响航天器的整体性能。欧洲航天局(European Space Agency,ESA)为满足航空航天应用提出了一种专门用于空间高速数据传输的点对点串行总线标准SpaceWire[1]。它具有数据率高,便于扩展,方便重复利用的特点,有利于航天器、卫星快速整合总装,这为航天器和卫星载荷的设计带来极大方便,应用前景广阔。

本文研究该标准下节点控制器IP[2]的实现方法,通过FPGA进行原型验证,最后在专用集成芯片龙芯1E300中实现了该节点控制器,实际测试信号传输率可达200 Mb/s~260 Mb/s。

1 系统总体设计

1.1 系统结构框图

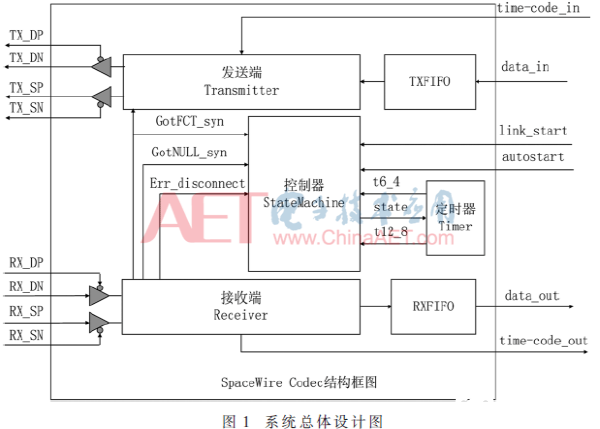

SpaceWire是一种点对点全双工串行数据传输协议,节点控制器在协议中主要负责解决数据包点对点传输问题。本文设计的SpaceWire IP核使用FIFO作为用户数据接口,并将数据发送和接收缓存包括在内。系统主要功能包括节点配置、链路状态控制和数据收发功能,总体设计如图1所示。

1.2 系统时钟域划分

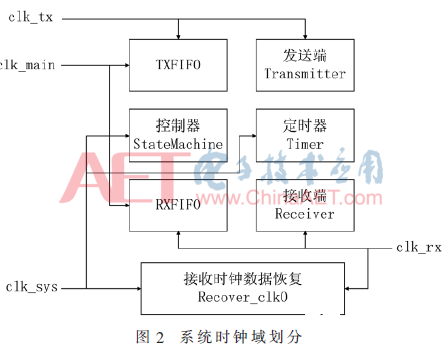

本设计必须使用到不同的时钟,系统时钟域的划分[3]是设计的重点之一。如图2所示,clk_sys是本设计中的频率最高的时钟域,同步系统控制器,并为系统提供定时功能。clk_main是来自上位机的时钟,同步发送缓存的写入和接收缓存的读取操作。clk_tx指的是发送时钟域,是同步发送端对发送数据的相关操作。clk_rx指的是恢复时钟域,是由链路数据进行时钟数据恢复所得到的时钟,用来同步接收端对恢复数据的相关操作。根据SpaceWire协议,接收端在接收到首位数据以前还没有产生恢复时钟,而链路断开检测在首位数据接收时就已经开始,这里采用系统时钟进行链路断开检测。

2 系统原理实现

2.1 系统状态机

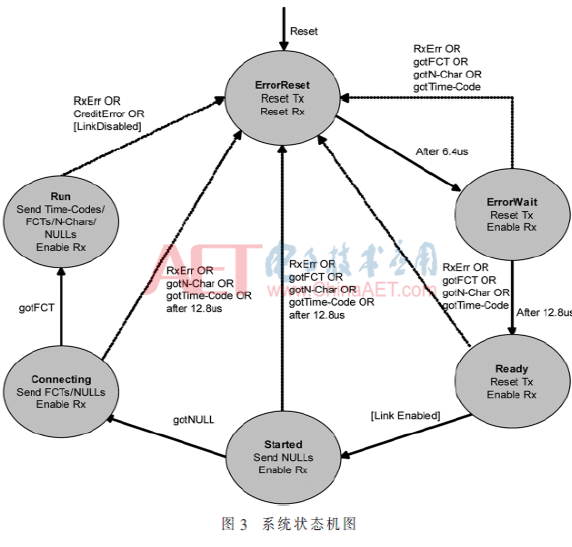

SpaceWire进行数据通信前要求两端的节点先通过NULL字符和FCT字符交换完成链路建立过程,链路在运行过程中可能由于链路主动或被动断开、数据传输错误等原因导致链路状态变化。链路运行的状态机如图3所示,图中实线表示链路初始化的过程,链路正确初始化后处于Run状态。在应用中,链路两端节点都可以被配置为主动或者被动模式[4],有如下条件:

Link_Enabled=(Not[Link_Disabled])And

([LinkStart] Or ([AutoStart] And gotNull))

2.2 发送端

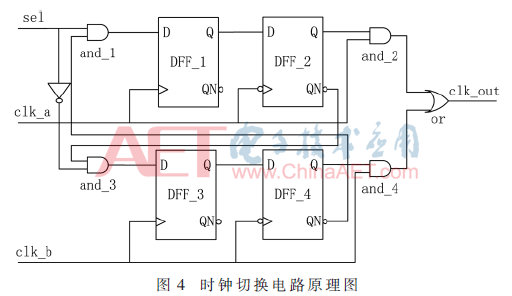

链路在初始化过程中,可能发送NULL字符和FCT字符,链路从初始化到运行的各个状态转换中,需要不间断发送字符。SpaceWire协议规定的链路初始化速率为10 Mb/s,而运行速率可以是2 Mb/s~400 Mb/s,故要求发送时钟速率可切换,发送端发送的比特流在数据发送频率变化的时候保持不间断,一种可用的时钟切换[5]电路图如图4所示。

DFF_2和DFF_4保证clk_a和clk_b时钟选择输出的变化都只发生在下降沿处,同时可以使得输出变化为某一时钟时,另一时钟的输出已经关闭,该方法可避免时钟切换时候产生毛刺。DFF_1和DFF_3分别加到and_1和and_3后面,防止sel、DFF_2输出和DFF_4输出的信号同时变化可能造成的DFF_2和DFF_4输出的亚稳态。

2.3 接收端

SpaceWire链路层采用DS编码方案,选通信号伴随着串行数据信号发送,接收端简单地通过异或数据和选通信号可以提取出时钟信号。该方法将接收偏差(skew)裕量从传统的时钟、数据方式的0.5比特时间提高到接近1比特时间,具有更好的抖动(jitter)容差。但由于接收数据的时钟是由接收的DS编码信号异或得到的,造成接收器的数据时钟信号不同步,恢复困难。

为实现数据时钟恢复,一种方法是基于Xilinx FPGA,选择采用可编程绝对延迟单元iodelay实现对DS异或后的信号执行指定的延迟,可以正确地恢复出时钟,根据图5分析DS信号的特点[6]后,得到一种更通用的方法:

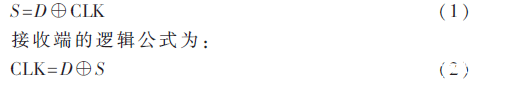

DS编码如式(1)和式(2)定义:

发送端的逻辑公式为:

式中D为数据信号,S为选通信号,CLK为数据时钟。根据DS信号变化的特点可以发现DS信号的每次转换有且只变换其中的1位信号,通过2次变换后则DS数据都将发生翻转,右图能够更清楚说明这一现象。

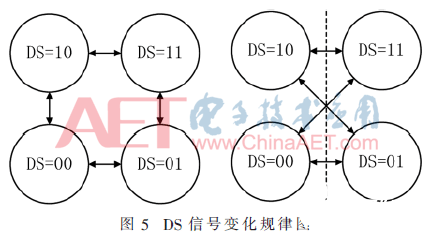

从图5可知,当且仅当时钟信号为上升沿时,data和strobe信号发生从同相至反相的跳变,如图5右半部分中右象限;同理,当且仅当时钟信号为下降沿时,data和strobe信号发生从反相至同相的跳变,如图5右半部分中左象限。根据上述分析结论设计的DS数据时钟恢复电路[7]如图6所示。

图6中电路由异或门、锁存器、触发器构成,当时钟信号为上升沿时,同相状态的data数据将保持不变,当时钟信号为下降沿时,反相状态的data数据将保持不变,从而保证了后级触发器时钟跳变时,触发器数据信号的建立时间。触发器输出的2位数据即是同步接收的数据信号,输出至后级接收模块进行处理。

2.4 数据缓存

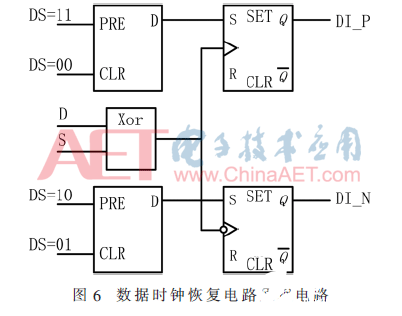

根据SpaceWire字符层定义,协议链路可能传送5种字符和2种控制码,其格式如图7所示。

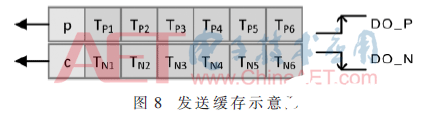

由于最长的时间控制码字符包含14比特位,本设计中发送方采用2组7比特位数据缓存完成数据格式的转换,采用DDR数据传输方式在时钟的上升沿和下降沿分别发送其中的一组缓存数据,如图8所示。在上次数据发送完成前的第二个时钟周期计算校验位,前一个时钟周期向该发送缓存填充待发送字符后进行数据发送。接收方采用5对移位寄存器组,首先判定接收字符的起始位置,在进行奇偶校验的同时,判别接收的字符类型,并保存至接收FIFO中。

图7和图8中标识为“p”或下标为“p”的比特位表示该位为字符的校验位,标识为“c”或下标为“c”的比特位表示该位为字符的控制位,箭头表示字符中比特位在链路上传输的先后顺序。

2.5 流量控制机制

为避免因主机接收缓存溢出而导致的数据丢失,链路的一端(B端)向另一端(A端)发送FCT表示B端已经准备好,可以再接收一定量的数据。

2.5.1 信誉量计数值

发送端要维护一个授权它可发送的N-Char数量的信誉计数值(Credit Count),具体如下。

ErrorReset状态下,信誉计数值为零,链路接口每接收到一个FCT,信誉量计数值就加8[8],每发送一个N-Char,信誉计数值就减1。信誉计数值为零时将停止发送N-Char,但可继续发送L-Char,直到它再次接收到FCT使信誉计数增长到8。

信誉量计数最大值根据接收缓存的大小设置(1个FCT对应接收缓存中8个N-Char的存储空间),不超过56(即7个FCT)。当信誉计数值达到或已经接近其最大值(即距最大值小于8)时又接收到一个FCT,那么信誉计数值不会再增长,同时会通过标志报信誉额度错误。

2.5.2 未偿付计数值

链路接口要维护一个它预期接收但未偿付的N-Char数量的计数值(Outstanding Count),即它通过发送FCT请求要发送的数量,具体如下。

复位时,初始未偿付计数值为0,链路出错时,未偿付计数值被保存并在下次重启时加载为初始值,每发送完一个FCT,未偿付计数值就加8,每接收到一个N-Char,未偿付计数值就减1。未偿付计数值最大为56(即7个FCT)。除非未偿付计数器有余量多计8个未偿付N-Char,同时接收缓存有容纳这8个N-Char的空间,否则发送器不能发送FCT。

3 测试与验证

本系统FPGA选用Xilinx公司的Virtex 4系列 xc4vsx55作为主控芯片,使用Verilog语言编程[9]进行逻辑设计和验证,在FPGA上同时例化两个节点控制器,通过读写配置寄存器控制SpaceWire节点收发数据。从仿真结果可见,节点控制器实现了协议规定的链路初始化和数据传输功能,控制字符和数据在链路上的传输正确。

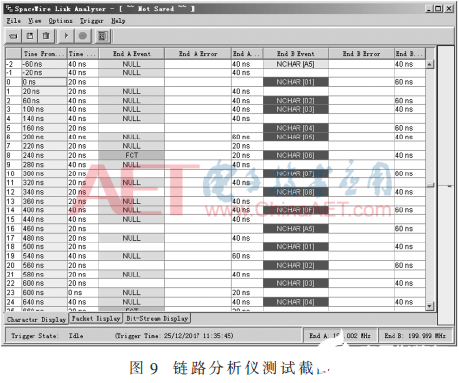

在专用集成芯片龙芯1E300中实现了该控制器,搭建测试环境,采用StarDundee公司的标准测试设备SpaceWire链路分析仪,与节点控制器芯片相互传输数据,验证了数据传输过程中的同步性和准确性。链路分析仪测试结果如图9所示,表明ASIC设计的节点控制器信号传输速率可达200 Mb/s,数据传输正常,满足协议规定的功能。

4 结束语

SpaceWire作为航天领域新兴的高速总线标准之一,具有数据率高、接口简单、扩展方便等诸多优点。本文提出的一种SpaceWire节点控制器实现方法解决了设计中多时钟域划分、数据时钟恢复、时钟切换和流量控制方面的难点。该设计方法经FPGA仿真验证正确,在专用集成芯片中成功实现,该节点控制器的研发设计具有较强的工程实用性。

参考文献

[1] ECSS,ECSS-E-ST-50-12C.SpaceWire-links,nodes,routers and networks[S].Noordwijk,The Netherlands:ESA-ESTEC Requirements & Standards Division,2003.

[2] JULIUSSON D.The swift codec development[C].Space-Wire-2013 Proceedings of the 5th International SpaceWire Conference.Gothenburg,Sweden:Space Technology Centre,University of Dundee,2013:316-318.

[3] 唐萍,李慧军.SpaceWire Codec接收端FPGA时序设计[J/OL]。微计算机信息,2009,25(2):178-179,198.

[4] CHRIS MCCLEMENTS,STEVE PARKES. SpaceWire standard:low speed signalling rates[C].SpaceWire-2008 Proceedings of the 2nd International SpaceWire Conference.Nara,Japan:Space Technology Centre,University of Dundee,2008:41-44.

[5] 魏家明.Verilog编程艺术[M]。北京:电子工业出版社,2014.

[6] NOMACHI M,ISHII S,KURODA Y,et al. Race condition free SpaceWire decoder for FPGA[C].SpaceWire-2010 Proceedings of the 3rd International SpaceWire Conference.St.Petersburg,Russia:Space Technology Centre,University of Dundee,2010:173-175.

[7] 闫梦婷,安军社,龚泉铭。基于RMAP机制的SpaceWire星载高速总线设计与实现[J]。电子技术应用,2016,42(1):108-110,114.

[8] 赵云富,吴一帆,孙强,等.SpaceWire总线的流量控制机制研究[J/OL]。微电子学与计算机,2016,33(1):1-5.

[9] 夏宇闻.Verilog数字系统设计(第4版)[M]。北京:北京航空航天大学出版社,2017.

- 相关推荐

- 热点推荐

- 节点控制器

-

组合逻辑控制器的基本概念、实现原理及设计方法2024-06-30 4386

-

一种点对点高速通信控制器的设计与实现2023-10-23 457

-

针对域控制器的一种升级测试方案介绍2022-08-01 1851

-

SpaceWire总线节点控制器接口电路2022-06-08 616

-

怎样去设计一种基于单片机的汽车车门节点控制器呢2022-02-23 1323

-

如何去设计并实现一种SDRAM控制器?2021-06-07 1792

-

如何去实现一种视频控制器的设计?2021-06-04 1680

-

一种简单的PID控制器调整方法2020-09-01 3367

-

全面了解车用电机控制器,从原理到设计!2020-06-22 4352

-

一种基于ARMCortex微控制器的相位差检测方法2017-09-26 822

-

一种MAC控制器设计方案2011-12-14 915

-

一种基于流水线的SpaceWire路由器研究2009-11-07 1621

-

一种简单的通用串行通信控制器2009-05-15 373

-

一种新型的模糊PID控制器介绍2009-04-10 539

全部0条评论

快来发表一下你的评论吧 !