关于FPGA芯片结构的简单介绍

可编程逻辑

描述

(文章来源:OFweek)

FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点

FPGA芯片主要由三部分组成,分别是IOE(input output element,输入输出单元)、LAB(logic array block,逻辑阵列块,对于Xilinx称之为可配置逻辑块CLB)和Interconnect(内部连接线)。

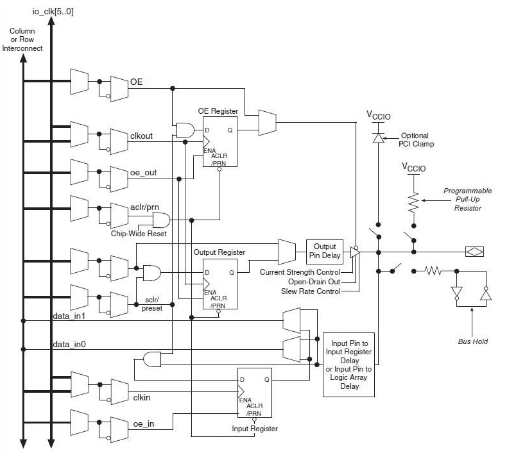

IOE是芯片与外部电路的物理接口,主要完成不同电气特性下输入/输出信号的驱动与匹配要求,比如从基本的LVTTL/LVCMOS接口到PCI/LVDS/RSDS甚至各种各样的差分接口,从5V兼容到3.3V/2.5V/1.8V/1.5V的电平接口,下面是ALTERA公司的Cyclone IV EP4CE115F29设备的IOE结构

FPGA的IOE按组分类,每组都能够独立地支持不同的I/O标准,通过软件的灵活配置,可匹配不同的电器标准与IO物理特性,而且可以调整驱动电流的大小,可以改变上/下拉电阻,Cyclone IV设备有8个IO blank(组),见下图:

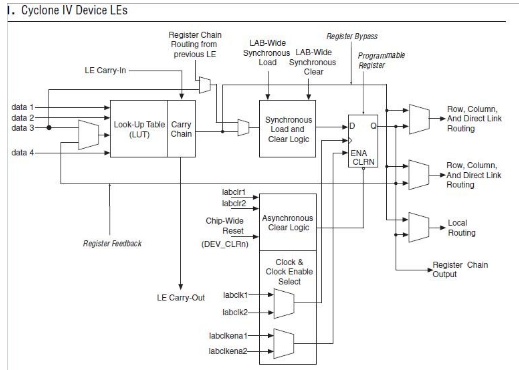

LAB是FPGA的基本逻辑单元,其实际的数量和特性依据所采用的器件的不同而不同,EP4CE115F29设备的每个LAB的布局包括16个LE、LAB控制信号、LE carry chains、Register chains和Local interconnect,其LAB结构图如下:

LE是Cyclone IV设备最小的逻辑单元,每个LE主要有LUT和寄存器组成的,

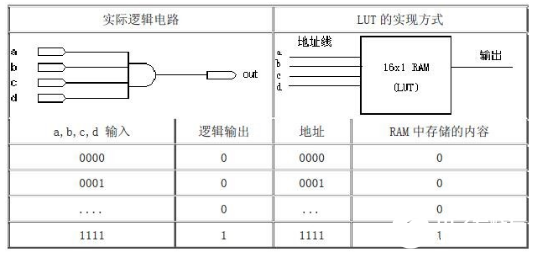

查找表LUT(Look-Up-Table)其本质是一个静态存储器SRAM,目前FPGA多采用4输入的LUT,每个LUT可以看作一个有4位地址线的16x1的RAM。当我们通过原理图或HDL语言描述了一个逻辑电路后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,在FPGA工作时,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

FPGA内部连接线很丰富,根据数据手册的描述,主要有图3中的Row interconnect、column interconnect、Direct link interconnect、和Local interconnect和Register chain interconnect(寄存器之间连接的连接线)。

内部连接线联通FPGA内部的所有单元,而连线的长度和工艺决定着信号再连接线上的驱动能力和传输速度。在实际开发中,设计者不需要直接选择连接线,布局布线器可自动地根据输入逻辑网表(这由综合生成)的拓扑结构和约束条件选择连接线来连通各个逻辑单元,所以,从本质上来说,布线资源的使用方法和设计的结果有密切和直接、直接的关系。

(责任编辑:fqj)

-

赛灵思FPGA全局时钟网络结构详解2013-11-28 14473

-

xilinx_fpga结构及工作原理介绍2012-08-02 6310

-

FPGA入门知识介绍2014-08-16 2515

-

FPGA—LUT结构介绍2018-07-09 5577

-

关于FPGA芯片资源介绍不看肯定后悔2021-09-18 2610

-

基于FPGA技术的无阻塞ATM交换技术结构的特点介绍2017-11-02 1230

-

基于FPGA芯片的数据流结构分析2017-11-18 3047

-

关于内置卡贴iphone5简单介绍2018-02-27 1401

-

FPGA视频教程之怎样开始一个简单的FPGA设计2019-03-20 1258

-

简单易懂的FPGA芯片内部硬件介绍2019-05-14 8422

-

关于FPGA的分析和介绍以及应用2019-09-05 3306

-

详细介绍关于FPGA开发板内部ram是如何操作的2020-07-20 2754

-

FPGA的基本结构和FPGA在电力系统中的应用详细说明2020-10-20 1672

-

介绍CPLD和FPGA的基本结构2023-06-28 5351

-

fpga芯片的简单介绍2024-03-26 2133

全部0条评论

快来发表一下你的评论吧 !