关于Cortex-M0的NVIC没有优先级分组功能,以及衍生内容

描述

今天遍地都是520的消息,华为也是热点。我们可以关注热点,自己的事还得继续做下去。

1写在前面

今天在一个交流群看到有人问,为什么NVIC没有优先级分组配置的选项,如下如:

这个问题,想必没有遇到过的人,还以为是STM32CubeMX的Bug。

其实,答案很简单:有的MCU是没有NVIC分组功能。

下面就针对这个NVIC分组功能展开来讲述。

2关于Cortex-M的NVIC

NVIC:Nested Vectored Interrupt Controller,嵌套向量中断控制器。

在每个Cortex-M内核中都有这么一个NVIC嵌套向量中断控制器,当MCU使用的内核不同,其中的NVIC也可能不同。

比如,Cortex-M0和Cortex-M3内核中NVIC功能就不同。

其中,中断优先级分组功能就不同。

Cortex-M0的NVIC没有优先级分组功能,Cortex-M3、 M4、M7有分组功能。

所以,你在使用STM32CubeMX配置时,M0内核的STM32是没有那个选项的。

Cortex-M0包含STM32F0、L0、G0等处理器。

对底层感兴趣的朋友可以继续往下看。

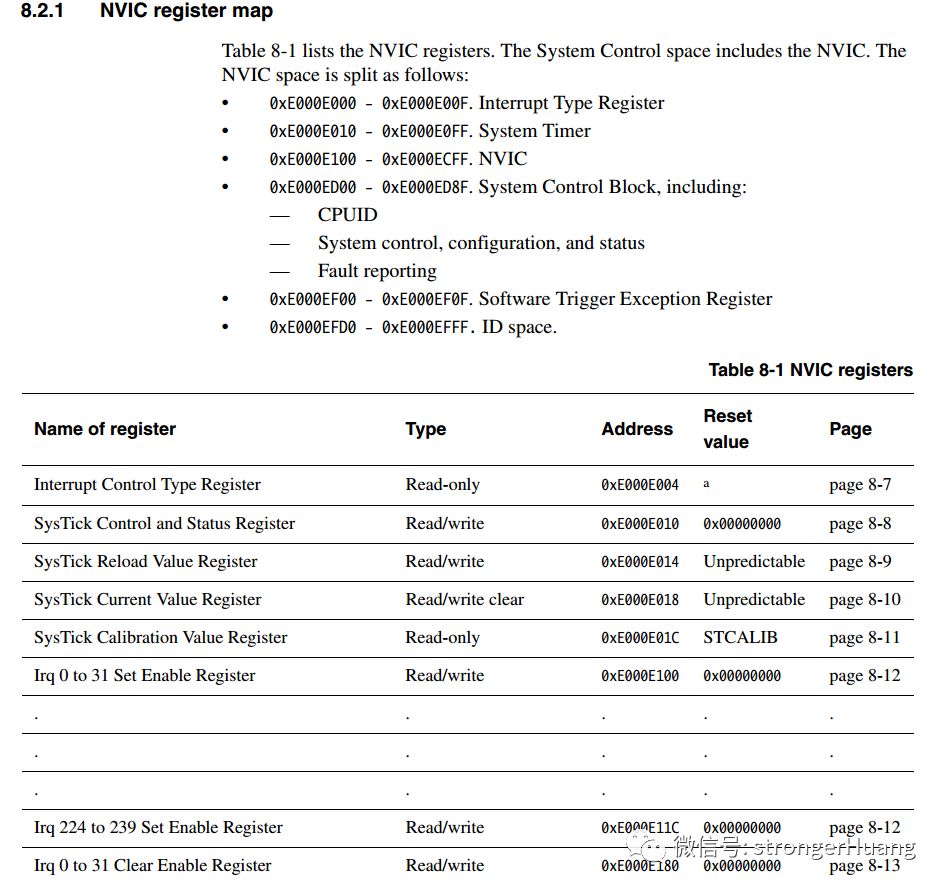

3NVIC寄存器

NVIC寄存器,需查看对应的内核(Cortex-M)手册,在ARM官网能找到。

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0432c/index.html

M3也有对应的中文翻译版,大家可以自己网上搜索。

内核中的寄存器和我们STM32参考手册中寄存器一样,不同的Bit位代表含义不同。

但是,对于NVIC来说,由于包含众多优先级相关配置,寄存器数量相对较多(NVIC寄存器族)。

拿M3来说,优先级分组的配置,位于NVIC的AIRCR应用程序中断及复位控制寄存器中:

这里推荐阅读之前我写过的一篇文章:STM32中断,及FreeRTOS中断优先级配置

4中断入口

前两天有人问题外部中断入口的问题:为什么外部中断8和9都使用同一个中断?

void EXTI9_5_IRQHandler(void){ if(EXTI_GetITStatus(EXTI_Line8) != RESET) { /* 代码 */ EXTI_ClearITPendingBit(EXTI_Line8); } if(EXTI_GetITStatus(EXTI_Line9) != RESET) { /* 代码 */ EXTI_ClearITPendingBit(EXTI_Line9); }}

我想,这个问题应该不难。

好比一个main程序入口,进入之后需要处理很多事情,只是在里面需要区分事件。

很多外设中断,都会使用同一个中断入口,有一个原因:节约中断入口资源分配。

像USART发送和接收中断,TIM不同通道捕获中断等。

-

STM32 MCU通过STM32CubeMx配置NVIC怎么没有中断子优先级选项2023-09-09 3339

-

Cortex-M中断及FreeRTOS中断优先级配置原理2022-02-08 1014

-

中断优先级分组(NVIC)的值与优先级有何关系2022-01-14 927

-

2021-04-16 NVIC中断优先级管理2021-12-04 900

-

关于M0+和M4的优先级设置问题2021-11-16 3952

-

NVIC中断优先级管理与中断优先级分组2021-08-16 1761

-

浅析stm32的中断嵌套优先级2021-08-13 2058

-

灵动微课堂 (第176讲) | Cortex-M0中断控制和系统控制(二)2021-07-29 2719

-

NVIC中断优先级分组2017-03-26 1554

-

[转] STN32抢占优先级与副优先级及中断优先级NVIC理解2014-04-15 4943

全部0条评论

快来发表一下你的评论吧 !