关于Xilinx FPGA内部体系结构的分析

可编程逻辑

描述

(文章来源:墨尘)

Xilinx的FPGA的基本结构是一样的,主要由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

但随着半导体工艺的发展,FPGA的逻辑容量越来越丰富,速度更快,嵌入越来越多的硬核了,比如:ARM处理器,PCIe, ETHERNET等。在制程工艺上,Xilinx的7系列FPGA采用28 nm工艺,UltraScale采用20nm, UltraScale+ 采用16nm,每一代工艺的可用资源,比上一代就翻了一倍。

Xilinx的FPGA是基于SRAM的查找表(LUT look up table)技术,所以需要上电后重新配置。从外部非易失性存储器中读数,通过配置控制器加载到内部配置SRAM 中。可编程I/O支持不同的IO引脚配置:IO标准、单端或差分、电压转换速率和输出强度、上拉或者下拉电阻、数控阻抗(DCI),可以使用IODELAY元件做输出延迟。

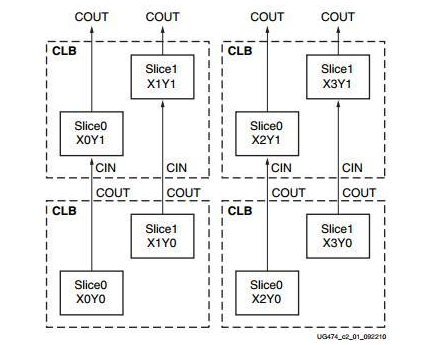

可配置逻辑块是指实现各种逻辑功能的电路,是xilinx基本逻辑单元。在Xilinx FPGA中,每个可配置逻辑块包含2个Slice。每个Slice 包含查找表、寄存器、进位链和多个多数选择器构成。而Slice又有两种不同的逻辑片:SLICEM和SLICEL。SLICEM有多功能的LUT,可配置成移位寄存器,或者ROM和RAM。逻辑片中的每个寄存器可以配置为锁存器使用。

布线资源用来连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置不同而划分为4类不同的类别。

第一类是全局布线资源,用于芯片内部全局时钟和复位/置位的布线;第二类是长线资源,用于完成Bank间的高速信号;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互联和布线;第四类是分布式布线资源,用于专有时钟、复位等控制信号线。

时钟资源分为全局时钟资源、区域时钟资源和I/O时钟资源。(1)全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。(2) 区域时钟网络是一组独立于全局时钟网络的时钟网络。(3) I/O时钟资源可用于局部I/O串行器/解串器电路设计。对于源同步接口设计尤其有用。

Xilinx FPGA的嵌入式存储器有两种类型:专用Block RAM(BRAM)和可配置成为分布式RAM的LUT。BRAM(Block RAM)是双端口的RAM,数量因器件而定,每个Virtex-4 BRAM 可存储18Kbit的数据,支持同步读写操作,两个端口对称且完全独立,共享数据,每个端口可以根据需要改变其位宽和深度。BRAM可以配置为单端口RAM、双端口RAM、内容可寻址存储器(CAM)以及FIFO等。BRAM提供专用的控制逻辑实现同步/异步FIFO,其中的控制逻辑如计数器,比较器和状态标记等不会占用额外的CLB资源。

在FIFO模式下,BRAM的端口A是读端口,端口B是写端口。对数据流操作是自动的,用户不必关心BRAM的编址顺序,当特殊应用需要时引出WRCOUNT和RDCOUNT。用户需要检测FULL和EMPTY标记。可以设置这两个标记值,将其配置到FIFO地址段内的任何位置。

FPGA除以上的资源和功能模块外,还有时钟管理(MMCM):数字时钟管理模块(DCM)与相位匹配时钟分频器(PCMD),DSP模块等。 DSP模块可提供高性能、低功耗的运算单元。它能够实现乘法-累加单元。还提供了专用的收发器模块,实现串行器/解串器(SerDes)功能,比如RocketIO模块,以太网模块(Ethernet MAC)模块,ARM核。

总之,随着FPGA的内部资源会变得越来越丰富,不仅在原来的在网络、电信、医疗、工业等多个领域有广泛的应用,而且在数据中心,云计算等新领域中进一步开疆拓土。

(责任编辑:fqj)

-

无线传感器网络的体系结构分析2011-11-03 9843

-

Xilinx_FPGA_内部结构深入分析2012-08-02 2721

-

ARM SOC体系结构2016-11-22 5904

-

可以在xilinx Blockset中估计FFT7.1块的各个体系结构的资源吗?2018-10-16 1603

-

Altera SoC FPGA体系结构有多重要?2019-09-26 2214

-

Microarchitecture指令集体系结构2021-12-14 1899

-

Arm的DRTM体系结构规范2023-08-08 968

-

ARM体系结构与编程2010-02-11 784

-

LTE体系结构2009-06-16 10197

-

网络体系结构,什么是网络体系结构2010-04-06 2091

-

体系结构建模工具SA分析2011-07-11 1319

-

软件体系结构的分析2017-11-24 1365

-

基于DoDAF的卫星应用信息链体系结构2018-01-10 1138

-

Xilinx的UltraScale体系结构和产品数据手册的资料概述2019-02-22 1560

-

Xilinx FPGA内部体系结构2019-06-11 4231

全部0条评论

快来发表一下你的评论吧 !