第三版HBM2存储标准发布,环比提升33%

电子说

1.4w人已加入

描述

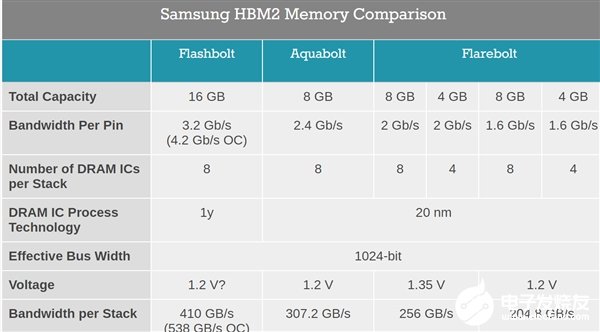

本周,固态存储协会(JEDEC)发布第三版HBM2存储标准JESD235C,将针脚带宽提高到3.2Gbps,前两版中依次是2Gbps、2.4Gbps,环比提升33%。

按照设计规范,单Die最大2GB、单堆栈12 Die(无标准高度限制),也就是24GB容量,匹配1024bit位宽,单堆栈理论最大带宽410GB/s。对于支持四堆栈(4096bit)的图形芯片来说,总带宽高达1.64TB/s。

第三代HBM2的电压和上一版一致,为1.2V,比第一代的1.35V有所下降。

简单比较下,常见高端独显采用的256bit GDDR6,按照14Gbps的针脚带宽计算,总带宽448GB/s,也就是第三代HBM2一个堆栈的水平。考虑到HBM2更容易扩充总线宽度,GDDR6过犹不及,况且单堆栈最大容量就能达到24GB,四堆栈直逼100GB。

图为HBM显存示意

事实上,3.2Gbps的第三代HBM2早先已经由三星和SK海力士提出,并更名为HBM2E,这种说法也得到了JEDEC默认。

在JESD235C标准发布的同时,三星宣布,名为Flashbolt(前两代名为Flarebolt和Aquabolt)的第三代HBM2(HBM2E)存储芯片将在上半年量产,单颗最大容量16GB,由16Gb的单Die通过8层堆叠而成。

三星的第三代HBM2E甚至支持超频,单针脚可加速到4.2Gbps,单堆栈最大带宽从而升至538GB/s。

责任编辑:gt

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADI参考电路合集(第三版)2023-11-18 902

-

Linux私房菜基础篇-第三版2022-03-07 1045

-

开关电源设计 第三版2021-09-29 4129

-

还没用上HBM2E?HBM3要来了2021-08-23 2594

-

LabVIEW大学实用教程(第三版)2020-03-29 4647

-

三星推出第三代HBM2存储芯片,适用于高性能计算系统2020-02-05 4360

-

PHASELOCK TECHNIQUES 第三版FLOYD M. GARDNER2019-10-01 2373

-

单片机原理及应用教程第三版答案2016-03-15 1244

-

数值方法第三版2015-12-30 797

-

信号与系统_郑君里第三版2015-04-22 21772

-

linux权威指南(第三版)2014-02-27 529

-

linux内核驱动第三版2013-04-04 325

-

EDA技术实用教程(第三版)2012-07-07 258

-

LINUX内核驱动第三版(中文)2010-03-11 508

全部0条评论

快来发表一下你的评论吧 !