SoC FPGA的数据采集如何解决与系统的交互问题

FPGA/ASIC技术

描述

引言

Internet 的快速发展和成功促进了以太网(Ethernet)技术的发展和应用的扩展,所涉及的领域十分广泛,如传统的工业控制、信息家电、智能家居、安全监控、楼宇自动化、医疗、环境监测等。大多数的数据采集设备的通信接口符合 UART 通信标准。这种通信方式的数据传输半径十分有限,并不能满足远距离传输的需求,并且不能接入 Internet. 因此数据的交互接入 Internet 就显得非常重要了。

1、系统的总体方案及各主要模块设计

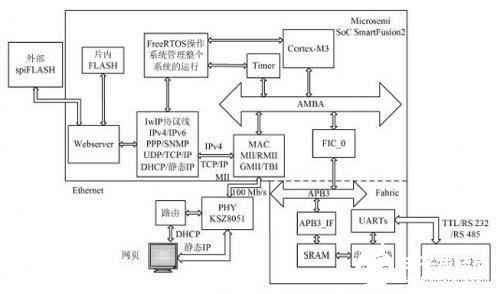

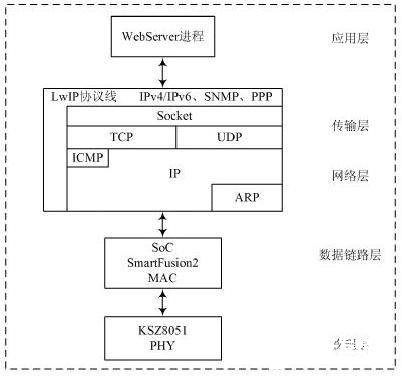

系统以 Microsemi(Actel)公司的基于 FLASH 架构的 SoC FPGA 产品 Smart Fusion2 器件为核心。系统通过 Fabric 架构实现多路 UART 对外相应数据进行采集,进行并 / 串转换写入 Fabric 的双端口 RAM.SmartFusion2 的 ARM Cortex-M3 子系统经过 AHB/APB 总线矩阵以 AHB/APB 方式访问 Fabric 的 RAM,将得到的数据经过 Ethernet 以网页的形式在 PC 上显示。反之,以同样的路径将主控的指令传输到外部的终端设备。PC 机端以网页形式实现数据交互。网页存放于 SmartFusion2 内部 FLASH,内核 Cortex-M3 基于实时操作系统(FreeRTOS)管理任务,IP 采用静态方式,内核 Cortex-M3 与 Fabric 采用 AHB 方式通信 . 系统设计结构框图如图 1 所示。

图 1 系统设计结构框图

系统硬件的设计可分为三个主要模块,分别为 PHY 物理层模块,SoC 的 Cortex-M3 内核及 FPGA 系统,UART 模块的数据采集系统。

1.1 PHY 模块

PHY 即物理层(Physical Layer)。物理层协议可定义电气信号标准、连线的状态、时钟信号的要求、数据编码的格式和数据传输所用的连接器等。物理层通过一个定义好的接口与数据链路层进行通信。比如 MAC 可以利用标准的介质无关性接口( MII 接口)与 PHY 进行数据交换通信。PHY 还有个重要的功能就是实现以太网的 CSMA/CD 部分功能,这是硬件上实现的。它可以检测到网络链路上是否有数据正在传送,如果有数据在传送中则进行等待,当检测到网络空闲,就再等待一定的时间(不同的 PHY 会有不同)后对数据进行传送。倘若两块网卡碰巧是同时发送数据,这将造成冲突,这时 PHY 内部的冲突检测结构可以检测到冲突的发生,然后两边各自等待一定的时间进行重发数据。

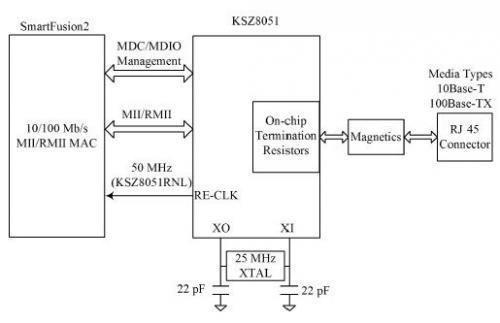

图 2 PHY 电路连接图

PHY 的电路图连接图如图 2 所示。KSZ8051 采用 MII 与 SmartFusion2 相连,由于 MII 兼容 RMII 接口,因此程序也可配置为 RMII 模式。Management 采用 2 个引脚连接,分别为 MDC 和 MDIO,MII 的时钟由 PHYKSZ8051 提供,KSZ8051 的时钟来自外部 25 MHz 晶振。媒体连接采用 RJ 45,兼容 10 Mb/s 和 100 Mb/s.

1.2 SoC 中的 Cortex-M3 模块

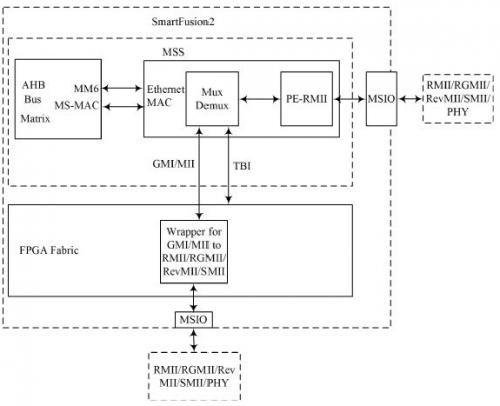

系统使用 Cortex-M3 中的 MAC 模块,如图 3 所示。

通过 AHB 控制 Ethernet MAC 模块,对于 MAC 的配置是使用其内部的寄存器,可以配置不同的接口模式,不同的速度。本系统配置为 MII 接口,100 Mb/s 速度。

图 3 Cortex-M3 的 MAC

MAC(Media Access Control,媒体访问控制子层协议),主要负责控制和连接物理层。在发送数据的时候,MAC 协议可以事先判断现在是否可以发送数据,如果可以发送则将给数据加上一些控制信息,最终将数据及附带的控制信息以规定的格式发送到物理层;在接收数据的时候,MAC 协议首先判断输入的信息是否发生传输错误,如果没有错误,则去掉控制信息发送至逻辑链路层(LLC)层。以太网 MAC 协议由 IEEE 802.3 以太网标准定义。

PHY 与 MAC 的接口方式有多种,如:

MII,RMII,SMII,SSMII,GMII,SGMII,TBI 等。目前常见的 PHY 都提供标准的 MII 接口,RMII 信号是对 PHY 内部的 MII 的信号进行编码和解码,这就是说支持 MII 接口的 PHY 内部都含有 RMII 信号,也就是支持 RMII 接口。具体使用何种接口的 PHY 则必须根据 MAC 芯片对应的功能和接口的标准来决定。

采用 FreeRTOS 实时操作系统管理整个系统的运行。FreeRTOS 使用 Cortex-M3 内核的定时器以 10 ms 时间片进行任务的调度和切换。创建 WebServer 进程和网页进行通信,网页编辑语言 HTML 是不需要编译的,因此将需要显示的数据全部发送给网页。这些数据存储在 FLASH 中,目前测试是存储在片内 FLASH,网页发来的控制数据进行实时的处理。网页的数据需要用 LwIP 协议栈进行打包,LwIP 协议栈是把所有的协议封装到一个单一的过程(进程)中,从而与操作系统内核分开。应用程序可能也驻留在 LwIP 处理过程中,或者在单独的过程中。TCP/IP 栈和应用程序之间的通信可以通过函数调用实现,也可以通过更为抽象的 API[4-5]. 本设计的应用层使用常用的 IPv4 协议,DHCP 和静态 IP 都进行测试,传输层和网络层使用 TCP/IP.

打包之后的需要介质层 MAC 进行处理,此 MAC 为 Cortex-M3 内核自带的,支持多种 MAC 接口,本设计采用 MII 接口,所采用的 PHY 芯片也是 MII 接口,采用 Micrel 公司的 KSZ8051,支持 MII、RMII 接口,10 Mb/s 和 100Mb/s 传输速度,设计时采用 100Mb/s 传输。

网页的数据需要实时更新,设计网页每隔 500 ms 发一次更新的命令,Cortex- M3 再将更新的数据发送给网页。而这些数据来自 APB3 上,Cortex-M3 通过 FIC_0 和 APB3 进行双向通信,从而发送和接收数据。FPGA 中 Fabric 和 APB3 进行双向通信,数据存储在双端口 SRAM 中,多路 UART 和 SRAM 进行双向通信。SRAM 在系统起缓存的作用,用来解决两端读写速度的不同。

而对于 UART 的数据也定义了协议,这些协议是区分数据的格式和内容。对于 UART 的个数可以进行增加,系统 UART 的同步使用 FPGA 硬件实现,不受个数的限制。

1.3 FPGA 的 UART 模块

本系统的主要功能是 UART 数据的采集与交互,使用网页进行人机交换,实现数据的实时更新和控制,并且把采样点的采样时间也传输过去,使用户知道数据的具体时间,便于以后的查看。

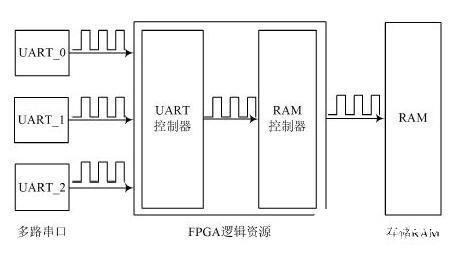

在本设计中需要在 SmartFusion2 片内的 FPGA 部分设计多路串口数据采集与存储的控制器,实现对终端的多路串口数据进行采集。使用的多路串口数据采集方法是在 SmartFusion2 片内的 FPGA 中设计一个 UART 控制器去采集多路数据[6]. 控制器并不完成串转并控制,而是实时监测多路串口数据状态,并将多路串行数据实时切换送入 RAM 控制器,串行的数据经过 RAM 控制器串行的进入 RAM 中去。如图 4 所示。

图 4 串口复用数据采集

当多路串口中任何一路,任何时候到来数据的时候,UART 控制器都能感知这次串行数据,并开通相应的信道,将某一路的串口数据送到 RAM 控制器。然后 RAM 控制器将该信道的串行数据写入 RAM 中。这样就可以完成对多路串口数据的采集工作。

在该方案中,需要在 SmartFusion2 片上的 FPGA 内设计一个 UART 控制器作为查询机制中的主机,各个终端串口作为从机,提供串口数据。主机会定时的在 SEL 总线上发出从机的片选信号,用于选通从机设备。当从机被选中之后,从机自己会做出判断,如果该从机有数据需要发送,则该从机立刻将串行的数据发出。如果从机没有数据需要发送,则从机对该选择信号 SEL 不做任何反应,定时时间到,主机会自动的去选通下一路从机,从机工作原理与之类似。这样的做法同样可以完成对多路串口数据的采集工作。

2、系统软件设计

本设计采用 FreeRTOS 操作系统,通过创建 WebServer 进程实现数据的交互。在初始化完成后,执行 WebServer 进程,WebServer 进程发送网页的数据、更新网页的数据、得到采集的数据。而关于以太网的协议则使用 LwIP 协议栈实现。对于硬件层则使用 Cortex-M3 内部的 MAC 和外部的 PHY 进行传输。实现物理层的传输[7]. 因此本设计的思路是发送接收数据给网页和接收发送 APB3 上对应的地址的数据。将 UART 的数据格式和网页 HTTP 数据格式互换。

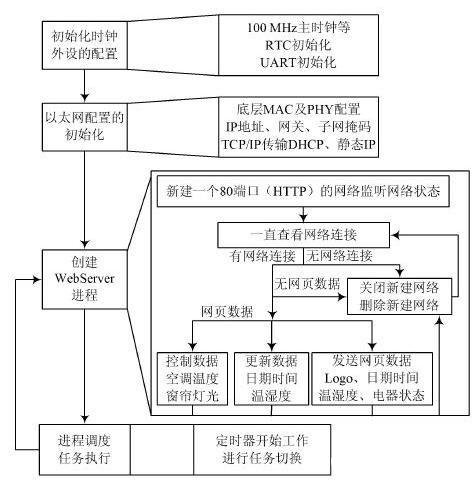

软件设计框图如图 5 所示,WebServer 进程和网页进行通信,通信的协议采用 LwIP 协议,对于 LwIP 协议使用其中的 IPv4 应用层,使用 TCP/IP 传输,DHCP 动态获取 IP,数据链路层使用内部的 MAC,采用 100 Mb/s 的 MII 接口和 PHY 通信,PHY 在物理层上和 PC 机通信[8].

图 5 软件设计框图

采用自动连接的方式与以太网相连,对于 HTTP 数据采用监听的方式,有 HTTP 数据则执行相应的操作。在网页上显示实时的日期和时间,这个日期和时间不是来自 PC 机的,而是来自 SmartFusion2 的,能够达到显示数据的采样时间,方便用户查看和保存带有时间的数据。

以太网的初始化首先是 MAC 的初始化,将 MAC 初始化为 MII 接口,半字节,100 Mb/s 模式。MAC 初始化后就是对于协议的选择,本系统选择 TCP/IP 协议,通过 tcpip_input 调用初始化网络的配置。对于网络的配置,首先是 MAC 地址、IP 地址、网关、子网掩码的配置(如果为 DHCP 则只有 MAC 地址有效),可以配置为静态 IP 和 DHCP 两种模式。静态 IP 使用 netif_set_up 函数,DHCP 使用 dhcp_star 函数来开始。

WebServer 是系统的主任务,负责网页和 APB3 上数据的交互。首先是使用 netconn_bind 函数新建一个 80 端口(HTTP)的网络,建立好后就一直处于监听状态的 netconn_listen 函数。

有网络连接时则发送相应的数据。如果有网页打开数据的请求,则开始发送网页的数据头和主界面的数据,同时将网页的运行的程序也发送过去,这样内核就可以方便和网页进行通信。

对于网页的刷新和数据请求命令都是已经发送给网页了,如果有网页的刷新请求则将更新的检测数据和日期时间数据发送给网页。有点击控制命令,处理器则马上响应,将控制命令转换并发送给 APB3,也就发送给了 UART. 当然,这里面所有的数据都是加了相应的通信协议。

如发送数据给网页时则需要使用 netconn_write 函数,首先是网页数据头,然后是相应的数据。如果无网络连接、无网页请求、请求完成等都是使用 netconn_close 函数关闭网络,使用 netbuf_delete 函数删除网络,然后又去监听是否有新的网络存在并连接。

图 6 软件设计流程图

以智能家居数据采集与交互为例,系统软件设置流程图如图 6 所示,首先是时钟和外设的初始化,再是以太网相关的初始化,包括 MAC 和 PHY 的初始化,IP 的获取方式,设置 MAC 地址、IP 地址、子网掩码、网关,设置传输的协议等。硬件层、传输层设置以后就是应用层,创建 WebServer 应用程序。此应用程序也是主应用程序,在 FreeRTOS 中的优先级是最高的,堆栈大小也是最大的。WebServer 任务就是与网页通信,实现网页的刷新。任务的调度和切换时通过定时器实现,10 ms 为一个时间片,调度函数为 vTaskStartScheduler 函数实现。

3、结语

本文利用源代码开放的 TCP/IP 协议栈 LwIP 和简单实用的操作系统 FreeRTOS 软件平台和 SmartFusion2 的硬件平台构建了基于 SoC 的数据采集与交互系统,完成设备数据信息的采集及处理并实现远程数据交流与共享。通过实际运行测试,系统性能稳定可靠,具有一定推广使用价值。

-

FPGA的多通道数据采集传输系统2024-12-09 1248

-

HarmonyOS应用框架如何解决多设备交互问题?2021-08-12 2239

-

请问怎样去设计一种数据采集与交互系统?2021-05-24 1680

-

怎样通过SoC去实现数据采集系统?2021-05-12 1136

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 2337

-

基于FPGA与SRAM数据采集系统设计2018-05-09 3041

-

基于FPGA的高速数据采集系统设计_杨江涛2016-05-17 889

-

高速数据采集系统中的FPGA的设计2016-05-10 743

-

基于FPGA的数据采集系统2012-08-11 5466

-

远程数据采集与交互系统设计2012-05-17 2644

全部0条评论

快来发表一下你的评论吧 !