EMC的基本概念及设计流程解析

EMC/EMI设计

描述

EMC简单介绍

EMC的概念:电磁兼容(Electromagnetic Compatibility , EMC) 其定义为“设备和系统在其电磁环境中能正常工作且不对环境中任何事物构成不能承受的电磁骚扰的能力”。

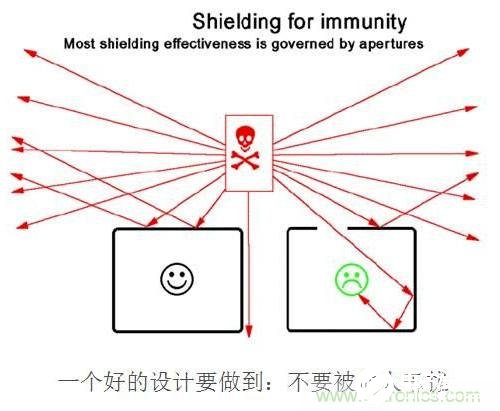

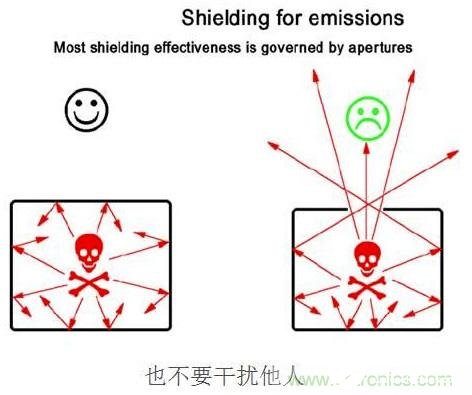

EMC包含两个方面的意思,首先,设备能够抵抗所接受到的干扰而正常工作(即EMS);其次,设备所发射的电磁干扰不能影响其它设备的正常工作(即EMI)。

EMC设计

1. EMC设计的内容:

EMC设计可分为:

信号设计、线路设计、屏蔽、接地、滤波、合理布局

其中与结构关系较大的有:

屏蔽、接地、合理布局

注意:并不代表其它措施与结构设计完全无关,结构设计亦需配合完成其它措施比如合理布局。

2. EMC设计基本目的:

产品内部的电路互相不产生干扰,达到预期的功能。

产品产生的电磁干扰强度低于特定的极限值。

产品对外界的电磁干扰有一定的抵抗能力。

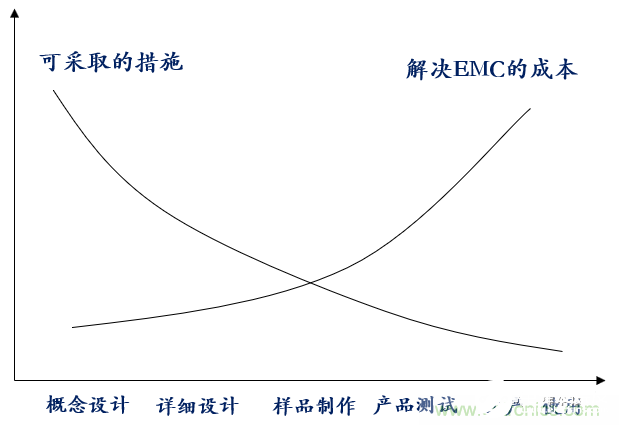

3. EMC设计在产品开发各阶段的成本:

在产品设计的早期阶段,解决EMC问题的途径多,将花费较少的成本;到产品生产后期再采取解决EMC的技术措施,将受到各种情况的制约。并且,采用同样的技术措施,在生产后期采用时,将大大增加产品成本,延长产品开发周期。

▲EMC设计在产品开发各阶段的成本

因此,随着产品开发向前推进,解决EMC的成本越来越高。因此,EMC设计越早进行越好,千万不要等到EMC测试出现问题了,再去急急忙忙的查找原因、寻找解决方案。

4. 传统EMC对策:

产品在进行实际测试的时候,EMC问题实际发生了,开始查找EMC问题,使用的工具:频谱仪和近场探头

此时能够采取的手段是:屏蔽和滤波

传统EMC对策存在的问题是:

● 需要考虑设备内部【板间,板内信号间】EMI问题,不能使用屏蔽/滤波手段;

● 屏蔽和滤波会导致产品设计修改,增加产品成本和延长产品开发周期;

● 信号频率与干扰频率一致,不能采用滤波;

● 频率提高,布线、屏蔽体、机箱等成为天线;

● 高频信号耦合到电缆,由电缆发射;

● 产品开发最后阶段解决EMC问题的唯一办法是:屏蔽和滤波。但是,用屏蔽能解决所有的EMC问题?

● 屏蔽策略的隐患:机箱及屏蔽材料的变形及损坏,产生电磁泄漏

● 这种对策的结果是:有利于通过EMC,但是会恶化内部干扰,影响设备稳定性,增加抗干扰的要求。

5. EMC对策新理念:

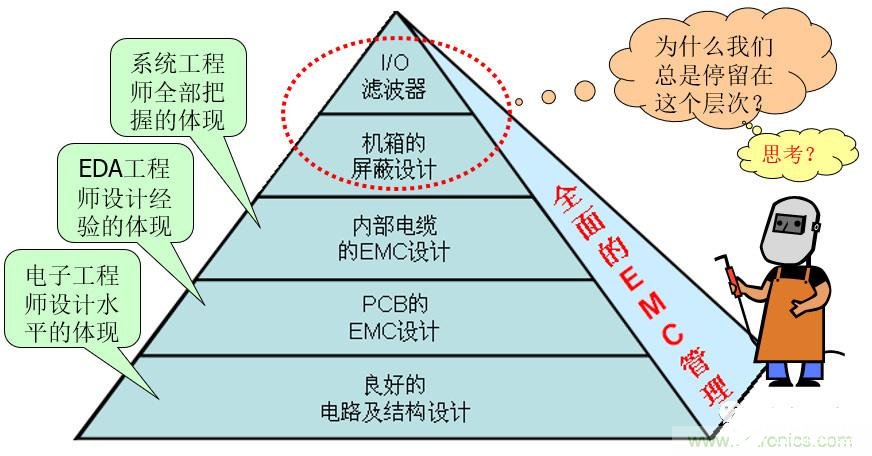

▲全面的EMC管理

EMC对策的新理念是进行全面的EMC管理,尽早进行EMC设计:

● EMC是一项系统工程:早考虑 ,成本低,手段多,效率高;需要产品开发团队协同配合,包括结构设计。

● 充分利用现有的EMC设计规范和设计指南(专家的经验),当然,在使用的时候需要思考:设计能全部按照设计规则执行吗?所有理论在所有场合都正确吗?

● 合理使用仿真技术,把问题扼杀在萌芽阶段 。PCB板设计的仿真:Hyperlynx。电子电路仿真:Pspice、Serenade。

● 精度与速度,实际问题实际解决。使用测量技术,使用一般仪器进行对比测试。引入电磁场扫描技术,进行EMC预兼容测试。

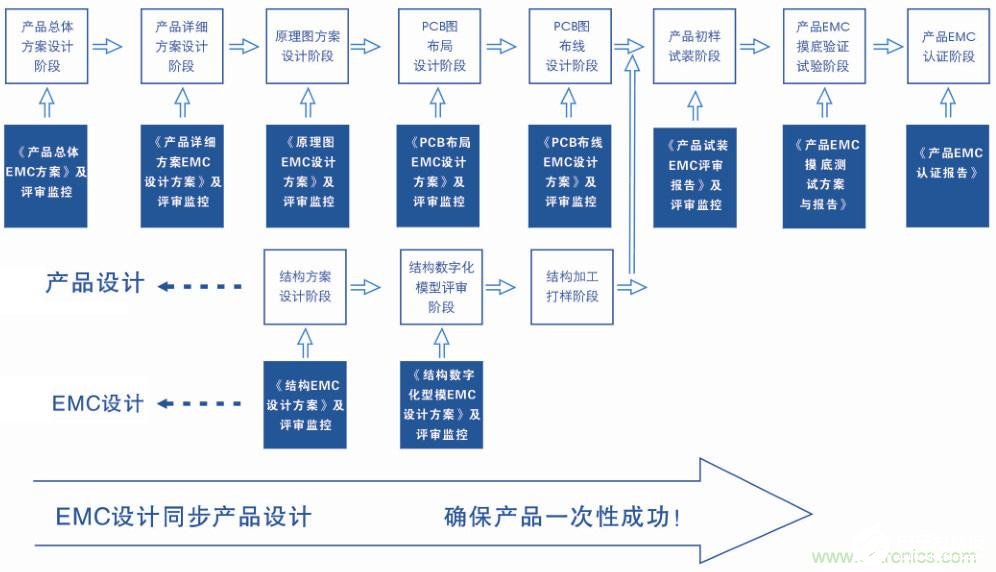

6. EMC设计的流程:

7. EMC结构设计的经验:

● 在项目的早期就参与结构设计,由硬件工程师主导硬件系统的结构设计,而不是被动地接收已有的结构造型,然后千方百计地想办法怎样才能在现有的造型基础上尽量满足性能、EMC等的要求,要在结构设计中起到主导性的作用;

● 尽早设计出3D图,针对3D图,组织各方面的人员反复讨论,权衡利弊,就EMC而言,要针对3D图去发现问题,填补问题,这样的互动要进行很多次,直至能得到一个比较满意的结果;

● 屏蔽结构的使用,哪些板卡需要屏蔽、哪些可以不要,未屏蔽的板卡要针对EMC采取哪些预防措施,PCB本身也许就可以作为EMC的屏蔽体;

● 线材处理,包括内部模块互连线(暴露在屏蔽壳之外)及外部接口线,是否已经在母板、连接板或输出板等位置预留滤波措施。

8、EMC PCB 设计

(1)、PCB设计

a、布局:同类电路布在一块、控制最小路径原则、高速电路间不要靠近小面板、电源模块靠近进单盘的位置;

b、分层:高速布线层必须靠近一层地、电源与地相邻、元件面下布一层地、近可能将两个表层布地层、内层比表层缩进20H;

c、布线:3W原则、差分对线等长,靠近走、高速或敏感线不能 跨分割区;

d、接地:同类电路单独分布地,在单板上单点相连;

e、滤波:电源模块、功能电路设计板级虑波电路;

f、接口电路设计:接口电路设计滤波电路、实现内外有效隔离。

(2)布局的基本原则:

a、参照原理功能框图,基于信号流向,按照功能模块划分;

b、数字电路与模拟电路、高速电路与低速电路、干扰源与敏感电路分开布局

c、单板焊接面避免放置敏感器件或强辐射器件;

d、敏感信号、强辐射信号回路面积最小;

e、晶体、晶振、继电器、开关电源等强辐射器件或敏感器件远离单板拉手条、对外接口连接器、敏感器件放置,推荐距离≥1000mil;

f、敏感器件:远离强辐射器件,推荐距离≥1000mil;

g、隔离器件、A/D器件:输入、输出互相分开,无耦合通路(如相邻的参考平面),最好跨接于对应的分割区;

(3)特殊器件布局

a、电源部分(置于电源入口处);

b、时钟部分(远离开口,靠近负载,布线内层);

c、电感线圈(远离EMI源);

d、总线驱动部分(布线内层,远离开口,靠近宿);

e、滤波器件(输入、输出分开,靠近源,引线短);

(4)滤波电容的布局:BULK电容:

a、所有分支电源接口电路;

b、功耗大的元器件附近;

c、存在较大电流变化的区域,如电源模块的输入和输出端、风 扇、继电器等;

d、PCB电源接口电路;

(5)去藕电容的布局:

a、靠近电源管脚;

b、位置、数量适当;

(6)接口电路的布局的基本原则:

a. 接口信号的滤波、防护和隔离等器件靠近接口连接器放置,先防护,后滤波;

b. 接口变压器、光耦等隔离器件做到初次级完全隔离;

c. 变压器与连接器之间的信号网络无交叉;

d. 变压器对应的BOTTOM层区域尽可能没有其它器件放置;

e. 接口芯片(网口、E1/T1口、串口等)尽量靠近变压器或连接器放置;

(7)布线

a. 走线短,不同类走线间距宽(信号及其回流线、差分线、屏蔽地线除外),过孔少,无环路,回路面积小,无线头;

b. 有延时要求的走线,其长度符合要求;

c. 无直角,对关键信号线优先采用圆弧倒角;

d. 相邻层信号走线互相垂直或相邻层的关键信号平行布线≤1000MIL;

e. 走线线宽无跳变或满足阻抗一致;

(8)各国产品安全和EMC认证组织

-欧美:CE

-美国:FCC&UL,NEBS

-日本:VCCI

-澳大利亚:CE

-中国:CCC

-***:CE

产品认证流程

-认证申请

-提交认证材料(认证标准、产品使用手册等)

-产品测试

-完成测试报告

-颁发认证证书

-产品发布

EMC标准及测试

国际标准

1、国际电工委员为IEC

2、国际标准华组织ISO

3、电气电子工程师学会IEEE

4、欧盟电信标准委员会ETSI

5、国际无线电通信咨询委员CCIR

6、国际通讯联盟ITU

6、国际电工委员会IEC有以下分会进行EMC标准研究

-CISPR:国际无线电干扰特别委员会

-TC77:电气设备(包括电网)内电磁兼容技术委员会

-TC65:工业过程测量和控制

国际标准化组织

1、FCC联邦通

2、VDE德国电气工程师协会

3、VCCI日本民间干扰

4、BS英国标准

5、ABSI美国国家标准

6、GOSTR俄罗斯政府标准

7、GB、GB/T中国国家标准

EMI测试

1、辐射骚扰电磁场(RE)

2、骚扰功率(DP)

3、传导骚扰(CE)

4、谐波电路(Harmonic)

5、电压波动及闪烁(Flicker)

6、瞬态骚扰电源(TDV)

EMS测试

1、辐射敏感度试验(RS)

2、工频次次辐射敏感度试验(PMS)

3、静电放电抗扰度(ESD)

4、射频场感应的传导骚扰抗扰度测试(CS)

5、电压暂降,短时中断和电压变化抗扰度测试(DIP)

6、浪涌(冲击)抗扰度测试(SURGE)

7、电快速瞬变脉冲群抗扰度测试(EFT/B)

8、电力线感应/接触(Power induction/contact)

EMC测试结果的评价

A级:实验中技术性能指标正常

B级:试验中性能暂时降低,功能不丧失,实验后能自行恢复

C级:功能允许丧失,但能自恢复,或操作者干预后能恢复

R级:除保护元件外,不允许出现因设备(元件)或软件损坏数据丢失而造成不能恢复的功能丧失或性能降低。

5、电压暂降,短时中断和电压变化抗扰度测试(DIP)

6、浪涌(冲击)抗扰度测试(SURGE)

7、电快速瞬变脉冲群抗扰度测试(EFT/B)

8、电力线感应/接触(Power induction/contact)

责任编辑;zl

- 相关推荐

- 热点推荐

- emc

-

放大电路中反馈的基本概念及判断方法2023-03-10 8425

-

共生散射通信的基本概念及技术原理2022-08-10 1883

-

数字地、模拟地、信号地、交流地、直流地、屏蔽地、浮地基本概念及PCB地线分割的方法2021-12-01 1541

-

嵌入式系统的基本概念及特点2021-11-08 1338

-

慕课嵌入式开发及应用(第四章.USB基本概念及从机编程方法)2021-11-03 888

-

嵌入式的基本概念及其应用2021-10-27 1614

-

AGV的基本概念及基本结构组成2021-09-14 2918

-

定时器的基本概念及初始化配置硬件2021-08-19 1128

-

串口通讯的概念及接口电路解析,不看肯定后悔2021-05-27 2617

-

阻抗控制相关的基本概念2021-02-25 2176

-

基于RF射频知识基本概念及DTD无线产品介绍2017-10-25 1331

-

C语言基本概念及语法2012-08-18 6944

-

天线的基本概念及制作2010-01-04 1613

-

电路的基本概念及定律 英语中文对照表2009-02-10 1362

全部0条评论

快来发表一下你的评论吧 !