基于高精度可编程延迟单元实现高性能8倍采样器的设计

可编程逻辑

描述

异步串行数据接口要求接收器恢复数据,方式是对比特流进行检查,并在所发送数据未附带时钟时确定每个位的采样位置。有几种方法可以在 Xilinx FPGA 中实现此类接收器。RocketIO收发器就是专门为这一任务设计的,但并非在所有 Xilinx FPGA 中都可用。根据器件系列和速度级别不同,SelectIO 的输入端和 FPGA 逻辑资源可以实现比特率高达近 1 Gb/s 的异步串行接收器。

对于行程短且抖动小的数据,每个位周期对比特流采样四次左右足矣。这种低过采样率数据恢复技术在 XAPP224 《数据恢复》中有描述。不过,如果未经过位转换数据行程就很长或者所要求的抖动容限高时,就需要较高的过采样率,这在传统上需要使用多个时钟相位,常常要占用若干数字时钟管理器 (DCM) 及大量全局时钟资源。

Xilinx Virtex-4 和 Virtex-5 器件的每个输入引脚都有与其相关的高精度可编程延迟单元。这些延迟单元被称为 IDELAY,可用于实现过采样器,这种过采样器仅利用极少的 FPGA 逻辑资源,而更重要的是,进行 8 倍过采样只需一个 DCM 和两个全局时钟资源。与使用多个 DCM的技术相比,这种解决方案可提供更高的抖动容限。

如果配以适当的数据恢复方案,就可以将本文所述的过采样技术用于多种不同的数据协议,在Virtex-5 器件中采样率可达 550 Mb/s,而在 Virtex-4 器件中可达 500 Mb/s。我们举例说明如何使用这种技术,用参考设计实现一个以 270 Mb/s 运行的 SD-SDI (SMPTE 259M) 接收器。

过采样技术

使用过采样的异步串行数据恢复技术要求接收器对输入的比特流快速采样,其速度足以在每个位周期中采集多个样本。这种采样方法可提供有关比特流的足够信息,从而可以确定位转换的位置,并且保证每个位的采样点都靠近位中心而远离转换区。

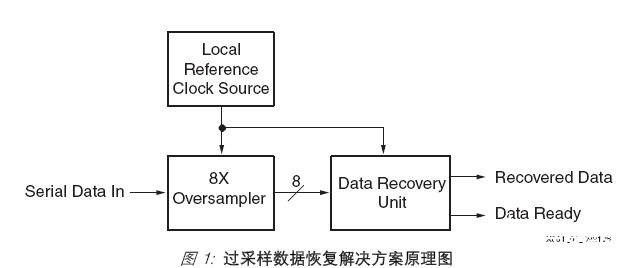

图1 所示为一典型异步串行数据过采样数据接收器。此接收器由两大部分组成:过采样器和数据恢复单元 (DRU)。过采样器在每个位周期对比特流进行多次采样,采集足够多数据传输给DRU。DRU 必须在每个位周期中取得足够的样本,以便确定发生位转换的位置,然后在距离转换区安全的位置对各个位进行采样。通常,过采样器在每个位周期中能向 DRU 提供的样本越多,DRU 对位转换发生位置的判断就越准确,对数据的恢复也越精确。每个位周期取得较多样本可以提高 DRU 的抖动容限。

有多种方法可以在 Xilinx FPGA 中实现过采样器。可以将 RocketIO 收发器用作过采样器,在某些情况下以 1 Gb/s 或更高比特率进行过采样。实际上,一些 RocketIO 收发器内置了过采样接收器(称为数字接收器),所支持的比特率低于普通接收器。

在用 SelectIO 输入端接收异步串行比特流时,通常限制最大可支持比特率的是 FPGA 的最大时钟速率,而非 IOB 所支持的最大速率。因为过采样器必须在每个位周期内对比特流多次采样,所以采样时钟必须明显快于比特率。使用采样时钟的多个时钟相位,即可在不提高时钟频率的情况下增加每个位周期的样本数量,但是这种方法需要以某种方式精确地生成并分配多个时钟相位,而且会用尽多个全局时钟布线资源。例如,使用相互间隔 45 度的四个时钟相位,并且使用各时钟相位的两个边沿,就可以保证 8 倍过采样的基本时钟频率与比特率相同。

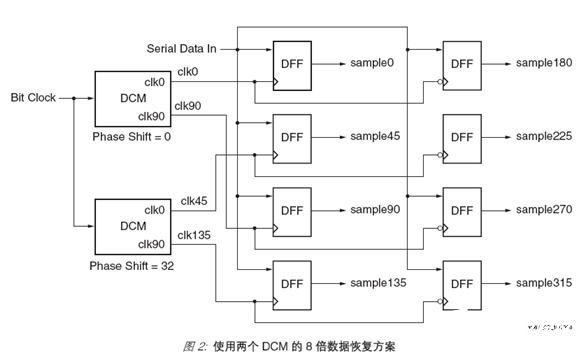

可以用 DCM 为串行输入的过采样创建多个时钟相位(参见 XAPP224 中的图2)。不过,根据时钟频率和每个位周期样本数不同,可能需要多个 DCM 才能提供足够的时钟相位。如果使用多个 DCM,这些 DCM 的输出就会在相互间产生相对抖动,这样就会降低采样点的精确性,从而降低接收器的抖动容限。图2 中使用的方案还要求与四个时钟相位对应的四个全局时钟。不过,如果所有比特率都相同,就可用这四个全局时钟来支持多个过采样器。

Xilinx 针对是否符合 SD-SDI 协议对多时钟相位过采样器进行了实验;因为支持的电缆长,这种协议要求位转换之间的行程长,抖动容限高。这些实验显示,任何低于 6X SD-SDI 比特流的过采样都无法提供足够的抖动容限,而 8 倍过采样是较为现实的下限。如图2 所示,使用四个时钟相位的 8 倍过采样方案需要两个 DCM。Xilinx 的实验显示,这两个 DCM 在时钟相位上产生的相对抖动将 DRU 的抖动容限降到了无法接受的程度。如果可以只使用一个 DCM,那么就能减轻时钟相位抖动问题,但仍然需要四个全局时钟。一个 Virtex-5 PLL 就可以生成四个低抖动的时钟相位,但仍需四个全局时钟将这四个时钟相位传送到过采样器。Virtex-4 器件不具备这种 PLL。

使用 IDELAY实现高效过采样

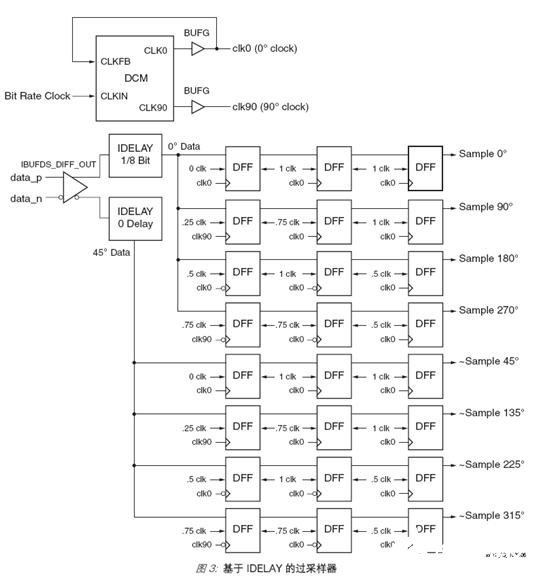

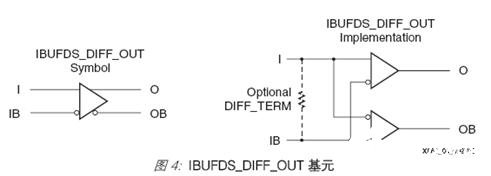

图3 所示为基于 IDELAY 的过采样器。一个 DCM 用来创建间隔 90 度的两个时钟相位。使用这两个时钟相位的两个边沿,可以在一个位周期内给定四个间隔均等的采样点。串行比特流通过称为 IBUFDS_DIFF_OUT 的基元进入 FPGA。因为此基元仅支持 LVDS 输入,所以串行数据必须为 LVDS 格式。一般的 LVDS 输入基元只向 FPGA 提供一个信号,但 IBUFDS_DIFF_OUT 基元会将接收到的真实信号及其反转信号都提供给 FPGA。如图4 所示,IBUFDS_DIFF_OUT 使用两个差分接收器,一个在 LVDS 对的 P 输入 IOB 中,另一个在其 N 输入 IOB。这些差分接收器各向 FPGA 提供一个信号,N 侧 IOB 发出的信号与 P 侧 IOB 提供的信号反相。

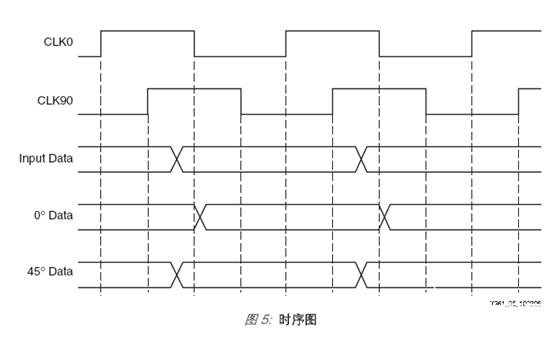

Virtex-4 和 Virtex-5 器件中的每个 IOB 都有一个 IDELAY 基元与之关联。不过,由于IBUFDS_DIFF_OUT 缓冲器从 LVDS 对的两个不同 IOB 提供两个输入信号副本,而这两个比特流副本可经不同的 IDELAY 基元分别发送,这致使它们有不同的延迟量。IBUFDS_DIFF_OUT的 P 侧提供的比特流真实副本被与其关联的 IDELAY 延迟八分之一个位周期。用于IBUFDS_DIFF_OUT 反相输出的 IDELAY 设置为零延迟。这两个 IDELAY 模块提供两个不同的比特流“相位”。过采样器用两个时钟相位的双沿对这两个比特流相位分别采样,所以每个位周期可采集比特流八次,如图5 所示。

乍看似乎奇怪的是,标为有零相移延迟的数据其实是来自有八分之一位周期延迟的 IDELAY 模块,而标为有 45 度相移的数据却是来自有零延迟的 IDELAY 模块。但这是正确的。图5 中的CLK0 说明了这一示例。比特流的两个相位均在 CLK0 的上升时钟沿采样。从有八分之一位周期延迟的 IDELAY 采集的样本代表比从有零延迟的 IDELAY 采集到的样本“早”八分之一位周期的输入数据。

还有一点可能看似奇怪的是,使用两个 IDELAY,却将其中一个设置为零延迟。但这样做是为了确保两个信号副本使用同等布线资源,从而尽量减轻数据信号两个相位间的歪斜。

如第 4 页图3 所示,各样本通过由三个触发器构成的流水线送至主时钟域(零度时钟的上升沿)。第一触发器是采样触发器,偶尔会因为比特流异步采样而处于亚稳态。为了规避亚稳态引起的问题,本设计在流水线中第一与第二触发器之间至少让出四分之三时钟周期,以便给第一触发器留出时间在样本被时钟驱动进入第二触发器之前稳定下来。当样本被时钟驱动进入流水线中第三触发器时,样本已送入主时钟域,而且亚稳态已解除。

如果包括流水线中第一触发器上的延迟量,任何样本通过流水线的总延迟都恰好是两个时钟周期。以 315 度的样本为例,第一触发器使用 90 度时钟的下降沿,所以为该触发器被时钟驱动四分之三时钟周期。第一到第二触发器的延迟是四分之三时钟周期,而第二到第三触发器的延迟是半个时钟周期。加起来恰好是两个时钟周期。

与第 3 页图2 所示的双 DCM 技术相比,这种基于 IDELAY 的过采样技术在性能及资源使用方面都有优势。显然,这种技术少用了一个 DCM 和两个全局时钟。因为只使用一个 DCM,所以各时钟相位之间相对更稳定。因为 IDELAY 基元不会加剧抖动,所以各数据相位之间相对抖动甚微。因此,这种过采样技术可以提供更精准的可重复性比特流采样,并且可以提高接收器的抖动容限。

IDELAY 基元可提供每 tap 78 ps 的高精度延迟。延迟值 6 提供 468 ps 的延迟,非常接近 270Mb/s 位周期的八分之一 (463 ps)。270 Mb/s 是视频应用的常用比特率,在参考设计中用作示范比特率。

如果 FPGA 正在接收比特率相同的多个异步比特流,就可以用 DCM 提供的两个全局时钟相位作为时钟来驱动所有比特流的过采样器。因此,这种技术对于接收比特率相同的多个比特流非常有效。

第 4 页图3 中的 DCM 不能在进行时钟乘法运算的同时提供两个相隔 90 度的时钟相位。因此,DCM 的输入端需要一个比特率时钟。不过,Virtex-5 器件时钟管理管道中的 PLL 可以同时对输入的时钟进行乘法运算并提供两个不同的时钟相位,并且允许使用较低频率的输入参考时钟。

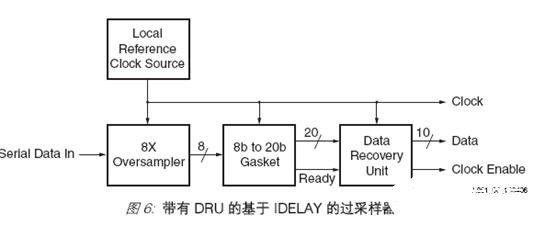

图6 所示为连接至 DRU 的基于 IDELAY 的过采样器设计。这种 DRU 支持 8 倍过采样,当初的开发目的是在 RocketIO 收发器上用作过采样器。由于这一原因,它预置一个 20 位的输入矢量,所以就需要少量接口逻辑将采样器的 8 位输出端与 DRU 的 20 位输入端衔接起来。DRU在其输出端口生成 10 位的恢复数据字,同时生成一个信号,一旦数据字生效则该信号被置位。DRU 还可以生成 20 位的输出字。

参考设计

可以从 http://www.xilinx.com/cn/bvdocs/appnotes/xapp861.zip 下载参考设计文件。

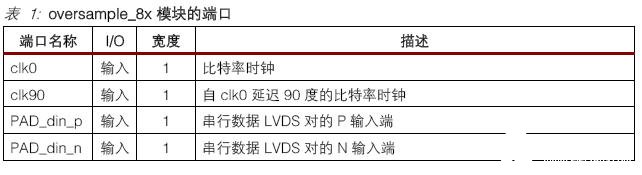

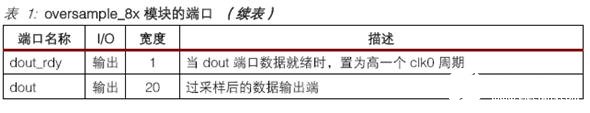

过采样器模块称为 oversample_8x。其端口如表1 所示。

oversample_8x 模块还接受一个称为 IDELAY_45_DEGREES 的 Verilog 参数或 VHDL 类属参数,其默认值为 6。此值设置 IDELAY 的延迟量,以便在数据上获得一个 45 度的相移(八分之一位周期)。默认值 6 是对应 270 Mb/s 的正确 IDELAY 值 (78 ps * 6 ≈ (1 / 270 MHz) / 8)。如果比特率是 270 Mb/s 以外的其他值,就必须将 IDELAY_45_DEGREES 的正确值传输到该模块。

在内部差分终端 (DIFF_TERM) 开启的状态下,用 IOSTANDARD 属性值“LVDS_25”在oversample_8x 模块内实例化 IBUFDS_DIFF_OUT 输入缓冲器。如果应用要求不同的IOSTANDARD 属性或者要求关闭差分终端,则必须修改在 oversample_8x 模块中的IBUFDS_DIFF_OUT 缓冲器上设置的约束条件.IBUFDS_DIFF_OUT 只能用于 LVDS I/O 标准。

DRU 模块称为 os48_1011x20bTo10b_top2。其端口如表2 所示。名称以 A/B 开头的所有端口实际上都是双端口,其中一个对应 A 通道,另一个对应 B 通道。

DRU 的 A_recclk 和 B_recclk 端口必须由连接到各自 oversample_8x 模块 clk0 输入端口的同样的比特率时钟驱动。过采样器的 dout 和 dout_rdy 端口分别驱动 DRU 的 A/B_din20b 和A/B_en 端口。

为 DRU 正确指定信号位顺序至关重要。DRU 有两个位顺序输入端,一个指定 DRU 输入数据的位顺序,另一个指定 DRU 输出数据的位顺序。不能独立地指定 DRU 两个通道的位顺序。

10 位和 20 位输出端口均由 DRU 提供。两个端口始终处于活动状态,应用可选择使用任一个。各通道的 10 位和 20 位端口各有其输出使能,通常用作对下游逻辑的时钟使能。在典型应用中,驱动 oversample_8x 的 clk0 端口和 DRU 的 A/B_recclk 端口的比特率参考时钟用作接收器中下游逻辑的时钟,如解码器、成帧器和查错器等。当 DRU 的输出端口上有新的恢复数据字时,用 DRU 的时钟使能输出仅在这些时钟周期上启用下游逻辑。

模块 FPGA 资源的利用

表3 所示为实现完整的 8 倍过采样单元和数据恢复单元所需的 FPGA 资源。DRU 基于 BlockRAM。因为 Xilinx FPGA 中的 Block RAM 有双端口,所以 DRU 设计可以处理两个异步数据流。这样,同样数量的 Block RAM 既可以处理一个异步通道,也可以处理两个异步通道。在Virtex-4 器件中,无论 DRU 处理一个还是两个通道,都需要有两个 RAMB16 Block RAM。在Virtex-5 器件中,DRU 需要一个半 RAMB36 Block RAM (一个 RAMB18,一个 RAMB36)。

表3 中的结果是用 ISE8.2 获得的,其 XST 设置为面积优化,串行比特率为 270 Mb/s。在Virtex-4 和 Virtex-5 FPGA 的最低速度级别下,如果将 XST 设置为面积优化则有可能满足比特率为 270 Mb/s 的时序。

时序

IDELAY 基元的粒度为 78 ps。因此,由于 78 ps 的粒度与本技术要求的八分之一位周期延迟刚好相符,有些比特率值相对于其他值就会更适合这一技术。例如,比特率为 270 Mb/s 时,八分之一位周期约为 463 ps,而 6 * 78 ps 为 468 ps。因此,使用延迟值 6 会使 IDELAY 对信号的延迟量非常接近八分之一位周期。

这种技术不能用于 DCM 的 CLKFX 输出端。其主要原因是,时钟相位的抖动要尽可能低,而DCM 的 CLKFX 输出端的抖动要远远高于 CLK0 和 CLK90 输出端。在 Virtex-5 器件中,也可以用时钟管理管道中的 PLL 提供这两个时钟相位。

重要的是,要妥善约束 DRU 和下游逻辑的时序。这通常需要多周期时序约束,因为所用时钟是比特率时钟,而 DRU 和下游逻辑则往往通过使用时钟使能而在字速率下运行。两个不同的时钟使能被用到,因此必须给予妥善约束。

过采样器对 DRU 的 A_en 或 B_en 输入生成一个时钟使能 (dout_rdy),以使其仅当准备好向DRU 输入 20 位过采样数据时 DRU 才会被时钟驱动。如果过采样器的实例名为 OVRSAMPLE,则使用以下约束指明每 20 个时钟(称为“sclk”)周期 DRU 输入才会被时钟驱动一次:

NET “sclk” TNM_NET = BIT_CLK;

TIMESPEC TS_BIT_CLK = PERIOD BIT_CLK 270 MHz HIGH 50 %;

NET “OVRSAMPLE/period《0》” TNM = DRU_IN_CE;

TIMESPEC TS_DRU_IN_CE = FROM DRU_IN_CE TO DRU_IN_CE BIT_CLK / 20;

串行时钟的 PERIOD 约束是以频率给定,从而使时钟使能的 TIMESPEC 等于串行时钟的TIMESPEC 除以 20。如果串行时钟的 PERIOD 约束是以周期而非频率给定,则时钟使能的TIMESPEC 必须等于串行时钟的 TIMESPEC 乘以 20。

另一个时钟使能由 DRU 在其使能输出端生成。DRU 有四个输出端使能,每通道两个。在每通道两个输出端使能中,一个对应于 10 位的输出,另一个对应于 20 位的输出。10 位的输出端口使能(A_dout10bEn 或 B_dout10bEn)平均每 10 个串行时钟周期被置位一次。不过,因为实际数据比特率对于串行时钟为异步,所以在 10 位输出端使能的各次置位之间偶尔会有 9 或11 个时钟周期。实际上,DRU 也可以在 10 位输出端使能的各次置位之间生成短至 5 个时钟周期的数据字。因此,对于由 DRU 时钟使能输出端驱动的逻辑,应该以所希望的最小时序编写其多周期时序约束。如果使用 DRU 的 10 位时钟使能输出端,并且信号名为“rx_ce”,那么以下时序约束可以妥善约束由 rx_ce 信号启用的 DRU 下游的任何逻辑。有必要在 Verilog 或VHDL 代码中对来自 DRU 的时钟使能信号应用一个 KEEP 约束,以使时钟使能将源代码保持为其给定的名称,从而可以在用户约束文件 (UCF) 中使用同样的名称。

NET “rx_ce” TNM = RXCE;

TIMESPEC TS_RXCE = FROM RXCE TO RXCE BIT_CLK / 5;

位置约束

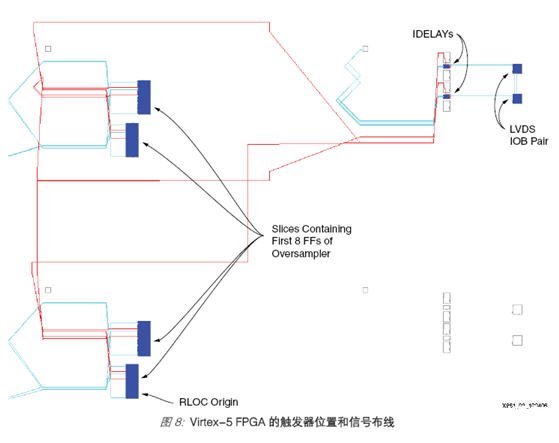

要从过采样器中获得良好性能,重要的是应将第一组的八个触发器(即直接从 IDELAY 基元输出端采集数据的触发器)放置在尽量靠近 IDELAY 基元处,并且从两个 IDELAY 基元到八个触发器的布线对于所有八个触发器来说应尽量相同。过采样器模块应设计成允许在约束文件中放置一个 RLOC 起点,以约束这第一组的八个触发器。应将 RLOC 起点设置成使触发器在 CLB中的位置尽可能紧靠 IDELAY 基元的左侧,因为这样放置可提供最直接的信号布线。如果不可能将触发器置于 IDELAY 基元的左侧,可以将其放在紧靠其右侧的位置,只是性能会稍有降低。

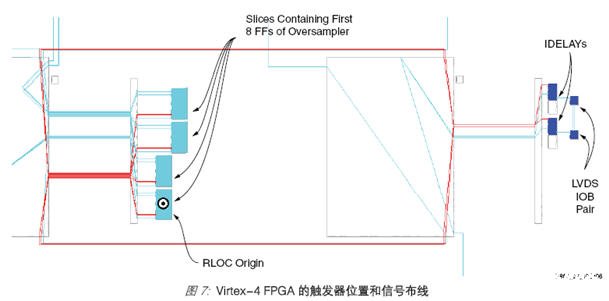

图7 所示为触发器紧靠 IDELAY 基元左侧的 Virtex-4 器件。图中以红色表示从两个 IDELAY 基元到触发器的数据信号布线。

XAPP861 (v1.0) 2006 年 10 月 13 日www.xilinx.com/cn 11

R 以下约束显示如何将设计中的两个 oversample_8x 模块分别指定给不同的 U_SET,以及如何对其指定 RLOC_ORIGIN 约束,以将其置于各自 IOB 的旁边。在本示例中,两个oversample_8x 模块的实例名分别为 OVRSAMPLE1 和 OVRSAMPLE2。

INST “OVRSAMPLE1” U_SET=USET_OVR1;

INST “OVRSAMPLE1” RLOC_ORIGIN = X0Y24;

INST “OVRSAMPLE2” U_SET=USET_OVR2;

INST “OVRSAMPLE2” RLOC_ORIGIN = X50Y24;

结论

本文所述技术使用 Virtex-4 和 Virtex-5 器件中各 IOB 内置的 IDELAY 资源来实现用于异步串行比特流的高效高性能8倍过采样器。当用多个 DCM 生成时钟相位时,这种技术可以提供比多时钟相位法更高的采样精度。因为 IDELAY 资源可以为各比特流提供更多采样点,所以只需一个 DCM 和两个全局时钟即可提供对以同样比特率运行的任意数量的异步比特流进行 8 倍采样所需的所有时钟。

责任编辑:gt

-

高性能的可编程电源管理解决方案2012-08-20 2585

-

基于lmk03806的高性能可编程时钟发生器的设计与fpga实现 毕...2013-05-03 3358

-

高精度PWM可编程的_RGB_LED_驱动芯片的设计实现2013-09-29 4470

-

高精度可编程电压源2019-07-25 2518

-

如何设计一种基于CPLD的可编程高精度CCD信号发生器?2021-04-13 1276

-

基于AD9833的高精度可编程波形发生器系统设计2009-05-26 1251

-

高速可编程遥感卫星数据模拟源的设计与实现2010-08-09 1160

-

用DA转换器实现高精度可编程增益放大器2010-03-04 4141

-

基于CPLD的数字可编程延迟单元的设计2011-09-20 1124

-

基于FPGA的实时可编程高精度信号源设计2012-05-28 1347

-

AD9833型高精度可编程波形发生器及其应用2016-01-22 1634

-

新一代可编程交流电源上市,高精度、高性能、多功能2020-03-02 1658

-

PWR系列高性能可编程交流电源的相关功能介绍2020-03-08 3902

-

AN-260:使用数字可编程延迟发生器2021-04-14 768

-

可编程高精度直流电源的优势及应用2023-11-10 2242

全部0条评论

快来发表一下你的评论吧 !