基于级联结构和VHDL语言的IIR数字滤波器在FPGA上实现设计

FPGA/ASIC技术

描述

IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同时钟速度下可以提供更好的带外衰减特性。下面介绍一种在FPGA上实现IIR数字滤波器的方法。

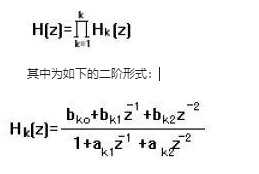

IIR数字滤波器的结构 任意阶的IIR滤波器可通过数学分解,表示为:

这样就可以将任意阶的IIR滤波器通过若干二阶网络(也称为滤波器的二阶基本节)级联起来构成,其结构如图1所示。其中,代表第i级的二阶网络。

对于每一个二阶基本节,可以转置直接II型结构加以实现,如图2所示。

采用这种级联结构实现IIR滤波器的优点是每一个基本节只是关系到滤波器的某一对极点和一对零点,调整系数a0i、a1i、a2i,只单独地调整了滤波器第i对零点而不影响其他任何零、极点。同样,调整b1i、b2i系数、也只单独调整了第i对极点。因此,这种结构便于准确地实现滤波器的零、极点,也便于调整滤波器的频率响应性能。这种结构的另一个优点是存储单元需要较少,在硬件实现时,可以用一个二阶节进行时分复用,从而降低对FPGA硬件资源的要求。[page]

IIR数字滤波器的设计

利用MATLAB信号处理工具箱中的滤波器设计和分析工具(EDATool)可以很方便地设计出符合应用要求的未经量化的IIR滤波器。需要将MATLAB设计出的IIR滤波器进一步分解和量化,从而获得可用FPGA实现的滤波器系数。

由于采用了级联结构,因此如何将滤波器的每一个极点和零点相组合,从而使得数字滤波器输出所含的噪声最小是个十分关键的问题。为了产生最优的量化后的IIR数字滤波器,采用如下步骤进行设计:

首先计算整体传递函数的零极点;

选取具有最大幅度的极点以及距离它最近的零点,使用它们组成一个二阶基本节的传递函数;

对于剩下的极点和零点采用与(2)相类似的步骤,直至形成所有的二阶基本节。

通过上面三步法进行的设计可以保证IIR数字滤波器中N位乘法器产生的量化舍入误差最小。 为了设计出可用FPGA实现的数字滤波器,需要对上一步分解获得的二阶基本节的滤波器系数进行量化,即用一个固定的字长加以表示。量化过程中由于存在不同程度的量化误差,由此会导致滤波器的频率响应出现偏差,严重时会使IIR滤波器的极点移到单位圆之外,系统因而失去稳定性。为了获得最优的滤波器系数,采用以下步骤进行量化:

计算每个系数的绝对值;

查找出每个系数绝对值中的最大值;

计算比此绝对值大的最小整数;

对(3)的结果取反获得负整数;

计算需要表示此整数的最小位数;

计算用于表示系数值分数部分的余下位数。

除了系数存在量化误差,数字滤波器运算过程中有限字长效应也会造成误差,因此对滤波器中乘法器、加法器及寄存器的数据宽度要也进行合理的设计,以防止产生极限环现象和溢出振荡。

IIR数字滤波器的VHDL描述

由上一节设计出来的IIR数字滤波器可以进一步用VHDL语言加以描述,通过编译、功能仿真、综合和时序仿真之后就可以在FPGA上实现了。由于采用了级联结构,每一个二阶基本节的VHDL描述都是类似的,只是滤波器的系数有所不同,下面着重讨论二阶基本节的VHDL描述。

采用VHDL描述的二阶基本节的顶层结构如图3所示。数据在执行单元内进行处理。执行单元内部包含算术和逻辑单元以及一些寄存器;算术和逻辑单元主要由串行乘法器和累加器组成;存储器包括工作RAM和系数ROM两部分,分别用于存放计算的中间结果和滤波器的系数;存储器和执行单元通过内部总线相连接;控制模块包括程序ROM和程序控制单元,程序ROM中存放有滤波算法的程序,程序控制单元用于解释指令并为数据处理模块产生控制信号。

此结构既可以接收串行输入的数据,也可以接收并行输入的数据,通过SEL进行设置。外部CPU可以通过READ信号来访问滤波器的计算结果,另外,外部CPU也可以通过地址总线A[3:0]对内部的存储器进行访问,用WRITE信号对滤波器系数进行写操作,这样外部CPU就可以根据自己的需要对滤波器进行配置,灵活地实现各种功能。 各信号的含义如下:

CLK:系统时钟;

RES:异步全局复位信号,低有效;

SDATA:串行输入数据;

PDATA:并行输入数据;

SEL:设置输入数据为并行还是串行;

READ:读信号,低有效;

WRITE:写信号,低有效;

SRES:同步复位信号,高有效;

CLKI:外部CPU时钟;

A[3:0]:外部CPU访问内部寄存器的地址总线;

OUT:输出数据。

内部算术与逻辑单元是整个滤波器的核心,它的结构如图4所示。

计算过程是,X、Y为输入数据,通过选择器进入乘法器,算术与逻辑单元从系数ROM中读取滤波器的系数用以输入数据相乘,相乘的结果与前一步的结果相加进入累加器,累加器读取上一步计算的中间结果A并计算,最后将此步计算的结果M存入到RAM中去。

结语

本文介绍了一种采用级联结构在FPGA上实现IIR数字滤波器的方法。在实际使用中,可以根据不同精度要求,方便地对该IIR滤波器进行修改以满足不同的指标要求,灵活地组成任意阶不同类型的滤波器。同时,在系统运行中,外部CPU可以灵活修改滤波器系数,改变滤波器的频率响应,满足特定的应用要求。

责任编辑:gt

-

怎么实现基于Matlab的IIR数字滤波器设计?2021-05-31 1764

-

如何采用级联结构在FPGA上实现IIR数字滤波器?2021-04-15 1907

-

请问如何去设计IIR数字滤波器?2021-04-14 1986

-

数字滤波器-IIR滤波器原理介绍&Verilog HDL设计2020-09-27 6950

-

如何使用FPGA实现IIR数字滤波器的设计2020-08-06 1377

-

基于FPGA和MATLAB实现IIR数字滤波器的设计和仿真验证分析2020-07-23 3778

-

IIR数字滤波器的FPGA实现2018-03-02 1185

-

IIR数字滤波器设计2015-12-25 1040

-

零基础学FPGA(三十) IIR数字滤波器的FPGA实现笔记2015-07-26 35308

-

IIR数字滤波器的Matlab和FPGA实现2012-08-20 5953

-

采用HDPLD实现高速IIR数字滤波器2009-09-01 545

-

数字滤波器的结构2009-01-07 994

-

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器2008-01-16 2935

全部0条评论

快来发表一下你的评论吧 !