如何进行多层PCB板的层叠设计

EDA/IC设计

描述

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。

本节将介绍多层PCB板层叠结构的相关内容。

对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题;

层的排布一般原则:

1、确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到最佳的平衡。对于有经验的设计人员来说,在完成元器件的预布局后,会对PCB的布线瓶颈处进行重点分析。结合其他EDA工具分析电路板的布线密度;再综合有特殊布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后根据电源的种类、隔离和抗干扰的要求来确定内电层的数目。这样,整个电路板的板层数目就基本确定了。

2、元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;敏感信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间。这样两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。

3、所有信号层尽可能与地平面相邻;

4、尽量避免两信号层直接相邻;相邻的信号层之间容易引入串扰,从而导致电路功能失效。在两信号层之间加入地平面可以有效地避免串扰。

5、主电源尽可能与其对应地相邻;

6、兼顾层压结构对称。

7、对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:

● 元件面、焊接面为完整的地平面(屏蔽);

●无相邻平行布线层;

●所有信号层尽可能与地平面相邻;

●关键信号与地层相邻,不跨分割区。

注:具体PCB的层的设置时,要对以上原则进行灵活掌握,在领会以上原则的基础上,根据实际单板的需求,如:是否需要一关键布线层、电源、地平面的分割情况等,确定层的排布,切忌生搬硬套,或抠住一点不放。

8、多个接地的内电层可以有效地降低接地阻抗。例如,A信号层和B信号层采用各自单独的地平面,可以有效地降低共模干扰。

常用的层叠结构:

4层板

下面通过 4 层板的例子来说明如何优选各种层叠结构的排列组合方式。

对于常用的 4 层板来说,有以下几种层叠方式(从顶层到底层)。

(1)Siganl_1(Top),GND(Inner_1),POWER(Inner_2),Siganl_2(Bottom)。

(2)Siganl_1(Top),POWER(Inner_1),GND(Inner_2),Siganl_2(Bottom)。

(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。

显然,方案 3 电源层和地层缺乏有效的耦合,不应该被采用。

那么方案 1 和方案 2 应该如何进行选择呢?

一般情况下,设计人员都会选择方案 1 作为 4层板的结构。选择的原因并非方案 2 不可被采用,而是一般的 PCB 板都只在顶层放置元器件,所以采用方案 1 较为妥当。

但是当在顶层和底层都需要放置元器件,而且内部电源层和地层之间的介质厚度较大,耦合不佳时,就需要考虑哪一层布置的信号线较少。对于方案 1而言,底层的信号线较少,可以采用大面积的铜膜来与 POWER 层耦合;反之,如果元器件主要布置在底层,则应该选用方案 2 来制板。

如果采用层叠结构,那么电源层和地线层本身就已经耦合,考虑对称性的要求,一般采用方案 1。

6层板

在完成 4 层板的层叠结构分析后,下面通过一个 6 层板组合方式的例子来说明 6 层板层叠结构的排列组合方式和优选方法。

(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。

方案 1 采用了 4 层信号层和 2 层内部电源/接地层,具有较多的信号层,有利于元器件之间的布线工作,但是该方案的缺陷也较为明显,表现为以下两方面。

① 电源层和地线层分隔较远,没有充分耦合。

② 信号层 Siganl_2(Inner_2)和 Siganl_3(Inner_3)直接相邻,信号隔离性不好,容易发生串扰。

(2)Siganl_1(Top),Siganl_2(Inner_1),POWER(Inner_2),GND(Inner_3),Siganl_3(Inner_4),Siganl_4(Bottom)。

方案 2 相对于方案 1,电源层和地线层有了充分的耦合,比方案 1 有一定的优势,但是

Siganl_1(Top)和 Siganl_2(Inner_1)以及 Siganl_3(Inner_4)和 Siganl_4(Bottom)信号层直接相邻,信号隔离不好,容易发生串扰的问题并没有得到解决。

(3)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),POWER(Inner_3),GND(Inner_4),Siganl_3(Bottom)。

相对于方案 1 和方案 2,方案 3 减少了一个信号层,多了一个内电层,虽然可供布线的层面减少了,但是该方案解决了方案 1 和方案 2 共有的缺陷。

① 电源层和地线层紧密耦合。

② 每个信号层都与内电层直接相邻,与其他信号层均有有效的隔离,不易发生串扰。

③ Siganl_2(Inner_2)和两个内电层 GND(Inner_1)和 POWER(Inner_3)相邻,可以用来传输高速信号。两个内电层可以有效地屏蔽外界对 Siganl_2(Inner_2)层的干扰和Siganl_2(Inner_2)对外界的干扰。

综合各个方面,方案 3 显然是最优化的一种,同时,方案 3 也是 6 层板常用的层叠结构。通过对以上两个例子的分析,相信读者已经对层叠结构有了一定的认识,但是在有些时候,某一个方案并不能满足所有的要求,这就需要考虑各项设计原则的优先级问题。遗憾的是由于电路板的板层设计和实际电路的特点密切相关,不同电路的抗干扰性能和设计侧重点各有所不同,所以事实上这些原则并没有确定的优先级可供参考。但可以确定的是,设计原则 2(内部电源层和地层之间应该紧密耦合)在设计时需要首先得到满足,另外如果电路中需要传输高速信号,那么设计原则 3(电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间)就必须得到满足。

10层板

PCB典型10层板设计

一般通用的布线顺序是TOP--GND---信号层---电源层---GND---信号层---电源层---信号层---GND---BOTTOM

本身这个布线顺序并不一定是固定的,但是有一些标准和原则来约束:如top层和bottom的相邻层用GND,确保单板的EMC特性;如每个信号层优选使用GND层做参考平面;整个单板都用到的电源优先铺整块铜皮;易受干扰的、高速的、沿跳变的优选走内层等等。

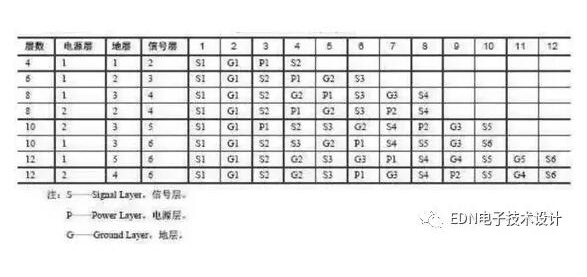

下表给出了多层板层叠结构的参考方案,供参考。

PCB设计之叠层结构改善案例(From金百泽科技)

问题点

产品有8组网口与光口,测试时发现第八组光口与芯片间的信号调试不通,导致光口8调试不通,无法工作,其他7组光口通信正常。

1、问题点确认

根据客户端提供的信息,确认为L6层光口8与芯片8之间的两条差分阻抗线调试不通;

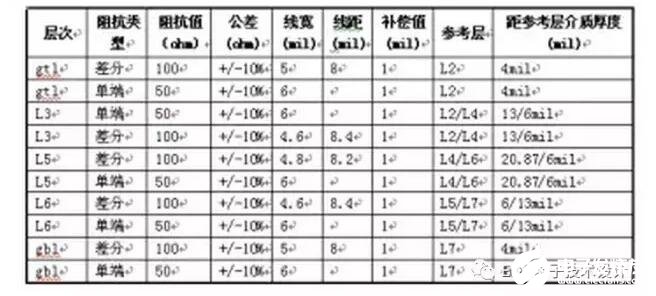

2、客户提供的叠构与设计要求

改善措施

影响阻抗信号因素分析:

线路图分析:客户L56层阻抗设计较为特殊,L6层阻抗参考L5/L7层,L5层阻抗参考L4/L6层,其中L5/L6层互为参考层,中间未做地层屏蔽,光口8与芯片8之间线路较长,L6层与L5层间存在较长的平行信号线(约30%长度)容易造成相互干扰,从而影响了阻抗的精准度,阻抗线的设计屏蔽层不完整,也造成阻抗的不连续性,其他7组部分也有相似问题,但相对较轻微。

L56层存在特殊设计(均为信号层,存在差分阻抗平行设计、相邻阻抗层间未设计参考地层),客户端未充分考虑相邻层走线存在的干扰,导致调试不通问题。

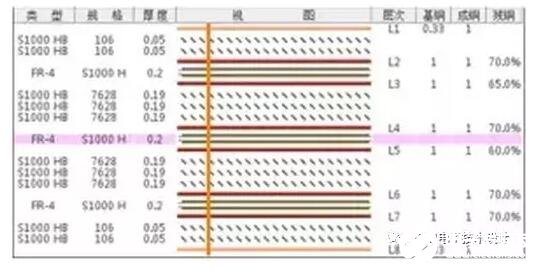

与客户沟通对叠层进行优化,将L45、L56、L67层结构进行了调整,介质层厚度分别由20.87mil、6mil、13mil 调整为5.12mil、22.44mil、5.12mil,将而L4、L7间的参考地层间的距离拉近,L56层互为参考且屏蔽不足的线路层距离拉远,减少干扰。

优化后的叠层结构:

优化后的阻抗匹配:

改善效果

通过调整叠层结构,拉大L56层相邻信号层之间的距离,串扰造成的系统故障问题得到解决。

责任编辑;zl

-

PCB层叠设计解读2020-03-13 7503

-

多层板PCB设计教程完整版2012-08-22 20508

-

多层PCB板的层叠结构规则2015-01-09 4050

-

PCB层叠的认识2020-03-16 4296

-

PCB多层电路板层叠设计2020-07-23 10353

-

多层电路板PCB层叠结构和阻抗设计2022-11-15 1505

-

适合初学者的多层板PCB设计资料2023-09-20 775

-

多层PCB板的选择、叠加原则和设计详解2018-06-24 12331

-

多层线路板如何设计?多层板PCB设计教程完整版详细资料免费下载2018-08-27 1764

-

多层PCB电路板的设计指南资料免费下载2019-05-23 1063

-

多层PCB板的层叠结构以及叠加原则解析2019-10-04 9488

-

多层PCB板的层叠的设计步骤解析2020-01-02 5966

-

PCB层叠设计需考虑的因素_PCB层叠设计的一般规则2020-03-21 3647

-

PCB层叠设计需考虑的因素和规则2020-11-03 3201

-

PCB多层板为什么都是偶数层?2023-12-07 1923

全部0条评论

快来发表一下你的评论吧 !