使用PCB板的堆叠与分层时应遵循哪些原则

EDA/IC设计

描述

1.概述

多层印制板为了有更好的电磁兼容性设计。使得印制板在正常工作时能满足电磁兼容和敏感度标准。正确的堆叠有助于屏蔽和抑制EMI。

2.多层印制板设计基础。

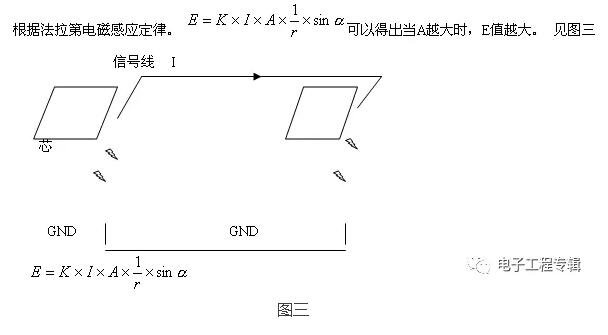

多层印制板的电磁兼容分析可以基于克希霍夫定律和法拉第电磁感应定律。

根据克希霍夫定律,任何时域信号由源到负载的传输都必须有一个最低阻抗的路径。见图一。图中I=I′,大小相等,方向相反。图中I我们称为信号电流,I′称为映象电流,而I′所在的层我们称为映象平面层。如果信号电流下方是电源层(POWER),此时的映象电流回路是通过电容耦合所达到的。见图二。

根据以上两个定律,我们得出在多层印制板分层及堆叠中应遵循以下基本原则:

① 电源平面应尽量靠近接地平面,并应在接地平面之下。

② 布线层应安排与映象平面层相邻。

③ 电源与地层阻抗最低。

④ 在中间层形成带状线,表面形成微带线。两者特性不同。

⑤ 重要信号线应紧临地层。

3. PCB板的堆叠与分层

① 二层板。

此板仅能用于低速设计。EMC比较差。

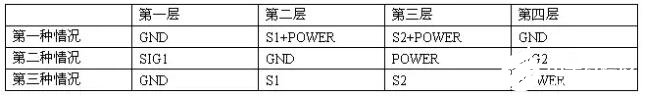

② 四层板。

由以下几种叠层顺序。下面分别把各种不同的叠层优劣作说明。

表一

注:S1 信号布线一层,S2 信号布线二层;GND 地层;POWER 电源层

第一种情况,应当是四层板中最好的一种情况。因为外层是地层,对EMI有屏蔽作用,同时电源层同地层也可靠得很近,使得电源内阻较小,取得最佳效果。但第一种情况不能用于当本板密度比较大的情况。因为这样一来,就不能保证第一层地的完整性,这样第二层信号会变得更差。另外,此种结构也不能用于全板功耗比较大的情况。

表中的第二种情况,是我们平时最常用的一种方式。从板的结构上,也不适用于高速数字电路设计。因为在这种结构中,不易保持低电源阻抗。以一个板2毫米为例:要求Z0=50ohm. 以线宽为8mil.铜箔厚为35цm。这样信号一层与地层中间是0.14mm。而地层与电源层为1.58mm。这样就大大的增加了电源的内阻。在此种结构中,由于辐射是向空间的,需加屏蔽板,才能减少EMI。

表中第三种情况,S1层上信号线质量最好。S2次之。对EMI有屏蔽作用。但电源阻抗较大。此板能用于全板功耗大而该板是干扰源或者说紧邻着干扰源的情况下。

③ 六层板

表二

A种情况,是常见的方式之一,S1是比较好的布线层。S2次之。但电源平面阻抗较差。布线时应注意S2对S3层的影响。

B种情况,S2层为好的布线层,S3层次之。电源平面阻抗较好。

C种情况,这种情况是六层板中最好的情况,S1,S2,S3都是好的布线层。电源平面阻抗较好。美中不足的是布线层同前两种情况少了一层。

D种情况,在六层板中,性能虽优于前三种,但布线层少于前两种。此种情况多在背板中使用。

④ 八层板

表三

八层板,如果要有6个信号层,以A种情况为最好。但此种排列不宜用于高速数字电路设计。如果是5个信号层,以C种情况为最好。在这种情况中,S1,S2,S3都是比较好的布线层。同时电源平面阻抗也比较低。如果是4个信号层,以表三中B种情况为最好。每个信号层都是良好布线层。在这几种情况中,相邻信号层应布线。

⑤ 十层板

表四

十层板如果有6个信号层,有A,B,C三种叠层顺序。A种情况为最好,C种次之,B种情况最差。其它没有列出的情况,比这几种情况更差。在A种情况中,S1,S6是比较好的布线层。S2,S3,S5次之。这中间要特别指出的是,A同C,A种情况之所以好于C种情况,主要原因是因为在C种情况中,GND层同POWER层的距离是由S5同GND层距离决定的。这样就不一定能保证GND层同POWER层的电源平面阻抗最小。D种情况应当说是十层板中综合性能最好的叠层顺序。每个信号层都是优良的布线层。E、F多用于背板。其中F种情况对EMC的屏蔽作用要好于E。不足之处是在于两信号层相接,在布线上要注意。

总之,PCB的分层及叠层是一个比较复杂的事情。有多方面的因素要考虑。但我们应当记住我们要完成的功能,需要那些关键因素。这样才能找到一个符合我们要求的印制板分层及叠层顺。

责任编辑;zl

-

PCB布板中PCB分层堆叠在控制EMI辐射中的作用和设计技巧2016-12-29 2087

-

详解PCB分层策略及PCB多层板的设计原则2022-12-29 5264

-

PCB分层堆叠在控制EMI辐射中的作用和设计技巧2013-08-28 2290

-

正确使用PCB的分层和堆叠的方法2017-04-12 8325

-

利用 PCB 分层堆叠控制 EMI 辐射2018-06-23 2446

-

正确使用PCB的分层和堆叠2018-09-20 1814

-

PCB的分层和堆叠你知道怎么正确使用吗2019-02-18 3141

-

利用PCB分层堆叠控制EMI辐射2019-08-19 1990

-

【设计技巧】利用PCB分层堆叠控制EMI辐射2019-08-22 1910

-

讨论:PCB分层堆叠在控制EMI辐射中的作用和设计技巧2019-09-06 4850

-

PCB中如何利用分层堆叠控制EMI2019-10-03 3201

-

基于PCB分层堆叠的EMI抑制方法2020-03-16 2999

-

请问一下PCB设计的布局与导线应遵循哪些原则呢?2023-04-10 863

-

通过PCB分层堆叠设计控制EMI辐射2016-11-10 840

-

如何利用PCB分层堆叠控制EMI辐射?2023-10-23 1678

全部0条评论

快来发表一下你的评论吧 !