等效时间采样技术的原理作用及采用FPGA器件实现系统的设计

可编程逻辑

描述

在现代电子测量、通讯系统以及生物医学等领域,经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不失真采集,根据奈奎斯特定理, 采样频率必须为信号频率的2 倍以上,但在电阻抗多频及参数成像技术中正交序列数字解调法的抗噪性能对信号每周期的采样点数决定,采样点数越多,抗噪性能越高。当采样信号频率很高时,为了在被采样信号的一周期内多采样,就需要提高采样时钟的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。

1 、等效时间采样原理

等效时间采样技术是把周期性或准周期性的高频、快速信号变换为低频的慢速信号。在电路上只对取样前的电路具有高频的要求,大大降低采样变换后的信号处理、显示电路对速度的要求,简化了整个系统的设计难度。等效时间采样分为顺序采样(sequential equivalent sampling)、随机采样(random equivalent sampling) 以及结合这两种方式的混合等效采样(compound equivalent sampling)。分别介绍了两种硬件实现的等效时间采样中的顺序采样。

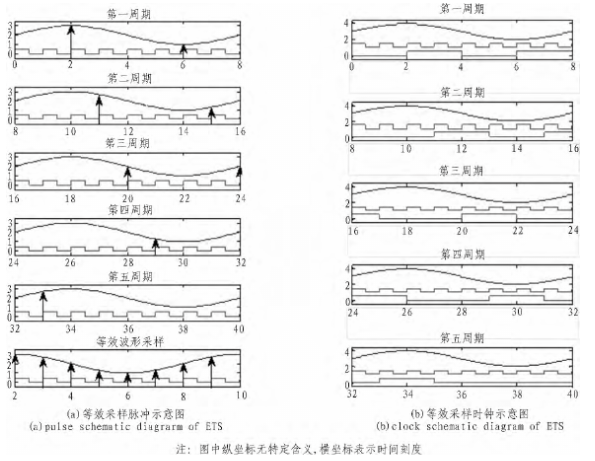

下面我将介绍等效时间采样中的混合时间采样,对于周期性信号的等效时间采样如图1(a)所示。

在第一周期中的横轴(时间)的第2 与第6 处的时钟上升沿对模拟信号进行采样,图中的箭头表示采样时刻。在一个周期中可以采集两个点,紧接着在第二个周期横轴的第11与第15 处的时钟上升沿对模拟信号进行采样。为了方便观察在此将第一至第五周期的波形纵向排列。可以看到第二周期比第一周的采样点距离各自周期起始点的时间晚了一个时钟周期。第三周期比第二周的采样点距离第三周期起始点的时间晚了一个时钟周期。在第四周期进行采样时我们可以发现第二个采样点已经进入第五周期。如果我们在第五周期周试图继续用以上方式进行采样即第五周期比第四周的采样点距离起始点的时间晚一个时钟周期,那么我们会发现在第五周期的采样起始点采样到的值重复了第一周期采样到的数值。所以此时我们可以终止采样那么我们就得到了如图1 中的第6 个波形示意图所表示的在一个周期的正弦波形中采到的8 个数据点。

等效时间采样中每个周期可以采集多个点时的理论依据,给出了等效时间采样中每个周期可以采集单个点时的理论依据。

我们通过将高频时钟进行分频已达到或者接近满足处理速度时钟要求。在图1(b)中幅度最小的时钟信号为采样时钟。由图1(b)可以很清楚的看到分频后的时钟波形,分频后的时钟波形在时钟的上升沿对信号进行采样,那么就会得到如图1(a)中所表示的等效时间采样。

图1 等效时间采样示意图

2 、基于FPGA的等效时间采样实现

2.1 系统硬件实现框图

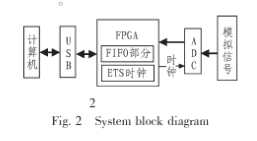

系统的总体框图如图2,FPGA 控制的等效采样时钟连接到ADC 器件的时钟部分,ADC 器件在时钟的控制下对宽带模拟信号进行采样,采集到的数据传送到FPGA 中的FIFO,FPGA 再将FPGA 中FIFO 的数据传递到USB 中的FIFO,然后USB 将USB 中FIFO 数据推送到计算机,计算机对接收到的数据进行重构处理。对于信号周期的获取,在电阻抗多频及参数成像技术中采集信号的周期是由发送信号的周期决定, 而对于其他复杂周期信号的周期获得可以通过所采用的方法获得。

图2 系统方案框图

2.2 等效时间采样时钟的程序实现

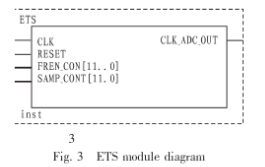

图3 展示了基于FPGA 生成的等效时间采样模块的输入端口与输出端口。其中CLK 表示高频时钟的输入,RESET表示的是复位输入端,FREN_CON 表示的是分频控制输入用于控制高频时钟的分频数,SANM_CONT 表示的是模拟信号的周期包含多少个高频时钟信号的波形,CLK_ADC_OUT 表示的是输出时钟端口,此端口连接到模数转换器件(ADC)的时钟输入端口。

图3 等效时间采样模块图

以下是实现等效时间采样所需时钟的代码:

SIGNAL SAMP_CONTS:STD_LOGIC_VECTOR (11

DOWNTO 0):=(OTHERS=》‘0’);

SIGNAL ADC_CLK_BANK:STD_LOGIC_VECTOR (11

DOWNTO 0):=(OTHERS=》‘0’);

SIGNAL CLK_CNT :INTEGER RANGE 0 TO 5000:=0;

SIGNAL CLK_TANK:STD_LOGIC:=‘0’;

SIGNAL EN :STD_LOGIC:=‘1’;

BEGIN

PROCESS(CLK,RESET)

BEGIN

IF RESET=‘1’ THEN EN‘0’);

SAMP_CONTS‘0’);

EN

3、 波形仿真

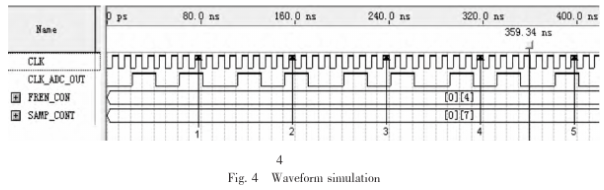

图4 中的波形仿真是以模拟信号的一周期等于8 个CLK 时钟周期,CLK_ADC_OUT 是对CLK 进行4 分频且分频后的时钟占空比为50%为假设的。1 号箭头指向的时钟上升沿标志着第一周期结束,上升沿之后进入第二周期。同理,2号箭头所指时钟的上升沿标志着第二周期的结束,上升沿之后标志着进入第三周期。

图4 波形仿真

在第一个周期中从CLK 的第一个上升沿开始计时同时对CLK 进行分频可以得到CLK_ADC_OUT 时钟信号, 在第一周期中在CLK 的第二个上升沿CLK_ADC_OUT 电平翻转(存在延时), 在第二周期中在第三个上升沿CLK_ADC_OUT电平翻转, 在第三个周期中在CLK 的第四个上升沿CLK_ADC_OUT 电平翻转。可以看出波形仿真图是对图1(a)、(b)两图表达时钟的实现。在这里应该注意到,在第一周期中虽然也有8 个CLK 的上升沿,但是并没有表示出如1 号箭头所指CLK 时钟上升沿之后与第二周期第一个CLK 时钟上升沿之间的波形。

4、 结论

本文介绍了等效时间采样的基本原理、系统实现的具体方案。等效时间采样技术实现了利用低速的ADC 器件对宽带模拟信号的采集, 降低了系统对ADC 器件的要求以及系统实现的复杂度。本文介绍的等效时间采样技术由于使用了FPGA 采样技术, 使得在被采样信号的一个周期中相较于一个周期仅能采集一个点的顺序等效时间采样有很大的提高,并且可以控制被采集信号一个周期中的采集点数从而可以根据后续器件处理速度实现变频控制采样。通过FPGA 实现等效采样时间,降低了系统实现的复杂度,同时可以十分方便的对代码进行修改使系统的调试更加简便。

责任编辑:gt

-

等效时间采样示波器与实时示波器的对比,有什么不同?2024-01-19 2884

-

什么是示波器的实时采样率?什么是示波器的等效时间采样?2023-10-17 3588

-

等效时间采样原理及基于FPGA的实现2023-09-15 4075

-

基于FPGA的等效时间采样原理的实现2023-07-29 1868

-

采用FPGA来实现SVPWM调制算法2022-01-20 8447

-

等效时间采样技术的原理作用及采用FPGA器件实现系统的设计2020-10-21 1825

-

利用单片机和FPGA器件实现等效和实时采样方式的数字示波器设计2019-05-05 3743

-

采用EDA技术的等效采样方案介绍2018-11-08 8301

-

基于FPGA实现高速ADC器件采样时序控制与实时存储2018-08-28 15090

-

等效采样2017-03-04 718

-

基于ARM的等效采样存储示波表设计2011-06-21 968

-

基于FPGA的等效采样存储示波器设计2011-03-16 714

-

基于EDA技术的等效采样的设计实现2010-08-03 483

-

基于单片机的等效采样示波器的设计2010-07-08 736

全部0条评论

快来发表一下你的评论吧 !