基于VersaClock6系列的多输出可编程时钟发生器的应用研究

可编程逻辑

描述

与仅仅几年前相比,当今的嵌入式产品已经变得更加复杂和更加先进。设计本身可包括一个FPGA以及一个单独的图形处理器(GPU),外加多个用于视频端接、USB、无线网络、以及高速有线以太网、工业Modbus或现场总线的连接端口。每个处理器以及相应的子系统都需要唯一的与其他时钟无关联的频率和类型,因此,它们需要自己的时钟信号。设计一个能产生这些彼此不同、具有所需精度性能的时钟系统,并将其分配到各自的负荷,是产品设计工程师所面临所有问题中的新挑战。

要提供这些时钟,一种直接和显而易见的方式似乎很简单,即可以根据需要采用多个时钟发生器IC,并将其放置在PC板上各个目标负载附近,或者采用一个由主时钟驱动的时钟树架构,如图1所示。这种做法至少从理论上可以解决多时钟的问题,因为每一个负载装置的需求可以通过量身定做的时钟信号来满足。而且,由于每个时钟源都靠近其负载,时钟之间以及时钟与信号之间的串扰都得到降低,从而最大限度地减轻了附加的时钟抖动和畸变问题。

图1:使用单一主时钟以及具有本地时钟发生器的时钟树是一种提供所需多个本地时钟的方式,但这种方式会影响成本(BOM,价格,占位面积)和性能,必须仔细研究。

为每个目标负载配备一个时钟IC的解决方案看似颇有吸引力,但也有许多不利因素,例如:

1.采用多个单独的时钟发生器IC直接导致BOM(物料清单)成本升高,以及管理和采购这些不同IC所产生的物流问题。

2.需要较大的PC电路板空间,而该问题几乎在每一个设计都很受限。

3.如果使用单独的、单路输出时钟发生器,而不是采用一个分布式时钟树,每一个时钟都需要自己的晶振,这将增大成本和电路板空间。

4.使用“时钟树”来产生最终的多个时钟会增加成本、占用空间、时钟抖动和误差积累。

5.采用多个IC会提高整体功耗。

6.若使用多个时钟发生器IC,每个新的设计都具有不同的电路板布局和时钟组件,使得难以在公司产品线不同产品之间重用系统设计。

在特定情况下每一个因素多么重要取决于具体设计、其优先事项、以及各种权衡。在多处理器系统中,针对每一个所需的独特时钟,如果决定采用一个时钟发生器加上一个晶振的方案会产生许多意想不到的后果。

替代方案的优势

幸运的是,还有另外一种方法可以在很大程度上克服多处理器设计中使用多个单独时钟发生器IC的弊端。一个多输出、可编程时钟发生器可以经由一个单一晶振来提供多路独立的输出,因而可以替代两个、四个、或更多个时钟。这些IC可具有多种输出选项、配置、以及频率范围,也可以面向多种应用。

在选择一个多路输出时钟发生器时,关键一点是要使其性能与各种时钟负载的需求相匹配。在许多设计中,各种不同的负载不仅具有不同的频率,当然也具有不同的电压、格式、上升/下降时间最大值、以及抖动指标。高端FPGA或SoC器件与用在同一设计中的低速通信链路相比,,其时钟将具有更严格的要求,但设计者却希望选择单一时钟发生器IC来满足所有不同的需求。

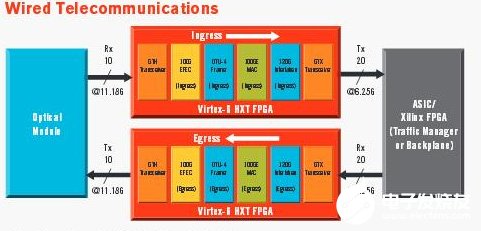

最新一代的可编程时钟发生器能够实现这些目标,尤其是可以满足一些较为困难的要求。例如,Xilinx公司的 Virtex-6和Virtex-7FPGA分别具有480 Mbps至6.6 Gbps,2.488 Gbps至11.18 Gbps数据速率的收发器,每个通道原始数据速率高达5.0 Gbps的PCI Express Base,以及一个支持10/100/1000 Mbps链路的以太网MAC模块,如图2所示。

图2: Xilinx公司提供的Virtex 6等FPGA具有高功能密度和极高带宽数据链路,具有成帧(framing)、增强型前向纠错(EFEC)的100GE MAC光学接口,以及采用两个Virtex-6 HX565T FPGA通过Interlaken总线实现的ASIC(或背板)接口。

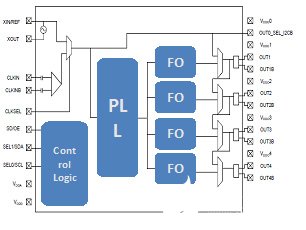

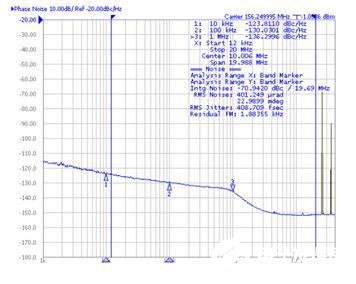

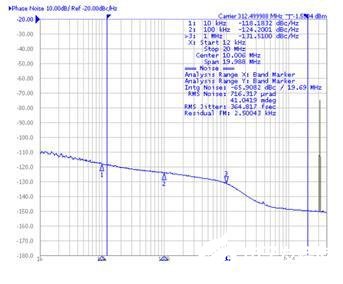

为了满足设计师基于这些FPGA实现电路设计的需求,IDT公司推出了VersaClock6系列可编程时钟发生器,如图3所示。VersaClock6时钟发生器可提供2至8路可配置输出(可选择为LVDS或LVPECL)以及2个、3个、或4个一次性可编程(OTP)配置,取决于选择的具体器件。所有时钟发生器包括一个分数输出分频器架构以获得最高的灵活性,并能产生1至350MHz之间的任何频率。该系列产品的最显着特点是能够确保均方根(RMS)相位抖动指标大大低于500 fs(0.5ps),如图4所示。

图3:IDT公司的VersaClock 6系列时钟发生器具有2个至8个可配置LVDS或LVPECL输出,每个都可实现1 到350 MHz之间的用户可编程频率。

图4:采用156.25和312.5MHz参考时钟,测量得到的相位抖动分别略微高过400fs(0.4ps)和350 fs(0.35ps)均方根值,如这些位噪声曲线所示,超过了最新FPGA的要求。

以应用实例说明其优势

那些必须支持SMPTE 424标准的设计可以作为很好的例证来说明使用一个可编程多输出器件的好处。SMPTE 424标准又称为3G-SDI,它针对高性能3 GbpsSerDes(串行/解串器)功能具有非常严格的眼图抖动规范,以满足所期望的误码率(BER)目标。 [SMPTE为电影与电视工程师学会,是国际公认的标准化机构,其管理的规范包括数字电视传输高速串行物理接口,通常被称为SDI或串行数据接口]。主要的强制性要求包括:

·时序抖动2.0 UI最大值,峰值到峰值,频率范围从10Hz到100kHz

·校准抖动规范(Alignment jitter)0.3 UI最大值,峰值到峰值,频率范围从100 kHz至297 MHz,推荐0.2 UI(一个单位间隔(UI)是两个相邻信号转变的时间间隔,为时钟频率的倒数)。

在技术方面更加具有挑战的是,许多广播视频设计需要同时支持NTSC和PAL HDTV标准,这意味着它们需要同时具有148.5MHz和148.5 /(1.001)MHz的参考时钟。此外,广播视频产品需要支持IP视频(VoIP)的趋势意味着这些设计也可能需要支持10GEPHY(10千兆以太网物理层),所以,通常需要工作在156.25 MHz的一个附加参考时钟。

由于Xilinx 7 系列FPGA具有集成式、高性能GTX / GTH / GTP收发器,因而通常被选用于这些支持SMPTE标准的设计。为了满足SMPTE 424眼图抖动规范,赛灵思(Xilinx)公司针对用于驱动这些SerDes功能的参考时钟规定了非常严格dBc/Hz相位噪声要求。如果相同的Xilinx 7系列GTX /GTH/GTP收发器也用于实现10 GbpsSerDes,非常严格的dBc/Hz的相位噪声要求同样也很关键。这些非整数相关(non-integer-related)时钟频率(148.5 MHz、 148.351648MHz以及156.25MHz)在与每个时钟非常严格的相位噪声要求结合时,意味着提供一个集成式时钟解决方案是一项重大任务。

幸运的是,已经有一种单一器件能够以单个器件综合所有这些高性能时钟:即IDT公司的通用频率转换器(UFT)系列高端锁相环(PLL)。该系列产品可作为一种高性能合成器,只需要一个简单的、基本模式并行谐振晶体(parallel-resonant crystal)作为其输入参考。UFT系列的所有产品都支持每个PLL的一个或两个不同引脚可选配置,并且这些可被预加载到内部一次可编程(OTP)非易失性存储器,用于在加电后直接自动运行,或者使用一个I2C串行接口来设置所需的频率转换配置。

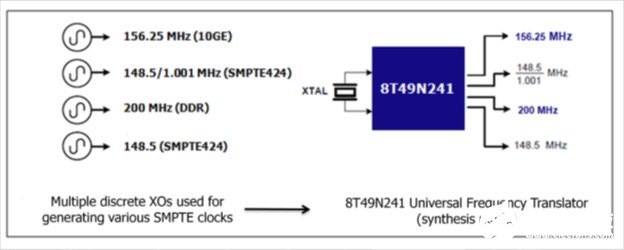

对于SMPTE 424设计,IDT公司的8T49N241可以作为一个高性能、四路输出合成器,如图5所示,其中可以清楚地看到电路板空间的节省以及设计复杂性。该系列的时钟器件具有这种复杂应用中Xilinx 7 系列参考时钟所要求的性能。

图5:一个单一的IDT通用频率转换锁相环(这里是8T49N241)可以用作一个高性能4路输出合成器,能够提供SMPTE需要的低抖动和高精度频率,可取代4个晶振和4个发生器IC。

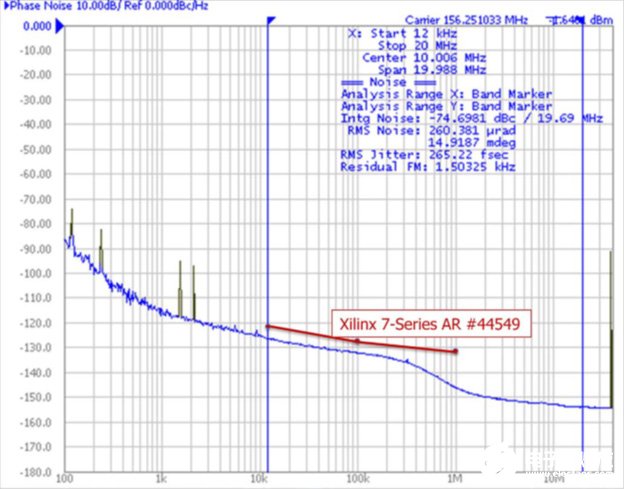

图6示出了一个典型的由IDT UFT时钟器件产生的156.25MHz输出时钟相位噪声曲线。相位噪声曲线远低于Xilinx Action Note AR# 44549所确定的相位噪声水平。

图6:IDT公司 UFT时钟IC生成的156.25 MHz输出时钟典型相位噪声曲线超过了Xilinx Action Note所确定的噪声要求。

如果设计者选择使用具有多路输出的一个单一时钟发生器IC,许多由于采用单独时钟IC而产生的问题就会消失或变得更简单。此外,通过为时钟IC添加可编程性,同样的组件和电路板布局可以重用于多个产品或升级产品。

设计人员在使用单一的时钟IC时,有一点需要牢记。IC的物理位置以及电路板上各个输出到相应负载的布线,都必须通过建模和仿真。这些对于保持时钟信号的完整性,并使串扰和噪声,以及对于抖动的影响达到足够低的水平非常必要。幸运的是,现在已有的用于高速信号和PCB布局的仿真工具能够完成这些任务,也将有助于确保针对非时钟信号的整体设计性能。

工具,易用性等设计考虑

显然,如果一个用户可编程、完全可配置的时钟发生器IC不能很容易地进行编程或配置,这对于用户将是一件非常令人沮丧的事情。 IDT公司的Timing Commander软件平台可以让客户通过一个直观而灵活的图形用户界面(GUI)对器件进行配置和编程。

图7所示为该平台的图形用户界面屏幕截图,其中该GUI把8T49N241配置为SMPTE 424应用的高性能四路输出合成器,分数反馈PLL与整数及分数输出分频器混合的组合允许8T49N241生成所有的这些输出频率,它们具有0 ppb的(每十亿份)附加合成误差,并且测得的10GE和SMPTE 424时钟相位噪声性能满足Xilinx 7系列的要求。

图7:为了配置SMPTE设计,IDT Timing Commander GUI采用分数反馈PLL与整数及分数输出分频器混合的组合来产生所有需要的输出频率。

另外,系统内I2C编程模式可以被用来在上电时为多输出器件编程,以覆盖一次可编程存储器的配置,因而,如果需要可重新配置器件。最后,用户可以另外针对每个输出对的一个独立扩频功能进行编程,以降低系统级的EMI/RFI水平和其他有关的顾虑,同样,这些也取决于选取的器件。

用户可编程在许多方面对于多处理器系统设计人员帮助很大,同时也克服了采用多个单独、彼此独立的时钟发生器所导致的缺陷,并且不会影响性能。用户可编程的特性能够凭借单一器件支持不同类型和负载需求,因此,“哪个时钟针对哪个负载类型?”等相关问题迎刃而解。当然,这些器件不仅可以进行频率定制,而且也支持其他一些关键的规范,能够实现成本、性能和高能效设计的理想平衡,而以往的方案往往要面临顾此失彼的尴尬。

责任编辑:gt

-

LMH1983高度集成的可编程音频/视频(AV)时钟发生器数据表2024-08-21 314

-

具有14个可编程输出的LMK03806超低抖动时钟发生器数据表2024-08-20 371

-

CY25200可编程时钟发生器英文手册2023-02-14 472

-

可编程音频时钟发生器MAX9485相关资料分享2021-04-02 1704

-

AK8140A可编程多时钟发生器评估板简介2020-07-27 2280

-

用于评估AD9525 3.6 GHz时钟发生器的评估板AD9525/PCBZ2019-02-25 2806

-

IDT推出其低功率可编程时钟发生器2017-09-28 9002

-

IDT5L35023VersaClock 3S可编时钟发生器解决方案2017-09-20 916

-

基于lmk03806的高性能可编程时钟发生器的设计与fpga实现 毕...2013-05-03 3360

-

DS1086 EconOscillator 可编程时钟发生器2012-03-22 2781

-

首款可编程时钟发生器的便携音频子系统发布2011-08-10 1238

-

利用MAX9489/MAX9471多输出时钟发生器构建集成时2009-04-22 538

-

MAX9489/MAX9471多输出时钟发生器构建集成时钟源2008-10-04 1173

全部0条评论

快来发表一下你的评论吧 !