首款基于机器学习引擎的新版数字全流程吞吐量最高提升了3倍

电子说

描述

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日发布已经过数百次先进工艺节点成功流片验证的新版 Cadence 数字全流程,进一步优化功耗,性能和面积,广泛应用于汽车,移动,网络,高性能计算和人工智能(AI)等各个领域。流程采用了支持机器学习(ML)功能的统一布局布线和物理优化引擎等多项业界首创技术,吞吐量最高提升 3 倍,PPA 最高提升 20%,助力实现卓越设计。

经过多项关键技术,全新 Cadence 数字全流程实现了 PPA 和吞吐量的进一步提升:

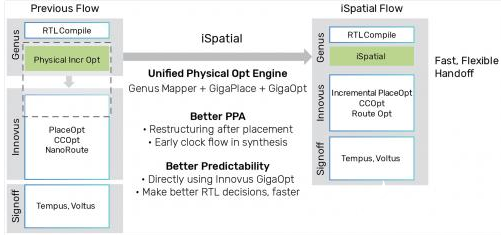

Cadence 数字全流程 iSpatial 技术:iSpatial 技术将 Innovus™ 设计实现系统的 GigaPlace™ 布线引擎和 GigaOpt™ 优化器集成到 Genus™ 综合解决方案,支持布线层分配,有效时钟偏移和通孔支柱等特性。iSpatial 技术让用户可以使用统一的用户界面和数据库完成从 Genus 物理综合到 Innovus 设计实现的无缝衔接。

机器学习(ML)功能:ML 功能可以让用户用现有设计训练 iSpatial 优化技术,实现传统布局布线流程设计裕度的最小化。

优化签核收敛:数字全流程采用统一的设计实现,时序签核及电压降签核引擎,通过所有物理,时序和可靠性目标设计的同时收敛来增强签核性能,帮助客户降低设计裕度,减少迭代。

“基于已经广泛采纳的集成流程,全新的增强版数字全流程进一步强化了 Cadence 在数字与签核设计领域的领导力,助力客户实现 SoC 卓越设计,”Cadence 公司资深副总裁兼数字与签核事业部总经理 Chin-Chi Teng 博士表示。“我们与客户紧密合作,缓解大规模设计下日益紧张的时间压力,提供高效达成 PPA 目标的全部所需。”

Cadence 数字全流程包括 Innovus 设计实现系统,Genus 综合解决方案,Tempus 时序签核解决方案和 Voltus IC 电源完整性解决方案。流程为客户提供实现设计收敛的快速路径和更好的可预测性,支持公司的智能系统设计™ 战略,助力实现高级节点片上系统(SoC)的卓越设计。

-

如何显著提高ATE电源吞吐量?2023-11-08 1530

-

全志R128 BLE最高吞吐量测试正确配置测试方法2023-10-27 2615

-

全志R128 BLE最高吞吐量测试正确配置测试2023-10-16 1132

-

iperf吞吐量的测试流程2023-04-03 623

-

debug 吞吐量的办法2022-08-23 1809

-

提高BLE吞吐量的可行办法2021-01-18 2251

-

如何通过UBFS获得流式ADC数据的最高吞吐量?2019-10-11 2204

-

MIMO天线增益不同引起的吞吐量波动2019-06-16 3541

-

CTAccel人脸检测演示,在单个服务器上将吞吐量提高2-3倍2018-11-29 3103

-

NI_LabVIEW三大关键技术提升测试速度与吞吐量2016-03-22 944

-

网卡吞吐量测试解决方案2013-12-23 4768

-

防火墙术语-吞吐量2010-02-24 1684

全部0条评论

快来发表一下你的评论吧 !