集成电路规模不断扩大 影响芯片成品率的因素有很多

电子说

描述

近年来,电子信息产业迅猛发展,为了追求电子产品的高性能及便捷性,集成电路规模不断扩大,特征线宽不断缩小,当前国际上的工艺已经进展 10 纳米以下,7 纳米已经量产,5 纳米也已经试产,将于 2020 年正式量产。

成品率下滑已成为纳米集成电路面临的最大挑战之一。而且,随着集成电路产品的快速升级,特别是对人工智能、5G 移动通讯、物联网、汽车电子方向应用需求的高性能、低功耗、高密度、可靠性及高度功能集成需求,促使各种新材料、新工艺、新器件的引进,为集成电路产品的设计制造带来了前所未有的挑战。这些因素大大增加了集成电路制造过程中的不确定性,使得集成电路产品的成品率更加难以控制。由于成品率问题的重要性,在当前的集成电路研发中,对成品率问题的考虑已渗透到集成电路设计、晶圆制造的各个阶段。如何在研发高性能集成电路的同时,保证较高的成品率,一直是学术界及工业界关注的热点问题。

首先,集成电路生产工艺十分复杂,一个芯片的产生往往要经过上百道甚至上千道工艺步骤,生产周期较长,在整个制造过程中任何一个工艺步骤上的偏差,都将会对产品成品率造成影响。尤其在 20 纳米节点以后,采用多次曝光的浸入式光刻,大幅度增加了光刻和刻蚀的次数,对芯片成品率的影响剧增。目前采用非 EUV 光刻制作的 10 纳米和 7 纳米的工艺,刻蚀步数已经超过 100 次,一个偏差,成品率将有可能下降到 10%。

其次,集成电路生产线的投资巨大,先进生产线的造价更是惊人。现在 14 纳米采用非 EUV 光刻,每万片产能的投资高达 25 亿美元。如果芯片成品率过低,难以付诸批量生产,投资成本将打水漂。

据晶圆代工厂的工程师表示,影响芯片成品率的因素有很多,但主要来自两个大的方面:

第一是来自设计方面的影响,包括芯片设计参数和结构设计不合理,与相应的制造工艺特性不吻合,则会导致芯片性能上出现缺失,造成成品率过低。

第二是制造工艺缺陷或扰动对成品率的影响,包括金属条变形、粉尘颗粒与冗余物的出现,或是工艺控制无法保证工艺窗口,都会对芯片成品率造成不可估量的影响。

对于如何提升芯片成品率,晶圆代工厂的工程师表示,提升芯片成品率的关键,是根据工艺及设计的具体情况,利用 EDA 工具通过对缺陷的统计分布情况进行分析和优化。而且根据工艺节点的不断更迭,越先进的工艺其成品率越难以控制,成品率的重要性也越明显。

成品率提升(Integrated yield ramp)EDA 软件虽然是一个小众市场,但是却非常关键。随着芯片研发及制造企业的竞争日趋激烈,成品率问题作为影响企业经济效益的关键因素,已成为芯片设计及晶圆制造企业提高产品市场竞争力的重要砝码。

事实上,进入 2000 年后,国内在成品率提升软件方面开展了相当多的研究,如西安电子科技大学在缺陷导致的集成电路功能成品率问题方面的研究、浙江大学在利用光学校正技术(OPC)改善集成电路成品率的研究等都取得较好的成果。但始终没有市场化。

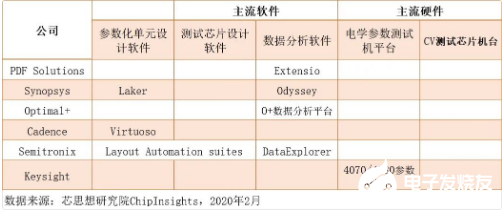

芯思想研究院在调研中发现,业界大厂除台积电、英特尔各拥有一支强大的成品率团队可以自主进行先进成品率管理以外,其他的晶圆制造厂的成品率提升和管理都需要较多借助外力。目前主流国际市场上,集成电路产业界较普遍采用的和成品率提升相关的关键软件、硬件提供商有 PDF Solutions、Semitronix、Synopsys、Cadence、Optimal+、Keysight 等。

以下是国际主流晶圆制造厂使用的一些主流软硬件。

Synopsys、Cadence 是全球知名的 EDA 工具提供商,其参数化单元设计软件广泛应用于集成电路设计领域,这其中也包括成品率提升方面。Keysight 是德科技是全球领先的测量仪器公司,为电子设计、电动汽车、网络监控、物联网、智能互联汽车等提供测试解决方案。在这里就不多做介绍。

下面我们简单介绍下 PDF Solutions 和 Optimal+。

PDF Solutions

PDF Solutions, Inc. 成立于 1991 年,总部在美国硅谷,是一家具有 30 年行业经验的半导体产业跨界整合技术服务公司,致力于为 IC 设计公司验证及改善设计,顺利完成流片、生产到产品上市;以及为晶圆代工厂定位工艺问题,提升新技术开发能力,完善工艺流程控制。PDF Solutions 的技术服务包括集成电路前沿工艺的开发,包括基于客户定制测试芯片(Characterization Vehicle)的良率改良咨询,可制造性设计优化(Design for Manufacturability),以及半导体大数据平台 Exensio Platform 等工具。其中 Exensio 平台包含用于半导体设备生产的故障检测与分类(Fault Detection and Classification, Exensio-Control)模块,产品测试优化模块(Exensio-Test),半导体良率管理系统模块(Exensio-Yield)等等。

PDF Solutions 提供从技术研发到产品设计,从工艺制造到封装测试,从试验流片到成熟量产,的整套成熟技术服务,有效帮助厂商降低 IC 设计和制造成本,显著提高产品质量和生产效率,进而加快产品上市速度和提升利润空间。

Optimal+

Optimal+是以色列一家大数据分析服务商,成立于 2005 年,为半导体和电子产业提供可操作性的制造和测试数据分析,其成品率业务仅涵盖数据分析这一块内容。但是其营收主要来自于电子行业,半导体产业为其贡献的营收仅约占其总营收入 20%,且占比呈现逐年下滑状态。公司未来在半导体产业的机会不大,原因在于公司仅仅只提供软件,没有硬件支持。

芯思想研究院在调研中还发现,杭州广立微电子有限公司(Semitronix)是国内一家以集成电路成品率为主营业务的企业,已经开发成功成品率提升相关软硬件工具。

随着近年来中国半导体行业发展环境的持续利好以及国内半导体企业的成长,大家对于技术、质量、效率的要求越来越高,很多国内领先的集成电路设计公司和晶圆生产厂商已经和国际接轨。

成品率提升软件市场规模

据中芯国际、华虹集团、三星电子的工程师表示,从 2017 年就开始采用广立微提供的新工艺制程研发提供整合性服务,包括早期工艺开发、产品设计流程确立、中后期产品量产时的可寻址测试结构,直到 yield ramp 阶段基于产品版图的测试芯片。

韩国顶级半导体公司代工部门的技术人员表示,广立微提供的基于测试芯片的软、硬件系统产品以及整体解决方案用于高效测试芯片自动设计、高速电学测试和智能数据分析的全流程平台,利用特有的流程平台与技术方法可以提高集成电路性能、良率、稳定性和产品上市速度的定制服务。公司代工部门的技术人员表示,基于广立微的软硬件的实用性和成本效益,向公司存储业务部门进行了推荐,现在公司存储业务也已经开始采购广立微的产品。该公司代工部门的技术人员还表示,由于之前欧美国家成品率方案供应商的市场垄断性,业界一直不太欢迎其商业模式。这一说法得到台积电、联电、中芯国际等多家晶圆代工厂的认可。

根据 WSTS 的数据,2019 年全球半导体芯片产业的营收超过 4000 亿美元。而根据三大 EDA 厂商的营收数据,预估 2019 年全球 EDA 市场约为 96 亿美元。

芯思想研究院根据调研数据发现,全球各大晶圆制造厂每家每年在成品率提升软件方面的投入约在 50 万美元。而晶圆代工公司的投入规模要大一些,一般在 200-300 万美元,高的在 700 万美元。

根据不完全统计,全球成品率提升 EDA 软件规模整体在 8000 万美元到 9000 万美元之间。按照地域来看,2019 年美洲约 1800 万美元至 2000 万美元、欧洲约 400 万美元至 500 万美元、亚洲(不含中国)约 2500 万元至 3000 万美元、中国(包括台湾)约 3300 万美元至 3500 美元。

预估未来几年的全球市场成长有限,预计到 2025 年市场规模望达 1.0-1.1 亿美元。但得益于国内晶圆制造业的成长,加上未来国内兴建的多座 FAB,国内的市场是有增无减,预计 2025 年中国(包括台湾)的市场将接近 6000 万美元,这将为国产成品率提升软件拓展国内的市场提供机会。

注:这是芯思想研究院第二次针对 EDA 软件细分市场进行调研,第一次是 2019 年推出的制造专用软件调研,由于经验不足,数据仅供参考!

-

伟测集成电路芯片晶圆级及成品测试基地项目启动竣工验收2024-05-28 1121

-

集成电路芯片规模组成详细介绍2022-04-06 9939

-

芯片的作用是什么 集成电路的分类2021-09-20 19798

-

芯片有哪些设计流程2021-07-22 1051

-

AGV在光伏行业应用规模正在不断扩大2020-12-09 2874

-

模拟芯片的需求随着电子产品的发展而不断扩大2019-12-17 1125

-

集成电路电源芯片的分类及发展2018-10-18 4782

-

中国机器人产业发展迅猛,产业规模不断扩大2018-08-30 3716

-

描述集成电路工艺技术水平的五个技术指标2018-08-24 7451

-

故障芯片重利用的三维存储器成品率提高方法2017-01-07 685

-

中国集成电路产业持续扩大2016-03-03 1041

-

芯片商们,苹果智能手表iWatch需要解决成品率低难题2013-09-12 5300

-

异构多处理器系统芯片的设计与研究2009-11-27 340

-

面向高成品率设计的EDA技术2008-06-11 6296

全部0条评论

快来发表一下你的评论吧 !