基于UNI/O总线系统的应用设计方案及发展前景

接口/总线/驱动

描述

引言

随着嵌入式系统小型化的趋势,市场对减少器件间通信所用的I/O引脚数的需求与日俱增。Microchip科技公司开发的UNI/O总线正满足了这一需求,这个低成本且易于实现的解决方案,仅需要使用一个I/O引脚就可实现主从器件之间的通信。

1 UNI/O总线介绍

1.1 UNI/O总线的特点

UNI/O总线具有如下特点:

①UNI/O总线采用曼彻斯特编码,只需一根信号线SCIO就可以实现数据的串行传输和同步控制。

②UNI/O总线是一种单主型总线。主器件负责肩动和控制总线上的所有操作,决定总线的工作速度。主器件通常由单片机、ASIC等充当。

③UNI/O总线具有双向通信能力。有主发送从接收和从发送主接收两种工作方式。

④UNI/O总线速度为10~100kbps。

⑤UNI/O从器件必须具有空闲模式和待机模式,也可选择具有保持模式。

1.2 UNI/O总线的帧格式

1.2.1 位值定义

由于采用的是曼彻斯特编码,所以其位值由佗周期中间的信号跳变方向决定。UNI/O总线规定:从高到低的跳变是0,从低到高的跳变是1。

1.2.2 帧结构

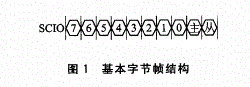

在UNI/O总线上进行通信时,指令、数据和地址的传送都以字节为单位。字节传送时,高位在前,低位在后,前一个位之后立即传输下一个位,位与位之间没有延迟。字节之后必须发送应答序列,进行主从应答。图1给出了通常情况下使用的基本字节帧结构。

(1)主应答位

由主器件发送,取值为1或0。为1时称之为MAK,MAK告知从器件指令执行将继续;为0时称之为NoMAK,NoMAK用来结束当前指令,此后如有必要,从器件可以启动相应的内部处理。

(2)从应答位

由被选定作为通信对象的从器件发送。该位为1时称之为SAK,SAK表明其前面的操作已成功完成;非1时称之为NoSAK。在从器件被选定之前,由于无从器件应答,从应答位应为NoSAK。在从器件被选定之后,NoSAK用来表明通信产生了错误。

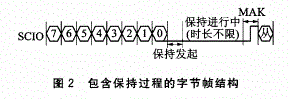

另外,UNI/O总线也考虑了对主器件的中断功能的支持。当主器件与具有保持模式的从器件进行通信时,如果主器件在下一个MAK位周期时间内持续拉低SCIO,从器件就进入了保持模式。要维持在保持模式应继续使SCIO为低电平。当从器件处在保持模式时,主器件就可以进行对其他I/O设备的中断处理工作,中断处理结束后可通过发送MAK来终止保持过程,并继续之前的通信。图2给出了包含保持过程的字节帧结构。

1.3 UNI/O总线的命令序列

UNI/O总线的命令序列是指完成一条指令的执行主从器件,需要在总线上传送的各种信号和字节帧的有序组合。在UNI/O总线系统中,一条指令的执行过程必须包括:总线准备、主从同步、从器件选择、指令传输和指令执行等环节。

1.3.1 总线定义的信号

(1)待机脉冲

待机脉冲是由主器件驱动SCIO到高电平状态,并保持此状态600μs以上形成的脉冲信号。待机脉冲通常用来通知总线上的所有从器件进入待机模式,也可以用来提前终止一条指令的执行。在执行一条指令时,如果是第一条指令,或者要选择的从器件与上一条指令不同,或者上一条指令的执行过程发生了错误,本条指令的执行都必须从产生待机脉冲开始。

(2)TSS信号

TSS信号是由主器件驱动SCIO到高电平状态,并保持此状态10μs以上形成的脉冲信号。在一条指令成功执行之后,若还要执行下一条指令来对同一个从器件进行操作,则后一条指令执行过程的第一步只需产生一个TSS信号,而不需要再产生待机脉冲。这样,通信效率会更高。

1.3.2 特殊功能字节帧

(1)起始头

起始头用来使从器件进入正常工作模式,并同步从器件内的时钟。起始头由5μs以上的持续低电平脉冲和紧跟其后的8位编码“01010 101”组成。所有的从器件都可以从起始头中获知位周期的长短,并以此为依据调整内部时钟,实现主从同步。起始头之后的主应答位应为MAK,从应答位正常情况应为NoSAK。

(2)地址帧

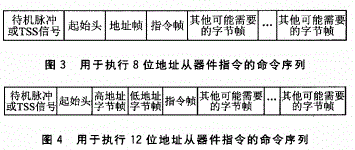

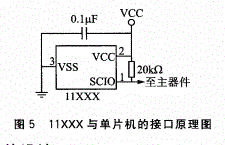

地址帧用于选择总线上特定的从器件进行通信。从器件地址有8位和12位两种类型,由4位系列码和4位或8位从器件码组成。8位地址的传输只需一个地址帧,正常情况,其应答序列由MAK和SAK组成。12位地址的传输需要两个字节帧:高地址字节帧和紧跟其后的低地址字节帧。正常情况,低地址字节帧中的应答序列应该由MAK和SAK组成,高地址字节帧中的应答序列则由MAK和NoSAK组成。

(3)指令帧

指令帧用于传送指令,由指令编码和应答序列组成。指令及其编码往各种UNI/O从器件中定义。指令帧中的主应答位应根据指令是否要求传输其他数据字节确定。当指令要求传输其他数据字节时,该位为MAK,否则为NoMAK。从应答位正常情况下为SAK。

1.3.3 UNI/O总线的命令序列

图3所示的是用于执行8位地址从器件指令的命令序列。其中字节帧的数量在总线规范中未进行限制,只要前一个字节帧中的主应答位为MAK就表示期望传输下一个字节帧。不过,字节帧的实际数量必须符合从器件指令的使用规范。在此前提下,可以由用户程序根据其功能决定。用于执行12位地址从器件指令的命令序列如图4所示。

2 UNI/O从器件与单片机的接口设计

11XXX系列EEPROM是Microchip技术公司最新推出的、支持UNI/O总线协议的存储器产品。下面就以该存储器的使用为例,详细介绍UNI/O总线系统的应用设计方法。

2.1 硬件设计

图5给出了11XXX系列EEPROM与单片机的接口原理图。图中,SCIO引脚上接一个20 kΩ的上拉电阻是为了确保总线在上电/掉电序列期间以及未被驱动时处于空闲状态。VCC和VSS之间接入一个0.1μF的去耦电容是为了滤除VCC上的噪声。

2.2 软件设计

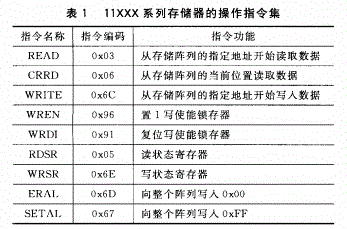

2.2.1 UNI/O存储器11XXX的操作指令

11XXX系列存储器共有9条操作指令,其指令编码和功能描述如表1所列。

2.2.2 UNI/O存储器11XXX的高级特性

11XXX器件除了具有EEPROM存储器的基本特性、支持UNI/O总线协议外,还有以下高级特性。这些高级特性也是编写接口程序的基本依据。

(1)内置了一个状态寄存器

状态寄存器可以用来提供状态信息和片内数据的保护控制。其各位的功能定义如下:

①Bit0。为写进行位WIP,用于表明11XXX是否忙于写操作。当它为1时,表明正在进行写操作;为0时,表明没有进行写操作。此位只读。要编写高效率的写存储阵列程序,可采用WIP查询来及时检测写周期的结束。

②Bit1。为写使能锁存器位WEL,用于表明写使能锁存器的状态。当它为1时,锁存器允许存储阵列无保护块和状态寄存器的写入操作;当置为0时,禁止写入操作。只能使用WREN指令来将此位置1,但会在上电或成功执行了以下指令之一时复位。这些指令包括:WRDI、WRSR、WRITE、SETAL和ERAL。

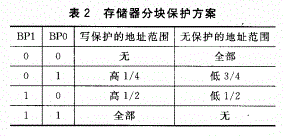

③Bit2~Bit3。是块保护位BP0和BP1,用于表明当前哪些块被写保护。这些位可以由用户通过WRSR指令进行设置。这些位是非易失性的。表2给出了利用BP0和BP1对存储器进行分块保护的方案。

④Bit4~Bit7。为无关位,读出时为0。

(2)包含一个读操作地址指针

在进行存储阵列读操作时,渎操作地址指针会在每个字节发送后自动指向原地址加1的存储单元。当到达最高地址时,如果主器件仍然发出MAK选择继续读取,则地址指针的值会翻转回到0x00地址处。在上电后,读地址指针会保持上一次访问的存储单元的地址。

(3)支持页写功能

用WRITE指令可以向指定地址的存储单元或者指定地址开始的存储器区域写入内容任意的数据。不过,在写多个存储单元时,必须限制在单个物理页面内写。物理页边界从页大小(16字节)整数倍的地址开始,结束于页大小的整数倍减1的地址。如果WRITE指令试图跨越物理页边界进行,其结果是将超出页边界的数据写回到当前页的开始,即覆盖先前存储的数据,而不会如期望的那样写到下一贞。

2.2.3 UNI/O存储器11XXX的读写程序

上电之后,由于11XXX处在关断模式,而且总线处于高电平空闲状态,所以主器件必须先在SCIO上产生一个高到低再到高的脉冲,使11XXX从关断模式退出进入空闲模式,这样11XXX才能按照命令序列所规定的流程响应总线上的其他信号,接收主器件发来的指令,并按指令要求完成规定的操作。

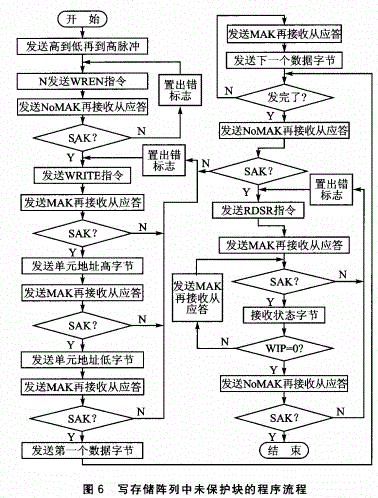

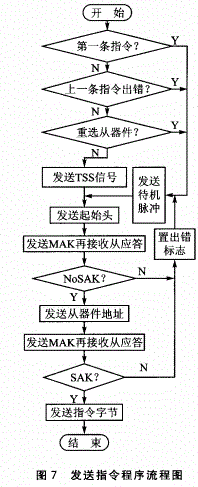

(1)写程序流程

图6是写存储阵列中未保护区块的程序流程。图中发送指令的操作可通过调用发送指令子程序来完成。图7给出了发送指令程序流程。要写存储阵列中受保护的区块,只需在执行WREN指令之前,用WRSR指令对BP0、BP1进行相应的设置,以暂时解除待写区块的保护,并在程序的最后再用WRSR指令对它们进行恢复即可。要全地址空间置1或擦除,必须先解除对整个存储阵列的保护并使能写操作,再发送SETAL或ERAL指令,指令发送之后用NoMAK来启动内部写操作,内部操作完成之后恢复对存储阵列的保护即可。

(2)读程序流程

随机读存储阵列的程序流程是:先发送READ指令,再发送待读单元地址。先高地址字节,后低地址字节。然后,从器件就会将该地址中的数据送到总线上,主器件收到第一个数据字节后,若还要读取更多的数据,可以发送应答信号MAK。之后,从器件用SAK应答,并送出下一个数据字节。若要结束读操作,主器件只要发送NoMAK即可。

要从存储阵列的当前位置读取数据可用CRRD指令来进行操作,其程序流程除了不需要传送存储器单元地址外,其余操作步骤与READ相同。

结语

UNI/O总线只有一根信号线,对I/O端口的占用最少,可有效地减小嵌入式系统的体积并降低产品成本,具有广阔的应用前景。

责任编辑:gt

-

国产FPGA的发展前景是什么?2024-07-29 8070

-

嵌入式系统发展前景?2024-02-22 11182

-

UNI/O总线规范2021-05-20 848

-

车载设备GPS的发展前景如何?2021-05-13 1740

-

总线分析仪市场发展前景及投资可行性分析报告2021-04-20 1502

-

通过SCIO为UNI/O总线器件供电2021-03-31 1091

-

嵌入式的发展前景2021-01-13 3379

-

嵌入式人才发展前景2019-01-21 2957

-

无线电发展前景怎样2014-09-13 3748

-

ARM的发展前景怎么样2013-11-20 3655

-

STATCOM发展前景怎么样啊?2013-05-12 12720

-

labview的发展前景2012-11-18 11207

-

嵌入式发展前景2012-08-20 13387

-

网络电话的发展前景?2012-07-05 2891

全部0条评论

快来发表一下你的评论吧 !