如何采用霍尔效应电流传感器抑制共模干扰

EMC/EMI设计

描述

背景

在使用集成载流环的IC中,载流环可以产生IC能测量的磁场。该磁场通过霍尔效应转换成电压。此霍尔电压正比于电流大小和方向。图1是特定电流传感器IC引线框产生磁场的示例。在该图中,箭头指示通过引线框的电流,彩色图表示100A直流电通过传感器时产生的磁场。为了表达清晰,图中移除了电流源。

图1:ACS780电流传感器引线框磁场。

使用配备集成载流环的IC具有很多优势:无需磁芯、基本没有磁滞、功率低、并且具有较高的温度精确度。但是,由于不存在磁芯,传感器容易受到磁体或传感器IC周围导线电流产生的杂散磁场的影响。为了抑制杂散磁场的出现,Allegro的很多电流传感器都具有双霍尔共模抑制方案。霍尔板的布置方式要确保当电流通过IC集成导体或载流环时,每个霍尔板感应的场极性相反。在图1中,两个霍尔板的位置用H1和H2表示。可以从图中看出,这两个区域具有方向相反的磁场。

采用CMR技术的基本原理是:如果两个霍尔板的信号相减,然后可以将集成环引发的信号求和,这样就可以抑制来自进入IC的任何杂散磁场共模(单极)信号。简单举例,假定每个霍尔板的磁场±B大小相等,方向相反,则:

H1 – H2 ∝ B1 – B2

B – B2 = B – (–B)

B – (–B) = 2 × B

因此,

H1 – H2 ∝ 2 × B

假定两个霍尔板上具有相等的杂散磁场Bext,则:

H1 – H2 ∝ B1 – B2

B1 – B2 = (B + Bext ) – (–B + Bext)

(B + Bext ) – (–B + Bext ) = 2 × B + Bext – Bext

2 × B + Bext – Bext = 2 × B

因此,

H1 – H2 ∝ 2 × B

Allego的其它技术资料《无磁芯霍尔效应电流传感器IC采用的共模场抑制技术》更详细地介绍了CMR技术的理论和指导方程。本文介绍的主要技术是如何设计和布置这些电流传感器IC的载流线路。此外,本文也提供了最小化其他杂散来源的指南。

临近电流产生的磁场

为了充分利用这些器件的CMR功能,包含IC的电路板应设计为两个霍尔板的外部磁场相同。这有助于最大限度减少载流PCB自身产生的外部磁场导致的错误。每个载流轨迹的三个主要参数据决定了导致IC错误:与IC的距离、载流体的宽度以及它和IC之间的角度。图2是IC附近载流体布线的示例。器件和导体之间的距离d是器件中心与导体中心的距离,电流路径宽度为w,器件和电流路径之间的角度θ是指连接两个霍尔板的直线与电流路径垂直线的夹角。

图2:具有临近电流路径的ACS780(从传感器底部观察)。

两个霍尔板的位置和方向随IC的不同而有所变化。例如,如图3所示,ACS724的霍尔板相比ACS780霍尔板旋转了90°。如果在任何具有CMR功能的Allegro、电流传感器IC附近进行电流路径布线,最好保持θ尽可能接近90°。

图3:霍尔板对齐的ACS724电流传感器IC。

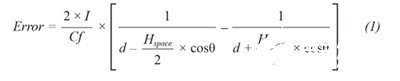

如果无法保持θ接近90°,下一个最好的选择是保持电流路径与电流传感器IC之间距离d尽可能大。假定电流路径与IC的夹角最差,即θ=0°或180°,见下列等式:

此处,H距离是两个霍尔板之间的距离,Cf是IC耦合因数。此耦合因数随IC不同而变化。ACS780的耦合因数是5至5.5G/A,而其他Allegro IC的耦合因数范围是10至15G/A。

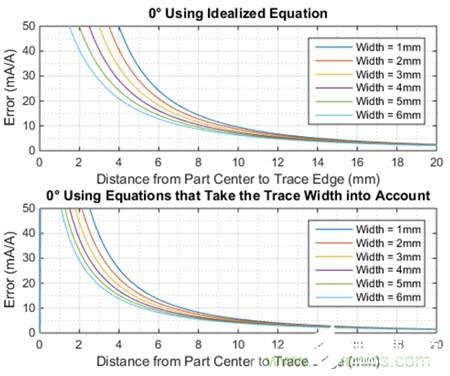

误差估计

等式1假定是无限长、无限细的导线。它没有考虑载流导体的宽度和厚度。图4是在最差条件方向(θ = 0° 或180°)计算得出的通过ACS780的载流体误差。该误差是采用理想等式以及考虑导体宽度和厚度的计算密集方程组计算得出。该图显示,计算误差高于使用理想方程的结果。因此,方程1可用于快速、保守估计误差。

图4:ACS780使用理想方程1与使用轨迹尺寸计算误差。

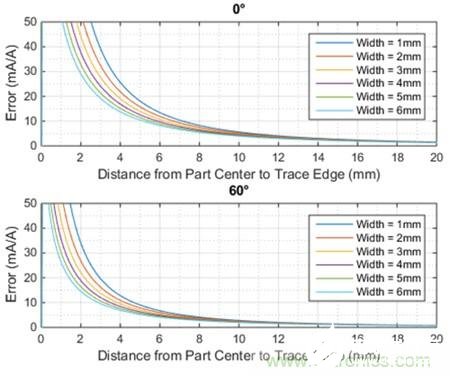

使用更精确的计算方法可以为不同宽度的电流路径以及器件和电流路径之间不同的角度计算误差。对于所有角度和宽度,都假定使用4盎司规格铜导体设定电流轨迹厚度。该图表明,载流体宽度对误差有影响,但最大的影响因素是与器件的角度θ以及与器件的距离d。

图5:ACS780计算4盎司规格铜导体轨迹导致的误差;多轨迹宽度θ=0°和60°

其他需要考虑的布局原则

如果布置包含具有CMR的Allegro电流传感器IC的电路板,所有载流路径的方向和接近性是重要因素,但优化IC性能还要考虑其他因素。可能影响系统误差的其他杂散场来源包括与IC集成载流体相连的轨迹以及临近永久磁体的位置。

必须小心规划电路板与电流传感器IC的连接方式。可能影响性能的常见错误是:

• 电流路径到IP管脚的接近角度

• 电流轨迹在IC下面扩展得过远

接近角度

使用Allegro电流传感器IC的一个常见错误是使用不适当的电流引入角度。图6是电流轨迹接近IC的示例(此处是ACS724)。此图显示IP+和IP–的轨迹。浅绿色区是进入IP+的理想接近区。该区域范围是0°至85°。该规则同样适用于IP–轨迹。

该区域的限制是为了防止载流轨迹影响到可能导致IC输出误差的任何杂散场。如果与IP相连的电流轨迹在该区域外部,则必须按上述方式处理(临近电流路径导致的磁场)。

图6:ACS724电流轨迹接近角度θ的理想范围是0°至85°,此范围很可能与其他Allegro电流传感器IC不同。

IC下的扩展

另一个常见错误是电流轨迹与IP管脚距离过远。根据器件的不同,这可能导致两种不同的问题。如果是采用SOIC和类似封装的器件,这可能导致IC上产生杂散场,使性能降低。如果采用LR封装,由于IP总线较大并且暴露在外,在封装下面过远布线可能改变通过IP总线的电流路径,从而改变器件的性能。下面内容将更详细地介绍对LR封装的影响。

对于杂散场而言,如果电流轨迹以一定的角度进入IP总线,问题会更加严重。如果发生这种情况,电流实际在部件下面流过,背向IP管脚,然后向上通过IP管脚。改变的电流路径可能会导致杂散场产生,降低IC精度。禁止在器件下面扩展至IP管脚的电流轨迹就可以防止这种情况。

图7:ACS724在IC下扩展,电流轨迹在IC下面过远,改变了电流路径,降低了精度。

永磁体影响

如果永久磁铁靠近电流传感器IC,磁铁导致的杂散场也会影响IC性能。一般情况下,来自磁铁的杂散场可能随磁体的不同而变化极大。它取决于磁铁尺寸、材料、磁化方向以及其他很多因素。如果可以调整电流传感器,使霍尔板垂直于磁体(如图8所示),则可以将这些杂散场的影响降至最小。

图8:具有临近永磁体最优方向的ACS780。

LR封装特定布局规则

IC下的扩展

在LR封装中,载流轨迹在器件下面扩展实际改变了电流通过IP总线的路径。这可能导致IP总线与IC的耦合因数发生变化,并显著降低器件性能。

使用ANSYS Maxwell电磁套件可以模拟电流密度和电流产生的磁场。图9提供两种不同模拟的结果。第一种情况是向上引至IP总线的电流轨迹在所需点终止。第二情况是电流轨迹向IP总线上方扩展过远。两个模拟中的红色箭头表示高电流密度的区域。在没有过量重叠的模拟中(红色区域),电流密度与具有过量重叠的模拟差距巨大。还可以看出,H1场比没有过多重叠时更大。这一点用蓝色暗影表示。

图9:具有不同电流轨迹和IP总线重叠的ACS780引线框模拟。

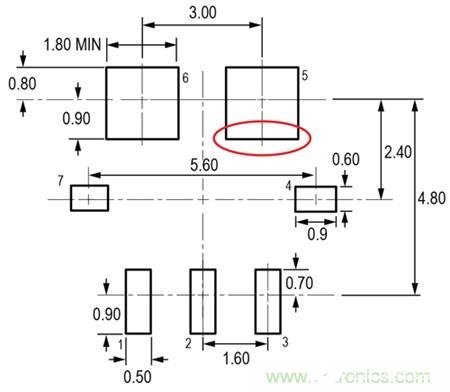

如果重叠超过推荐量,也会导致其他问题,例如电流接近角范围显著缩小。如果电流轨迹在IP总线上扩展的过大,则会形成对接近角的依赖,即接近角直接影响器件的耦合因数。避免这种情况的最佳方式是限制电流轨迹的重叠。

图10:ACS780 PCB布局参考图。进行必要的调整,满足应用工艺要求和PCB布局公差和红色的圈选关键尺寸。

结论

Allegro MicroSystems电流传感器IC有很多优势。这些传感器IC的磁滞几乎为零,而且功耗非常低。与无磁芯相伴的一个缺点是容易受到杂散磁场的影响。但是,很多IC都能够抑制共模磁场。

两个霍尔板的共模场相等时,CMR技术效果最好。我们探讨了若干显著降低两个霍尔板共模场差值的技术,即如何进行外部电流路径布线与其他优化布局技术。针对电流路径不能以最有利的方向布线的情况,我们还介绍了误差估算。此外,还探讨了一些针对LR封装的布局技术,这是因为必须考虑LR的一些特性才能获得最优性能。

总之,本文探讨的技术和计算有助于客户优化Allegro、电流传感器IC性能。

责任编辑;zl

-

德州仪器方案-使用封装内霍尔效应电流传感器的太阳能应用场景概要2025-08-04 7174

-

川土微电子推出全新高精度霍尔效应电流传感器2025-02-13 951

-

TMCS11073%精度、基本型隔离霍尔效应电流传感器数据表2024-08-09 653

-

中国霍尔效应电流传感器市场规模达到了192.71百万美元?2022-12-30 1462

-

线性霍尔效应电流传感器IC2022-12-26 12936

-

第一个零漂移霍尔效应电流传感器2022-08-08 2409

-

霍尔效应电流传感器集成电路封装的内部结构2021-04-28 6746

-

无芯霍尔效应电流传感器集成电路(IC)和共模场抑制2021-04-27 3942

-

霍尔电流传感器的应用2020-10-29 3398

-

电流传感器的开环和闭环2019-06-24 4700

-

基于开环霍尔效应电流传感器性能的改善2019-04-19 1884

-

数字输出开环霍尔效应电流传感器参数及应用介绍2018-08-27 5339

-

如何采用电流传感器IC实现共模场干扰最小化?2017-08-12 5262

全部0条评论

快来发表一下你的评论吧 !