基于CY7C68013芯片的LED显示屏外部接口设计

接口/总线/驱动

描述

1 、引言

led 显示屏具有亮度高, 故障低、能耗少、使用寿命长、显示内容多样、显示方式丰富等优点, 可广泛用于公路、金融、证券、车站、码头、体育场馆等公共场合, 其显示数据通常来自上位PC 机, 这就要求有一个高速通道来传输大量的显示数据,USB2. 0 接口无疑是一个很好的解决方案。USB 由总线提供电源, 传输时具有CRC 检错、纠错能力, 能实现真正的实时热插拔, 并支持多个外设连接到同一个连接器上, 从而缓解PC 系统资源冲突, 这些突出的优点使得USB1. x 在PC 机外部设备上得到了广泛的应用, USB2. 0 传输速度高达480Mb/ s ,是USB1. x 的40 倍, 并向下兼容USB1. x。这样就使得快速大量的数据传输得以实现。

2 、CY7C68013 简述

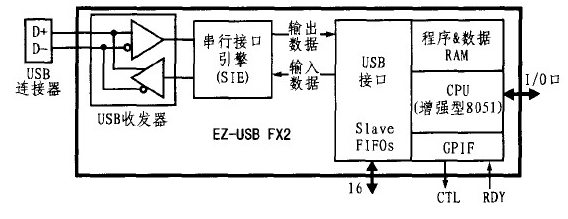

带高速Slave FIFO 通用外部接口的CY7C68013是CYPRESS 公司推出的USB2. 0 集成微处理芯片,片上集成了USB 收发器(SIE) 、增强型8051 单片机(其指令系统与普通8051 单片机完全兼容) 及8k 程序存储区, 共有4 个支持USB2. 0 高速传输的“大”端点(2 个IN 端点和2 个OUT端点) 和4kB 片内RAM,该RAM可配置为4 个“大”端点的FIFO ,其中2 个“大”端点可以配置为双、三、四缓冲区( FIFO) ,一个“大”端点最大可配置为2kB FIFO ,更重要的是,该芯片提供了两个用于实现USB2. 0 高速传输的可编程外部设备接口以及Slave FIFO 和GPIF , 这2 个通用外部接口可通过与4 个“大”端点协调工作来实现USB2. 0 的高速传输, 本文只讨论Slave FIFO 可编程外部设备接口的应用。

CY7C68013 有56pin、100pin、128pin 三种封装,其中56pin 已具备所有USB2. 0 功能, 而100pin 则在56pin 基础上增加了更多I/ O 和更多GPIF 模式下的控制信号, 128pin 又在100pin 基础上增加了用于扩充数据存储区的地址总线和数据总线。本应用就是基于可编程外部设备接口Slave FIFO , 大量数据传输可直接由FPGA 处理而无需扩充外部数据存储区,在此选择最经济的56pin CY7C68013 即可满足设计要求, 其体系结构如图1 所示。

图1 56 脚CY7C68013 的体系结构

3、硬件设计

图2 所示是FPGA 与CY7C68013 的连接图, 除将IFCLK作为FPGA 输入时钟外,其它信号均在FP2GA 和CY7C68013 之间互连。由于FPGA 片内RAM很小, 本系统还使用了一片128k ×8 的高速静态RAM(型号为IS63LV1024 , 读写周期为15ns) 作为数据暂存器。FPGA 与CY7C68013、RAM、VT6103 的硬件连接见图2。

图2 硬件连接总图

从USB 收到的来自上位PC 机数据最终将被远端安装在LED 显示屏屏体内的显示控制部件中, 当RAM被填入预定数量的显示数据时, FPGA 会从RAM中连续取出数据并送到与VT6103 连接的4 位数据输出端口, VT6103 收到4 位数据后, 其内部会自动按照IEEE802. 3 规范对该数据进行4B5B(转换4 位数据数据码为5 位数据码) 重新编码,然后将5B码送扰频器,再经片内整形后输出给以太网变压器,以驱动五类双绞线并将数据传给远端显示控制部件。

4、软件设计

本系统的外部主设备接口逻辑采用VHDL 硬件描述语言,利用ALTERA 公司QUARTUS II 开发平台进行设计。软件设计是以FPGA 为核心的,主要由下面3 个并行执行的部分组成, 在此每个部分分别设计为一个VHDL 进程(process) :

进程1 : 外部主设备FPGA 同步读写CY7C68013“大”端点FIFO 的时序逻辑, 并把接收到的数据存入FPGA FIFO 中。这部分只需要根据Slave FIFO 读写时序进行设计,Slave FIFO 时序图如图3 所示。

图3 Slave FIFO 同步读时序

这里需要引起注意的是两个建立时间: 其一是tOEon , 这个建立时间是从SLOE 拉低到Slave FIFO 数据有效。其二是tSRD ,即从SLRD 信号拉低到第1 个同步读时钟上升沿的时间。这两个建立时间应大于等于CY7C68013 数据手册规定的时间。由于该FPGA有59904 bit 的片上RAM, 这里使用其中4k byte 的RAM来生成FIFO 结构,这样从Slave FIFO 同步接收到的USB 数据就可以直接存入FPGA 片上的4k FI2FO 中。图4 是此进程的设计流程图。

图4 进程1 设计流程

进程2 : 用于完成将FPGA 的FIFO 中数据写入128kB RAM的设计。只要FPGA 的FIFO 中有数据,则该进程启动, FPGA 会连续地把片内FIFO 中取出的数据存入片外128kB 的高速静态RAM( IS63LV1024) 中, 这个片外的128kB RAM分为两个64kB 区,两个区轮流接收来自FPGA 片内FIFO 的数据, 当一个区接收完规定的显示数据后, FPGA 会置位send data flag 去启动进程3 ,如果FPGA 片内FIFO中还有数据, 则FPGA 会把RAM切换到另一个区继续接收片内FIFO 中的数据,其设计流程图如图5 所示。

图5 进程2 设计流程

进程3 : 此进程由send data flag 信号启动, 当发送数据标志被置位时, 此进程启动。此后, FPGA 开始从已完成显示数据接收的RAM区读取数据并送到4 位宽度的数据输出口, 此输出口与VT6103 相连。VT6103 以25MHz 时钟每次接收半个字节(4bit) ,然后经片内4B5B 编码、整形后将数据由差分输出口TX+ 和TX- 串行输出, 以把数据从USB2. 0 接口模块发给外部的显示处理模块。其设计流程图如图6所示。其中, VT6103 接收显示数据时序如图7 所示。每次接收4bit 后, 芯片内部都将自动对每次接收到的4bit 数据进行处理并以100MHz 的时钟频率串行差分输出给以太网变压器。

图6 进程3 设计流程

图7 接收显示数据时序

责任编辑;zl

-

哪个CY7C68013的芯片方便与GPIF接触?2019-03-22 2292

-

基于CY7C68013的USB_Camera开发教程2016-12-17 1560

-

cy7c680132016-03-10 3225

-

采用CY7C68013芯片的系统固件程序设计2016-01-22 1168

-

LED显示屏高速数据通讯接口设计2011-11-08 607

-

基于USB2.0芯片CY7C68013的高速数据通信接口设计2011-09-21 1520

-

基于CY7C68013的高速数据通信接口设计2011-09-08 991

-

基于CY7C68013的CCD图像传输系统2011-05-17 1284

-

CY7C68013器件中文手册2011-01-21 932

-

基于CY7C68013的液晶驱动电路设计2010-08-03 927

-

USB2.0控制器CY7C68013特点与应用2009-11-28 732

-

基于CY7C68013的USB数据采集系统2009-09-14 851

-

cy7c68013开发包及驱动2009-04-11 1967

全部0条评论

快来发表一下你的评论吧 !