PIC9054 PCI总线主控I/O加速器的性能及接口设计解决方案

接口/总线/驱动

描述

随着ISA总线逐步被淘汰,基于PCI总线的扩展板越来越被广泛地应用于各种高速、大数据量的处理系统中。尽管有许多供就商提供了各种通用的PCI总线扩展板,但在较多应用场合,用户还必须自行设计满足自己特殊需求的PCI扩展板,这就不可避免地会遇到PCI总线接口问题。对于绝大多数用户而言,选择专用PCI接口芯片进行PCI接口设计是必然的选择。

PIC9054是PLX公司推出的一种32位33MHz的PCI总线主控I/O加速器。它采用多种先进技术,使复杂的PCI接口应用设计变得相对简单。该芯片是目前主流的PCI接口芯片之一,其功能和性能如下:

·符合PCI V2.2规范,包含PCI电源管理特性;

·支持PCI双地址周期,地址空间高达4GB;

·提供两个独立的可编程DMA控制器,每个通道均支持块和分散/集中的DMA方式;

·PCI与Local Bus之间数据传输速率高达132MB/s;

·支持复用或非复用的32位局部总线操作,本地总线支持8位、16位和32位外围设备和存储设备,本地总线有三种工作模式:M模式、C模式和J模式,可通过模式选择引脚加以选择;

·PCI9054内部有可编程的FIFO,可以实现零等待突发传输及本地总线与PCI总线之间的异步操作,本地总线速率高达50MHz。

·支持可编程突发管理、可编程预取数技术和可编程中断产生;

·3.3V/5V兼容。

1、 PCI9054的工作模式

PCI9054有M、C、J三种工作模式,可通过模式选择控制引脚MODE[1:0]进行控制。当MODE[1:0]=“11”时,PCI9054工作在M模式;当MODE[1:0]=“00”时,PCI9054工作在C模式;当MODE[1:0]=“01”时,PCI9054工作在J模式;当MODE[1:0]=“10”时,娄保留工作状态。

M模式可与Motorola MPC850或MPC860系列高性能微处理器进行无缝连接;C模式可与Intel i960系列高性能微处理器进行无缝连接;J模式地址和数据线复用,应用很复杂,不过在一些特殊的应用场合,利用J模式和TI公司6000系列DSP的HPI口进行接口,其控制逻辑将比其它模式简单得多。

事实上,C模式能够满足绝大多数的应用需求,而且C模式的本地总线操作时序最简单,逻辑控制相对容易,其开发难度相对较低,因此,如无特殊需求,建议采用C模式。

2 、总线仲裁

在PCI9054与本地总线的接口设计中,一般需采用一片可编程逻辑器件CPLD/FPGA进行逻辑控制。在其控制逻辑中,总线仲裁逻辑是最关键、最核心的部分,直接影响计算机运行的稳定性。如果总线仲裁逻辑设计不合理,当计算机对PCI扩展板上的硬件资源进行访问时,计算机将会死机,因此PCI9054本地总线的所有控制逻辑必须服从于总线仲裁逻辑。

下面以C模式为例对PCI9054的总线仲裁逻辑进行探讨。在C模式下,PCI9054的143脚LHOLD和144脚LHOLDA是总线仲裁输入输出信号控制引脚,从公开发表的论文来看,有人将这两个引脚直接与设计电路相连进行总线仲裁逻辑设计。笔者在设计时也曾采用过这种方式,结果计算机运行很不稳定,经常莫名其妙地死机。仔细分析这种方式设计的电路会发现,该设计电路其实是利用器件的引脚传输延时配合总线仲裁电路的时序关系的。一般情况下,当环境温度、工作电压等外界因素变化时,大多数据逻辑器件的引脚延时会有相应的变化,因此用器件引脚延时设计出的总线仲裁逻辑电路运行不稳定应该是预料之中的事。

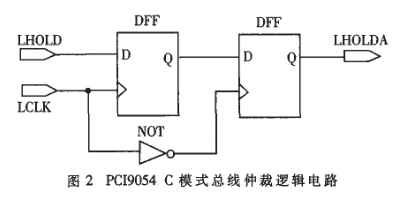

利用D触发器只在触发时钟有效边沿对信号敏感的特性进行设计,提高电路运行的稳定性,是可编程逻辑器件设计中的一种常用技巧。图1是PCI9054在C模式下对外设进行单一周期写操作的时序图,图2是利用可编程逻辑器件中的D触发器设计出的总线仲裁电路。

在图1中,ADS#、BLAST#和READY#信号的时序配合很重要,如果配合不好,计算机同样会死机。要提高电路稳定性,其设计思想与图2中的总线仲裁逻辑电路的设计思想相似。从多次实验情况来看,无论使用哪种工作模式,在该设计思想下设计出的本地总线控制逻辑电路运行非常稳定,没有死机的情况发生。

3、 存储器和I/O操作

通常PCI扩展板应该有配置空间、存储器空间和I/O空间三类资源。空间配置是必须的,根据设计需要,后两种资源可以只包含其中之一。PCI9054有S0和S1两个配置空间,两个配置空间都可以配置成存储器空间和I/O空间,存储器空间和I/O空间的配置既有相同之处,也有很大的区别。其相同点为两者都以字节为单位进行空间配置。不同之处有以下几点:

(1)存储器空间支持0~4GB的空间配置和映射,而I/O空间只支持0~256字节的空间配置和映射;

(2)存储器空间支持8位、16位和32位总线位宽配置和操作,而I/O空间只支持32位总线位宽配置和操作;

(3)存储器空间支持单一周期和突发模式读写操作,而I/O空间只支持单一周期读写操作;

(4)在编写设备驱动程序时,存储器空间用程序指针进行访问,I/O空间则用专用的函数进行访问。

如果不清楚存储器空间和I/O空间的异同步,有可能配错相应的寄存器。当计算机重新启动时,很有可能会启动不起来。除此之外,值得注意的是:在配置存储器空间和I/O空间时,不要将两种硬件资源配置到相同的空间,导致空间重叠,使驱动程序产生误操作。

4、 DMA和突发数据传输

在《PCI9054-DataBook》中,每种工作模式都将DMA和突发数据传输的时序图放在一起,这并不意味着DMA和突发数据传输是等同的,这是两个不同的概念。事实上,既可利用一周期的总线操作也可以利用DMA方式进行数据传输。

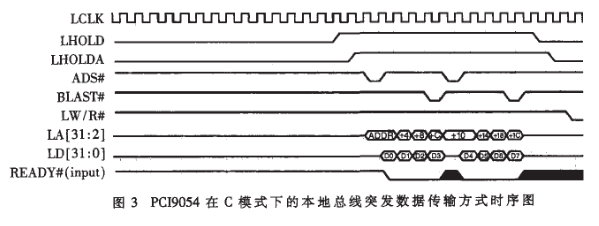

DMA和突发数据传输的作用是不同的。PCI9054中有两个DMA通道,可以独立工作,互不干扰。采用DMA方式传输数据,可以节省CPU资源;采用突发方式传输数据可以提高数据的传输率,充分发挥PCI总线数据传输率高的优点。因此,在高速大容量数据传输和处理系统中,将DMA和突发数据传输方式结合在一起是比较理想的,一方面可以充分发挥PCI总线的性能,另一方面可以将节省出的CPU资源对数据处理算法进行优化。图3是PCI9054在C模式正气突发数据传输方式的时序图。

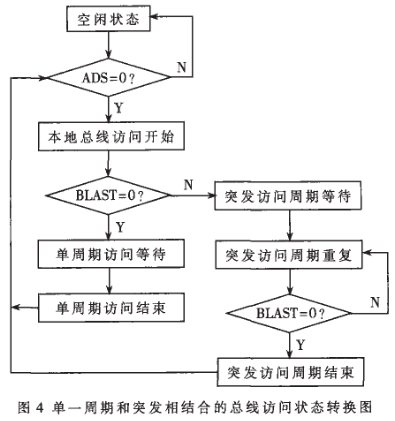

从图1和图3可以看出,用状态机实现该控制逻辑是比较理想的。图4是PCI9054在C模式下采用单一周期和突发相结合的总线访问状态转换图。用该状态转换图设计出的逻辑电路既可满足单一周期总线访问的需要,又可以满足突发方式传输数据的需要,具有很大的实用价值。

使用DMA和突发方式相结合进行数据传输时,驱动程序要作为如下设置:

(1)调用驱动程序中相应的API函数,找到PC机的物理地址;

(2)在设备驱动程序中使能突发寄存器;

(3)在设备驱动程序中使能总线位宽寄存器;

(4)在设备驱动程序中使能相应的寄存器,指明DMA传输的方向是PCI→LOCAL还是LOCAL→PCI;

(5)在设备驱动程序中指明本次DMA传输需要传输的字节数。

完成上述设置后,即可在突发方式下进行DMA传输,否则DMA传输会失败。

5、 PCI中断

PCI总线采用的是中断共享机制,所有的PCI扩展板在PCM插槽上共用一根信号线INTA#,通过电平触发方式响应PCI中断。每块PCI扩展板上的PCI9054提供的中断使能寄存器和中断状态寄存器能识别相应板卡上十几种类开的PCI中断。

当PCI插槽上只有一块PCI扩展板,而系统需要使用某种PCI中断时,则在主程序中将相应的中断使能寄存器置位,当相应的中断源中断信号到来时,与主板相连的信号线INTA#置一段时间低电平后,中断状态寄存器中的相应位被置位。当这两个寄存器的相应位都有效时,计算机响应相应的PCI中断,执行中断服务子程序。在《PCI9054-DataBool》中,INTA#信号为11个本地总线时钟周期,该时序图给不少设计人员带来了很多困惑。根据笔者的应用经验,INTA#信号在7μs左右是比较理想的,这与在Windows下PCI总线每秒钟可以响应十几万次中断的相关资料是相符的。

当PCI插槽上有多块PCI扩展板需要用到中断功能时,其工作过程与一块PCI扩展板差不多。唯一不同的是,首先驱动程序要利用一系列设备寄存器对扩展板进行设备识别,然后利用中断使能寄存器和中断状态寄存器对中断类型进行识别,最后响应相应的中断服务子程序。

在网上经常看到一些应用PCI9054的设计人员被以上讨论的问题所困扰,笔者在近两年从事PCI9054芯片应用设计中,也曾被这些问题困扰过。本文从这些方面对PCI9054芯片的应用进行了深入的探讨和总结,提出的所有技术解决方案都经过实验验证是可行的,这些内容在以往公开发表的论文中一般比较可见。本文探讨的内容对从事PCI9054芯片应用设计的人员应该会有一定的参考价值。

责任编辑:gt

-

采用专用接口电路PCI9054实现ARINC429总线接口板设计2019-04-26 2218

-

基于CPCI总线结构的微波接收机设计2018-07-25 3296

-

基于Hadoop的I/O硬件压缩加速器2017-11-27 981

-

PCI9054在高速数据采集系统中的应用2011-07-18 906

-

基于PCI9054的PCI接口数据通信系统2011-06-02 1307

-

PCI 总线接口芯片9054及其应用2011-05-14 1092

-

基于PCI9054的数据转换模块设计2011-01-14 585

-

基于PCI9054桥路器的数据传输的接口逻辑设计2010-09-08 3872

-

基于PCI9054的接口卡2010-07-21 942

-

PCI总线接口技术及其在高速数据采集系统中的应用2009-12-08 1385

-

基于PCI总线的高速数据采集接口的设计与实现2009-07-30 612

-

嵌入式PCI总线主模式设计2009-07-07 638

-

PCI总线接口芯片PCI9054及其应用2008-10-09 9030

全部0条评论

快来发表一下你的评论吧 !