allegro软件的绝对传输延迟是什么,绝对传输延迟应该怎么设置呢?

描述

标题:allegro软件的绝对传输延迟是什么,绝对传输延迟应该怎么设置呢?

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

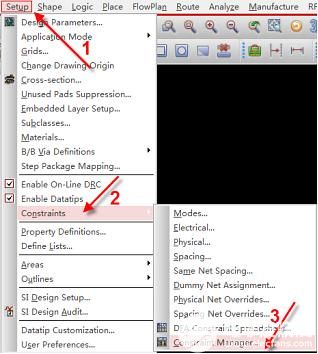

第一步,打开规则管理器,执行菜单命令Setup-Constraints,在下拉菜单中选择Constraint Manager,如图5-90所示,进入到规则管理器中;

删除

(选填) 图片描述

图5-90 规则管理器示意图

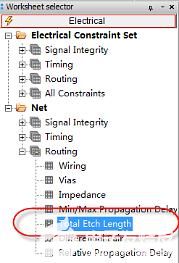

第二步,进入规则管理器以后,在CM左侧的目录栏中选择Net,在Routing中选择Total Etch Length,如图5-91所示,设置信号的线的总长度;

删除

(选填) 图片描述

图5-91 设置绝对长度示意图

第三步,进入到右边栏,对需要做等长的信号线,创建好Bus,在Total Etch Length中输入最小值、最大值即可,如图5-92所示,每一组的信号线都会跟这个对比产生相对应的误差,按这个误差做等长即可;

删除

(选填) 图片描述

图5-92 设置绝对长度最大值最小值示意图

第四步,回到PCB界面,如果需要做等长的信号线没有满足最小值或者最大值的要求,都会报相对应的DRC错误,用于提醒工程师做等长设计。

上述,就是在Allegro软件中,如何设置绝对传输延迟的方法解析。

-

使用ESP8266模块进行UDP传输,重新连接路由后发送数据有延迟怎么避免?2024-07-12 588

-

是否有uart命令来设置传输时的字符延迟?2024-07-16 481

-

在同步电路中影响性能都有哪些方面呢?传输延迟,惯性延迟怎么形成的呢?映射到硬件上怎么形成这种现象呢?2018-03-09 4416

-

请问6678中PA_muloticoreExample_exampleProject所传包类型是什么?文档中对传输包的组成描述也与里程中使用的不同是为什么?2018-06-25 2002

-

个人对传输线变换器的粗浅理解2019-06-20 4359

-

JTIDS信息传输时间延迟分析2009-04-11 567

-

过孔对传输线信号的影响详解2007-10-10 5059

-

OP放大器有相位延迟补偿的高速绝对值电路2010-05-11 3001

-

如何使用模型添加法设置相对传输延迟的等长规则2020-04-15 6752

-

PCB技术:allegro软件中如何通过模型添加相对传输延迟的等长规则2020-10-14 6928

-

如何快速解决CAN/CAN FD通讯延迟困扰2020-12-26 2651

-

关于超低延迟实时流媒体传输技术的图文详解2021-04-16 5900

-

Allegro小技巧 | 如何使用Allegro直接添加相对传输延迟的等长规则2022-05-13 6526

-

阈值电压对传播延迟和跃迁延迟的影响2023-09-07 2257

-

延迟低至30ms+ LLSM流媒体传输模块低延迟方案推荐2025-06-04 1612

全部0条评论

快来发表一下你的评论吧 !