采用EP2C5T144C8 FPGA实现PS/2接口的设计方法

接口/总线/驱动

描述

引言

当前嵌入式系统技术已得到了广泛应用,但传统嵌入式系统的人机接口多采用小键盘操作的文本菜单方式,用户操作较为不便。本设计利用FPGA实现对PS/2接口鼠标的控制,是在以VGA作为输出设备的单片机系统上初步实现图形化用户界面的方案,它成本低、效果好,并且有很强的实用性。

FPGA(Field Programmable Gate Array)是 20世纪80年代中期出现的高密度、可编程逻辑器件,FPGA及其软件系统是开发数字电路的最新技术,它利用EDA技术,以电路原理图、硬件描述语言及状态机等形式输入设计逻辑,提供功能模拟、时序仿真等模拟手段,在功能模拟和时序仿真度满足要求后,经过一系列变换,将输入逻辑转换成FPGA器件的编程文件,以实现专用集成电路。本设计选用Altera公司推出的CyclONe II系列的EP2C5T144C8 FPGA来设计PS/2接口,体积减小,可靠性提高。

PS/2接口和协议

接口的物理特性

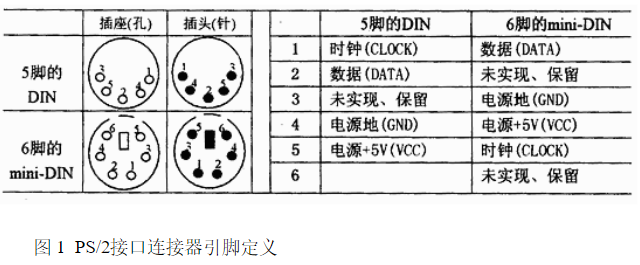

PS/2接口用于许多现代的鼠标和键盘,由IBM最初开发和使用。物理上的PS/2接口有两种类型的连接 器 :5脚的DIN和6脚的MINI-DIN。图1就是两种连接器的引脚定义。使用中,主机提供+5V电源给鼠标,鼠标的地连接到主机电源地上。

接口协议原理

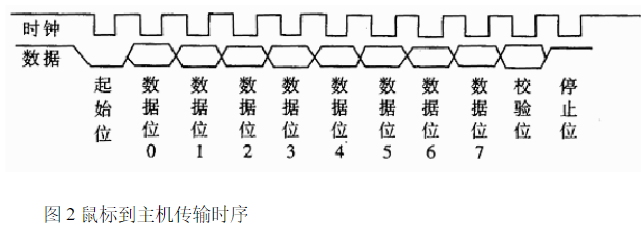

PS/2鼠标接口采用一种双向同步串行协议,即每在时钟线上发一个脉冲,就在数据线上发送一位数据。在相互传输中,主机拥有总线控制权,即它可以在任何时候抑制鼠标的发送,方法是把时钟线一直拉低,鼠标就不能产生时钟信号并发送数据。在两个方向的传输中,时钟信号都由鼠标产生,主机不产生通信时钟信号。

如果主机要发送数据,就必须控制鼠标产生时钟信号,方法如下:主机首先下拉时钟线至少100μS抑制通信,然后再下拉数据线,最后释放时钟线。鼠标检测到这个时序状态后,会在10mS内产生时钟信号。如图3中(A)时序段。主机和鼠标之间,传输数据帧的时序如图2、图3所示。

PS/2鼠标的工作模式和协议数据包格式

PS/2鼠标的四种工作模式

PS/2鼠标的四种工作模式分别是:Reset模式,当鼠标上电或主机发复位命令(0xFF)给它时,进入这种模式;STream模式,鼠标的默认模式,当鼠标上电或复位完成后,自动进入此模式,鼠标基本上以此模式工作;Remote模式,只有在主机发送了模式设置命令(0xF0)后,鼠标才进入这种模式;Wrap模式,这种模式只用于测试鼠标与主机连接是否正确。

数据包结构

PS/2鼠标在工作过程中,会及时把它的状态数据发送给主机。发送的数据包格式如表1所示。

Byte1中的Bit0、Bit1、Bit2分别表示左、右、中键的状态,状态值0表示释放,1表示按下;Byte2和Byte3分别表示X轴和Y轴方向的移动计量值,是二进制补码值;Byte4的低四位表示滚轮的移动计量值,也是二进制补码值,高四位作为扩展符号位。这种数据包由带滚轮的三键三维鼠标产生,若是不带滚轮的三键鼠标,产生的数据包没有Byte4,其余的相同。

VGA信号时序

图4所示是计算机VGA(640×480,60Hz)图像格式的信号时序图,其点时钟DCLK为25.175MHz,场频为59.94Hz。图中,Vsync为场同步信号,场周期Tvsync为16.683mS,每场有525行,其中480行为有效显示行,45行为场消隐期。场同步信号Vs每场有一个脉冲,该脉冲的低电平宽度twv为63μS(2行)。场 消隐期包括场同步时间twv、场消隐前肩tHV(13行)和场消隐后肩tVH(30行),共45行。行周期THSYNC为31.78μS,每显示行包 括800点,其中640点为有效显示,160点为行消隐期(非显示 区)。行同步信号Hs每行有一个脉冲,该脉冲的低电平宽度tWH为3.81μS(即96个DCLK);行消隐期包括行同步时间tWH,行消隐前肩tHC(19个DCLK)和行消隐后肩tCH(45个DCLK),共160个点时钟。复合消隐信号是行消隐信号和场消隐信号的逻辑与,在有效显示期复合消隐信号为高电平,在非显示区域它是低电平。

设计实现

实现功能

1、 用FPGA实现PS/2鼠标接口。

2、鼠标左键按下时十字形鼠标图象的中间方块改变颜色,右键按下时箭头改变颜色。

3、 Reset按键:总复位。

设计原理

主机复位后,首先向鼠标发送初始化命令(0xf4)。当鼠标收到命令字后会给出一个应答字节(0xfa),主机根据应答字节来判断鼠标是否正确应答。如果应答正确则接收鼠标数据包,然后从接收到的数据包中获得鼠标位置及状态数据,并输出给显示模块。显示模块在CRT上显示出当前鼠标的状态和位置,否则,停止处理。如图5。

如图6,当状态机m2_state复位时,即进入m2_reset状态,并在 一个clk周期后进入m2_hold_clk_l状态,当ps2_clk_hi_z(时钟线)被拉低并保持400μS后进入m2_data_low_1状态,此时向鼠标 发送起始 位和d[0]、d[1](d[0]=d[1]=0)。完成后进入m2_data_high_1状态, 发送d[2](d[2]=1)并进入m2_data_low_2状态,此时向鼠标发送d[3]位(d[3]=0), 完成发送进入m2_data_high_2状态,向鼠标发送d[4]、d[5]、d[6]、d[7](d[4]=d[5]=d[6]=d[7]=1),完成发送进入m2_data_low_3状 态,向鼠标发送奇偶校验位,然后进入m2_data_high_3状态,将数据线拉高,等待鼠标返回应答信号。若PS/2时钟信号下降沿来临时,数据线仍未变为高电平,则进入m2_error_no_ack状态,此时握手失败,系统将保持m2_error_no_ack状态直到下一次复位,否则进入m2_await_response状态接收应答字,接收完成进入m2_verify数据校验,然后进入m2_use状态,锁存输出数据,并进入m2_wait状态,等待接收数据。当检测到时钟下降沿后进入m2_gather状态,接收鼠标数据包,接收完成进入m2_verify状态,此时便形成了数据接收循环。

PS/2程序源码

entity mouse is

Port (clk : in std_logic; reset : in std_logic; ps2_clk : inout std_logic; ps2_data : inout std_logic; left_button : out std_logic; right_button : out std_logic; mousex: buffer std_logic_vector(9 downto 0); mousey: buffer std_logic_vector(9 downto 0); data_ready : out std_logic; error_no_ack : out std_logic);

end mouse;

architecture Behavioral of mouse is

--变量、信号定义(略)

begin

ps2_clk 《= ‘0’ when ps2_clk_hi_z=‘0’ else ‘Z’;

ps2_data 《= ‘0’ when ps2_data_hi_z=‘0’ else ‘Z’;

--检测ps2clk上升沿和下降沿(略)

m2statech: process (reset, clk) ------------------m2 状态

begin

if (reset=‘0’) then

m2_state 《= m2_reset;

elsif (clk‘event and clk=’1‘) then

m2_state 《= m2_next_state;

end if;

end procESS;

--m2 状态传输逻辑

m2statetr: process (m2_state, q, fall,rise,watchdog_timer_done,bitcount,ps2_data,packet_good)

begin

ps2_clk_hi_z 《= ’1‘;

ps2_data_hi_z 《= ’1‘;

error_no_ack 《= ’0‘;

output_strobe 《= ’0‘;

case m2_state is

when m2_reset =》 -- 复位后向鼠标发送命令字

m2_next_state 《= m2_hold_clk_l;

when m2_wait =》

if (fall=’1‘) then

m2_next_state 《= m2_gather;

else

m2_next_state 《= m2_wait;

end if;

when m2_gather =》

if ((watchdog_timer_done=’1‘) and (bitcount=TOTAL_BITS))then

m2_next_state 《= m2_verify;

else

m2_next_state 《= m2_gather;

end if;

when m2_verify =》

--if (bitcount 《 TOTAL_BITS) then

--m2_next_state 《= m2_wait;

--else

m2_next_state 《= m2_use;

--end if;

when m2_use =》

output_strobe 《= ’1‘;

m2_next_state 《= m2_wait;

-- 用状态机的9个状态实现命令字传输,使鼠标进入“streaming”模式,并等待鼠标正确应答 [page]

when m2_hold_clk_l =》

ps2_clk_hi_z 《= ’0‘; -- 启动看门狗!

if (watchdog_timer_done=’1‘) then

m2_next_state 《= m2_data_low_1;

else

m2_next_state 《= m2_hold_clk_l;

end if;

when m2_data_low_1 =》

ps2_data_hi_z 《= ’0‘; -- 数据位 开始位, d[0] and d[1]

if (fall=’1‘ and (bitcount = 2)) then

m2_next_state 《= m2_data_high_1;

else

m2_next_state 《= m2_data_low_1;

end if;

when m2_data_high_1 =》

ps2_data_hi_z 《= ’1‘; -- 数据位 d[2]

if (fall=’1‘ and (bitcount = 3)) then

m2_next_state 《= m2_data_low_2;

else

m2_next_state 《= m2_data_high_1;

end if;

when m2_data_low_2 =》

ps2_data_hi_z 《= ’0‘; -- 数据位 d[3]

if (fall=’1‘ and (bitcount = 4)) then

m2_next_state 《= m2_data_high_2;

else

m2_next_state 《= m2_data_low_2;

end if;

when m2_data_high_2 =》

ps2_data_hi_z 《= ’1‘; -- 数据位 d[4],d[5],d[6],d[7]

if (fall=’1‘ and (bitcount = 8)) then

m2_next_state 《= m2_data_low_3;

else

m2_next_state 《= m2_data_high_2;

end if;

when m2_data_low_3 =》

ps2_data_hi_z 《= ’0‘; -- 奇偶校验位

if (fall=’1‘) then

m2_next_state 《= m2_data_high_3;

else

m2_next_state 《= m2_data_low_3;

end if;

when m2_data_high_3 =》

ps2_data_hi_z 《= ’1‘; -- 允许鼠标拉成低电平(ACK脉冲)

if (fall=’1‘ and (ps2_data=’1‘)) then

m2_next_state 《= m2_error_no_ack;

elsif (fall=’1‘ and (ps2_data=’0‘)) then

m2_next_state 《= m2_await_response;

else

m2_next_state 《= m2_data_high_3;

end if;

when m2_error_no_ack =》

error_no_ack 《= ’1‘;

m2_next_state 《= m2_error_no_ack;

-- 为了鼠标正确进入“streaming”模式,状态极必须等待足够长的时间,确保鼠标正确应答0xFA。

when m2_await_response =》

--if (bitcount = 22) then

m2_next_state 《= m2_verify;

--else

-- m2_next_state 《= m2_await_response;

--end if;

when others =》 m2_next_state 《= m2_wait;

end case;

end process;-----------------------------m2 状态结束

-- 位计数器 (略)

-- 数据移位寄存器(略)

-- 看门狗时间计数器(略)

watchdog_timer_done 《= ’1‘ when (watchdog_timer_count=WATCHDOG-1) else ’0‘;

packet_good 《= ’1‘; -- 接收数据包有效标志

outdata: process (reset, clk) -- 输出数据

begin

if (reset=’0‘) then

left_button 《= ’0‘;

right_button 《= ’0‘;

elsif (clk’event and clk=‘1’) then

if (output_strobe=‘1’) then

left_button 《= q(1);

right_button 《= q(2);

mouseyy 《= not (q(6) & q(6) & q(30 downto 23)) + “1”;

end if;

end if;

end process;

cordinatex: process (reset, clk)

begin

if (reset=‘0’) then

mousex 《= “0110010000”; -- 400

elsif (clk‘event and clk=’1‘) then

if (output_strobe=’1‘) then

if ((mousex 》= 797 and q(5)=’0‘) or (mousex 《= 2 and

q(5)=’1‘)) then

mousex 《= mousex;

else

mousex 《= mousex + (q(5) & q(5) & q(19 downto

12));--q(5):xsign q(6):ysign

end if;

end if;

end if;

end process;

cordinatey: process (reset, clk)

begin

if (reset=’0‘) then

mousey 《= “0100101100”; -- 300

elsif (clk’event and clk=‘1’) then

if (output_strobe=‘1’) then

if ((mousey 》= 597 and q(6)=‘1’) or (mousey 《= 2

and q(6)=‘0’)) then

mousey 《= mousey;

else

m ousey 《= mousey + mouseyy; --(q(6) & q(6) & q(30

downto 23));

end if;

end if;

end if;

end process;

data_ready 《= output_strobe;

end Behavioral;

结束语

该设计采用了清华大学THCII-1创新SoPC实验套件进行综合、仿真和下载,测试得到了满意的效果,完整地实现了对PS/2和VGA的时序驱动。

该设计可以被应用到各种需要鼠标操作、以VGA作为显示的嵌入式系统中,从而大大提高人机交互能力,降低了开发成本,提高了开发效率,使系统的稳定性也得到了可靠的保障。

责任编辑:gt

-

dw8051是怎样移植到altera的EP2C5T144C8N上去的?2021-06-18 1375

-

微雪电子EP2CFPGANIOSII开发板简介2019-12-23 2138

-

微雪电子EP2C FPGA NIOSII开发板简介2019-12-19 2380

-

开发板ep1c3t144fpGAdevelopboard2017-03-20 1528

-

EP2C8T144I8芯片资料2016-08-15 3303

-

EP2C5T144的时钟问题2014-10-31 3446

-

EP2C8T144I8 Altera QFP144 资料 PDF2013-12-06 2658

-

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这三种芯片的区别2013-07-21 2193

-

基于FPGA的多轴控制器设计2013-04-27 1273

-

请问altera芯片EP2C5T144C8和C8N的区别?2012-03-30 6558

-

EP2C5T144开发板原理图2011-12-06 6161

-

基FPGA Cyclone II_EP2C5 EP2C8的频2008-11-30 1009

全部0条评论

快来发表一下你的评论吧 !