基于CAN控制器SJA1000实现非智能适配卡的设计

接口/总线/驱动

描述

引言

控制器局域网CAN (Controller Area Network)是目前被批准为国际标准的少数现场总线之一。CAN网络可采用多主方式工作。它采用非破坏性的总线仲裁技术,其信号传输和控制采用短帧结构,因而具有较强的抗干扰能力和低耦合性;CAH网络的通讯速率范围为5 kbs/10 km~lMbs//40m,驱动节点数可达110个。它的传输介质可以是双绞线、同轴电缆或光纤,选择十分灵活;每帧信息都有CRC校验及其它检错措施,因而数据出错率极低,可靠性很高;当其传输的信息出错严重时,节点可自动断开与总线的联系,以使总线上其它的操作不受影响。

虽然目前PCI、USB等总线技术得到了快速发展,但在大量应用的测试微机及工控机中,用的最多的还是ISA (Industry Standard Architecture.工业标准体系结构)总线。ISA总线具有16位数据宽度,最高工作频率为8MHz,数据传输速率达到16MB/s,地址总线有24条,可寻址16MB的地址单元,其总线信号分为5类,分别为地址线、数据线、控制线、时钟线和电源线。

为了解决CAN控制器SJA1000与ISA总线各信号线的时序配合与逻辑配合问题,设计了一种基于CAN总线的非智能适配卡。该适配卡已应用于研制的“基于CAN总线的运动控制系统”中,运行情况良好。

非智能型ISA总线CAN适配卡的总体结构

CAN控制器SJA1000的地址数据总线是分时复用的,通过ALE信号的下降沿可锁存总线上的地址信号;ISA总线上的地址和数据总线是单独提供的,它不能直接和SJA1000的地址数据总线相连。本设计利用地址译码电路来对地址信号线进行译码,从而为CAN适配卡分配出一定的端口地址。然后再利用74HC373芯片的数据锁存功能锁存第一次I/O操作中通过ISA数据总线传送的数据信号,以便作为访问CAN控制器SJA1000中寄存器的地址信号,最后在第二次I/O操作中完成对SJA1000中相应地址寄存器的读写操作。其适配卡的总体结构如图1所示。

图1中,地址锁存器74HC373可看作SJA1000的地址端口,而SJA1000本身可看作SJA1000的数据端口,另外还有对SJA1000进行硬件复位的复位端口。图中的基地址译码电路以AEN作为使能信号,对A2~A9地址信号进行译码就可得到适配卡的基地址;组合AO和A1地址信号可得到各端口的偏移地址。SJA1000与ISA的通讯采用两次I/O操作的方法,第一次先往地址端口送地址,第二次再对数据端口进行访问。这里所说的地址及数据端口都是对SJAl000而言的,通过ISA总线的数据线可获得被访问的SJA1000寄存器的地址及所传送的数据。控制端口译码电路可将CPU送来的控制信号和地址信号按一定的逻辑关系进行组合,从而生成一组新的功能信号作为接口控制信号。通过SJA1000复位电路可对SAJ1000进行复位,具体操作可采用上电复位、程序复位及按键复位三种硬件复位方式。

适配卡硬件的设计

基地址译码电路设计

图2所示是一种具体的基地址译码电路。一般情况下,根据系统需要,地址译码电路可对ISA地址线的端口地址译码,并可用AO~A9来表示。基地址译码电路对A9~A2进行译码,则可作为卡上端口的基地址。

图2中,74HC688是一个8位量值比较器,当时Pi=Qi(i=0…7),P=Q的反端输出低电平。当ISA总线的AEN为高电平时,总线工作在DMA方式;而当AEN为低电平时,CPU拥有对总线的控制权。非智能型适配卡的工作过程实际上就是CPU对I/O的操作过程,期间,AEN始终为低电平,可用于控制74HC688的选通端G反。只有在I/O操作时,才允许它选择地址。由于使用的是拨码开关,用户可预先设定适配卡的基地址。卡上各端口的偏移由A1和A0选择,并可通过软件控制,本设计中的定义地址端口偏移为00,数据端口偏移为01,复位端口偏移为11。

控制信号产生电路

该适配卡的控制信号产生电路如图3所示。该电路的主要作用是把CPU送来的控制线和地址线按照一定的逻辑关系进行组合,以生成一组新的功能信号输出。该信号可作为接口控制信号去控制SJA1000、74HC373、74HC245等芯片的工作状态。由于基地址译码电路的输出信号为P=Q的反(低电平有效),SJA1000地址端口偏移地址为00H,数据端口偏移地址为01H

适配卡在工作过程中,各芯片的逻辑时序关系是:当74HC373输出数据有效时,74HC245输出为高阻态;当74HC373输出呈高阻态,且SJA1000的数据直接传回ISA总线时,74HC245输入输出工作正常。具体来讲,假设CAN的基地址为300H,且访问SJA1000是分两次I/O操作完成的,那么,第一次往端口300H送出的数据可在写信号的后沿被锁存在74HC373中,这个操作中,74HC245的E与74HC373的LE端有效,而74HC373的OE端为高电平,74HC373输出端为高阻态;当第二次访问数据端口301H时,SJA1000被选中,此时CPU可对SJA1000的相应单元进行读/写操作。具体的操作过程分为读、写两种情况。当第二次I/O操作到来时,SJA1000会在BALE信号下降沿将第一次I/O操作时锁存在74HC373中的数据作为地址锁存,该过程中,74HC245的E反为高电平,输出呈高阻态,74HC373的OE的反为低电平,输出端有效,可向SJA1000传送地址信号。当地址被SJA1000锁存以后,此时如果进行的是读操作,那么,在读信号有效期间(低电平),74HC373的输出允许OE反端为高电平,74HC373输出端呈高阻态,这时SJA1000可将选中单元的寄存器内容输出到数据总线,并通过74HC245驱动送入CPU中。而在地址锁存后,如果进行的是写操作,那么,74HC373的输出允许端始终有效,此时可在写信号有效期间,将数据写入SJA1000的相应单元中。

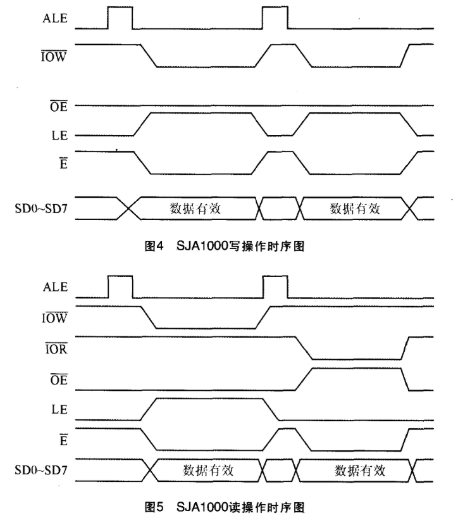

计算机通过ISA总线对CAN控制器SJA1000进行读写的时序分别如图4和图5所示。

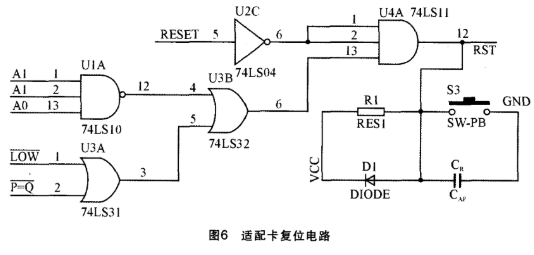

复位电路

SJA1000正常工作前,只有通过复位引脚对其进行可靠的硬件复位,才能对SJA1000中的寄存器进行正确的读写操作。使SJA1000可靠复位的电平持续最小时间为0.1μs,PC系统复位电平持续时间可达几微秒。系统复位信号RESET在系统电源接通时为高电平,经反向器后可直接用于对SJA1000进行复位。图6所示是适配卡的复位电路,对SJA1000的复位具有开机上电复位、程序复位以及按键复位等三种方式。

在图6中,A1和A0经过与非门74LSl0后,为复位电路产生的偏移地址为11,该地址信号与IOW反、P=Q反等信号经过逻辑组合,同时配合程序设计可产生对SJA1000的复位信号。程序设计时只需对复位端口写入一个数据即可实现程序复位。而按键复位则可在系统运行出现通信故障时,直接用于对CAN控制器SJA1000进行硬件复位。

适配卡的软件设计

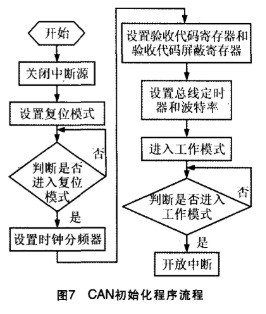

软件设计的关键部分是CAN通信程序的设计。通信程序(流程如图7、8、9所示)可分为三部分:CAN初始化程序、接收程序、发送程序。初始化是通信的前提,主要完成对CAN控制器的一些寄存器的设置。由于SJA1000支持中断操作,因此可以用中断服务程序来完成数据的接收和发送,以提高系统的工作效率。

实际上,只有在复位模式下才可以对SJA1000进行初始化,初始化主要包括工作方式的设置、接收滤波方式的设置、接收屏蔽寄存器和接收代码寄存器的设置、波特率参数设置和中断允许寄存器的设置等。完成初始化后,即可将SJA1000设置为工作状态,以进行正常的通信。发送子程序负责节点报文的发送。发送时,读取状态寄存器并对各位进行适当判断,并将待发送的数据按特定格式组合成一帧报文,送入SJA1000发送缓存区中,然后启动SJA1000发送;接收子程序则负责节点报文的接收以及其它情况的处理。在处理接收报文的过程中,还要对总线关闭、错误报警、接收溢出等情况进行处理。

CAN适配卡与计算机可采用中断方式通信。但在WIN API中不能直接控制中断,只有在操作系统底层为CAN适配卡编写虚拟设备驱动程序(VxD)才可以利用中断。这需要在虚拟设备驱动程序中将中断虚拟化,并在中断事件响应函数中编写所需代码,同时为应用程序提供访问接口。应当注意的是:计算机通过ISA总线对CAN适配卡上的SJA1000进行访问采用的是两次I/O操作,第一次往地址端口送地址,第二次对数据端口进行访问。其具体的实现代码如下:

//向指定的SJA1000寄存器(地址为addr)写一个字节数据(data),CAN_BASE为基地址

void CanIRQ::writeByte(int CAN_BASE,unsigned char addr,unsigned char data)

{

_outp(CAN_BASE,addr);

_outp(CAN_BASE+1,data);

}

//从指定的SJA1000寄存器(地址为addr)读一个字节数据(data)

unsigned char CanIRQ::ReadByte(int CAN_BASE,unsigned char addr)

{

unsigned char result;

_outp(CAN_BASE,addr);

result=_inp(CAN_BASE+1);

return result;

}

在访问SJA1000的程序中,可以直接调用以上两子函数。这样,其发送程序段代码为:

Bool CanIRQ::CanTrans(int CAN_BASE,unsigned char*pTransBuf)

{

status=ReadByte(CAN_BASE,SR); //SR为状态寄存器地址

for(i=0;i

{

WriteByte (CAN_BASE,*pTFansBuf,ptbuf;//pTransBuf为发送缓冲区地址

ptbuf++;pTransBuf++;

}

}

结束语

通过解决计算机ISA总线与CAN控制器SJA1000的逻辑配合与时序配合可完成基于CAN总线的非智能适配卡设计。该适配卡现已成功地应用于笔者所研制的基于CAN总线的测控系统中。实际上,若在适配卡上增加CAN通信控制器,也可使一卡带多条CAN总线,以增加网络节点,扩大网络规模。另外,还可以在适配卡的应用程序中,根据应用系统需要编写各种监控程序来扩展系统功能。

责任编辑:gt

-

SJA1000独立CAN控制器中文资料2023-10-13 721

-

SJA1000独立CAN控制器中文手册2023-04-07 1074

-

基于SJA1000的完整CAN节点设计2021-06-18 10217

-

基于VxWorks操作系统实现PC/104-CAN适配卡的驱动系统设计2020-09-08 4821

-

基于FPGA的VHDL语言设计控制器SJA1000的IP软核设计2020-04-12 3749

-

DSP与CAN控制器SJA1000的总线接口的差别2017-10-30 2360

-

CAN总线控制器SJA1000的初始化程序设计2016-05-06 928

-

基于SJA1000的CAN总线智能控制系统设计2012-08-20 3660

-

SJA1000独立的CAN控制器应用指南2009-11-18 992

-

SHARC DSP与SJA1000的CAN总线接口设计2009-09-27 1649

-

SJA1000 在CAN 总线系统节点的应用2009-05-13 1111

-

CAN控制器SJA1000及其应用2008-10-03 7753

-

基于CAN控制器SJA1000的智能高速控制系统设计2006-03-11 2601

全部0条评论

快来发表一下你的评论吧 !