如何通过运算放大器实现ppm精度

模拟技术

描述

作者:Barry Harvey ADI公司

工业和医疗设计推动产品的精度和速度日益提高。模拟集成电路行业总体能够跟上速度的发展要求,但在精度要求上却有所不足。许多系统都竞相迈入1 ppm精度之列,特别是如今,1 ppm的线性ADC日益普遍。本文将介绍运算放大器的精度局限性,以及如何选择为数不多的有可能达到1 ppm精度的运算放大器。另外,我们还将介绍一些针对现有运算放大器局限性的应用改善。

精度(Accuracy)与数值相关:系统特性与绝对真实数值之间的差距。精密(Precision)是以数字形式表示的数值深度。在本文中,我们将使用精度一词,它包括噪声、偏移、增益误差和非线性度等系统测量的所有限制。许多运算放大器的某些误差在ppm量级,但没有个运算放大器的所有误差都达到了ppm量级。例如,斩波放大器可提供ppm级的失调电压、直流线性度和低频噪声,但它们的输入偏置电流和频率线性度存在问题。双极性放大器具有低宽带噪声和良好的线性度,但其输入电流仍可能导致内部电路误差(对于内部电路,我们将使用“应用”一词)。MOS放大器具有出色的偏置电流,但通常在低频噪声和线性度领域存在缺陷。

在本文中,我们将在转换函数中使用大致相当于1 ppm的非线性度表现谐波失真的–120 dBc失真。

非ppm放大器类型

让我们来看看非高线性度的放大器类型。线性度最低的类型即所谓的视频或线路驱动器放大器。这些都是直流精度不太好的宽带放大器:偏移达几毫伏,偏置电流在1 µA至50 µA范围内,并且1/f噪声性能通常较差。理想的直流精度在0.3%至0.1%之间,但交流失真可以介于–55 dBc至–90 dBc(线性度:2000 ppm至30 ppm)之间。

下一项分类是传统经典运放设计,例如OP-07,可能具有高增益、CMRR、PSRR以及良好的失调电压和噪声性能,但其失真却无法优于–100 dBc,特别是在达到1 kΩ或更高负载的情况之下。

然后,还有一些或新或旧的廉价放大器,其失真在负载超过10 kΩ的情况下都无法优于–100 dBc。

此外,还有音频放大器类运算放大器。它们相当实惠,且失真表现可能非常好。但是,它们的设计不合适且不能提供良好的失调电压和1/f噪声性能。此外,他们的失真或许在大于10 kHz后也不能变的更好了。

有些运算放大器旨在支持MHz信号的线性度。它们通常为双极性,并具备较大的输入偏置电流和1/f噪声。在该应用领域,运算放大器更多追求的是–80 dBc至–100 dBc程度的性能,实现ppm性能不太现实。

无论宽带及压摆率多大,电流反馈放大器也不能支持深线性度,甚至是适度的精度。它们的输入级有很多误差源,并且增益、输入和电源抑制性能都不高。电流反馈放大器还具有热漂移效应,会大幅拓展正常的建立时间。

然后,我们拥有现代的通用型放大器。它们一般具备1 mV的偏移和微伏级1/f噪声。支持–100 dBc失真,但在高负载时通常无法实现。

运算放大器的误差源

图1显示的是简化的运算放大器框图,并添加了交流和直流误差源。拓扑为带有输入跨导(gm)的单极点放大器,驱动输出缓冲单元的增益节点。尽管有许多运算放大器拓扑,但所示的误差源对它们全部适用。

图1.简化的运算放大器和误差源

输入噪声

有的输入噪声电压VNOISE包含宽带和1/f频谱成分。如果噪声的幅度类似或超过系统LSB,则无法准确地测量信号。例如,如果宽带噪声为6 nV/√Hz,系统带宽为100 kHz,那么输入端的有效值噪声则会达到1.9 µV。我们可以使用滤波器来降低噪声:例如,将带宽降至1 kHz可使噪声降至0.19 µV rms或1 µV p-p(峰峰)左右。频域的低通滤波可降低噪声幅度,就像ADC输出随时间推移而平均化一样。

不过,由于速度太慢,1/f噪声实际上无法过滤或均化。1/f噪声通常使用0.1 Hz至10 Hz频谱范围内生成的峰峰值电压噪声体现。大多数运算放大器的低频噪声都介于1 µV p-p至6 µV p-p之间,因而不太适合对直流精度要求高的ppm级别,特别是在提供增益的情况下。

图2显示的是优良的高精度放大器(LT1468)的电流和电压噪声。

图2.LT1468输入电压和电流噪声

在图1的输入端,还有偏置电流噪声源INOISE+和INOISE–。它们包含宽带和1/f频谱成分。INOISE乘以等效电阻会产生更多输入电压噪声。一般而言,同相端和反相端的两个电流噪声之间互不相关,不会随着两端输入电阻值相等而抵消,而是以rms方式增加。INOISE乘以输入等效电阻产生的噪声电压常常会超过1/f区的VNOISE。

输入共模抑制和偏置误差

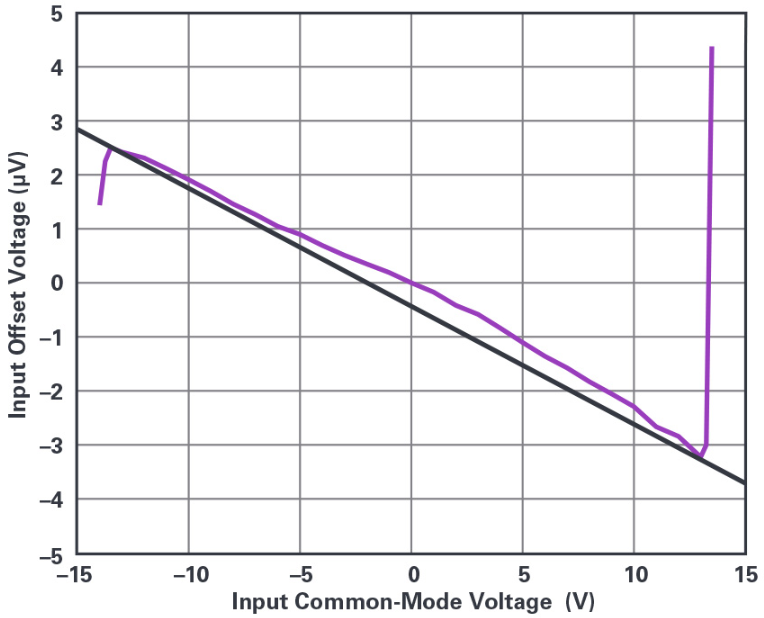

下一种误差源是VCMRR。这体现在共模抑制比指标参数上,其中失调电压会随着相对于两个供电轨的输入电平而变化(所谓的共模电压,VCM)。使用的符号指示箭头方向的电源相互影响,通过它的分割线表示其可变,但可能是非线性变化。CMRR对信号的主要影响在于使线性部分与增益误差无法区分。非线性部分将会失真。图3显示了LT6018的CMRR。增加的线与CMRR曲线在该曲线分化到过载之前的极点相交。该线的斜率提供的CMRR = 133 dB。范围每相差30 V,CMRR曲线与理想线之间的偏差仅约为0.5 µV,表示ppm以下级别的输入非常成功。其他放大器的曲率可能更大。

图3.LT6018输入失调电压与VCM

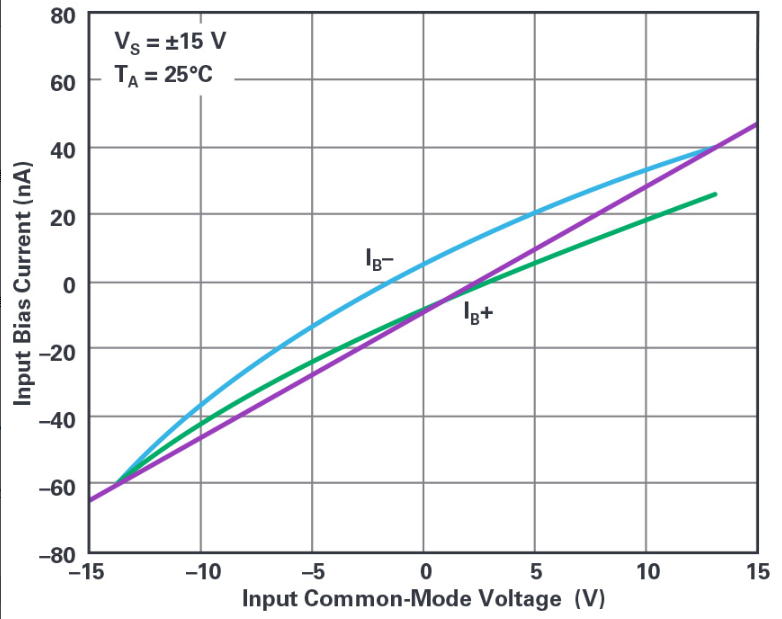

失调电压(VOS)将归入此处的CMRR。斩波放大器的输入失调电压低于10 µV,相对于2 V p-p至10 V p-p的典型输入信号,接近于单ppm误差。甚至,最佳ADC的失调电压通常会多达100 µV。所以,10uV级的失调电压不会对运算放大器自身造成太大的负担;无论如何,系统本身会自动调零。与输入信号的共模电平相关的是ICMRR,即输入偏置电流及其随电源的变化情况。断线表明偏置电流会随电压变化,并且也可能不是线性变化。共有四个ICMRR,因为两个输入端有独立的偏置电流和电平相关性,并且每个输入端随两种电源的变化不同。ICMRR乘以应用电阻的阻值会增加电路的整体失调电压。图4显示了LT1468的偏置电流与VCM(ICMR规格)。添加的线所示的斜率为~8 nA/V,在使用1 kμΩ应用电阻或低ppm误差的情况下将为8 µV/V。它与直线的偏差约为15 nA,由此在1 kμΩ应用环境下会在26 V范围内产生15 µV的误差,或非线性度达0.6 ppm。

图4.LT1468输入偏置电流与VCM

输入级失真

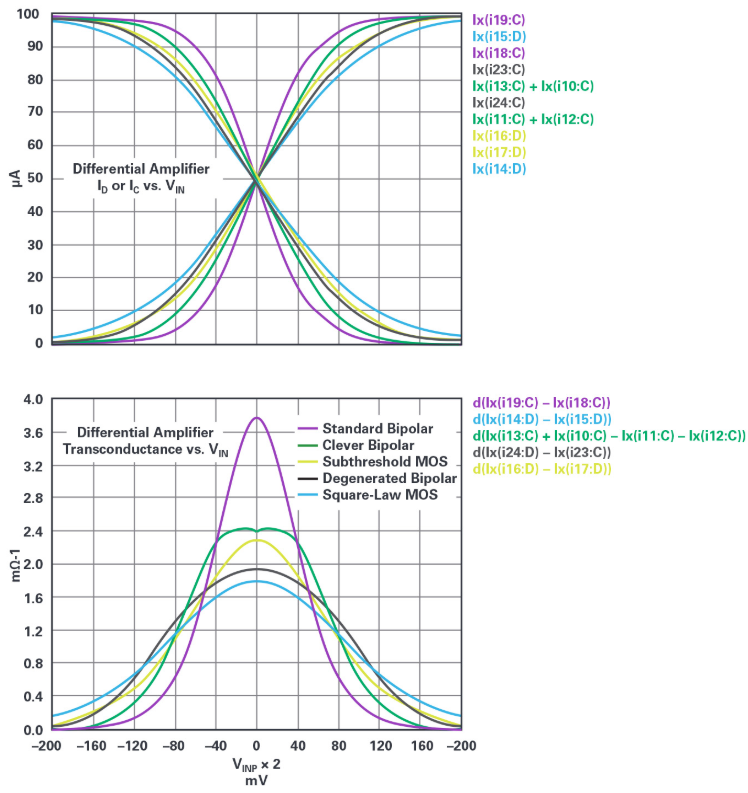

图1显示了输入级,它们通常是由一对差分晶体管设计成跨导电路。图5顶部显示了各种差分放大器类型的集电极或漏电流以及差分输入电压。我们模拟一个简单的双极性对、一个跨线性电路(我们称之为“智能双极”)、一个低阈值(即非常大)的MOS差分对、一个带发射极电阻的双极性对(图5中已退化)和一个超越阈下区域而进入平方律机制运行的小型MOS对。使用100 μA的尾电流模拟所有差分放大器。

在显示图5底部所示的跨导与VIN之前,明确的信息不多。跨导(gm)是输出电流相对于输入电压的导数,使用LTspice®模拟器生成。语法当中包含d(),其在数学上等同于d()/d(VINP)。gmis的非平面度即运算放大器在频率下的基本失真机制。

对于直流,运算放大器的开环电压增益约为gm(R1||R2),但前提是输出缓冲区增益大约1。R1和R2表示信号路径中各种晶体管的输出阻抗,每个电阻均连接到一个供电轨或其他单元。这就是运算放大器中增益受限的基础。R1和R2不能保证为线性;它们可能导致空载失真或非线性度。除线性度之外,我们需要增益达到或超过一百万,才能实现ppm级的增益精度。

观察标准双极性晶体管曲线,我们可以看到它在该组中的跨导最高,但该跨导会随着输入从零伏开始变化而快速消退。这一点让人担忧,因为线性度的基本要求就是增益或gm恒定。另一方面,谁会在乎放大器的电压增益如此之高,以致于差分输入随输出电压的伏特级增加只能实现微伏级增加?下面是CCOMP。

图5.各种差分放大器的输出电流和跨导以及输入电压

CCOMP(CCOMPP和CCOMPM的平行线)会吸收gm在频率范围内的大多数输出电流。它可设定放大器的增益带宽乘积(GBW)。GBW可设定:在频率f下,放大器的开环增益为GBW/f。如果该放大器在f = GBW/10时的输出为1 V p-p,闭环增益为10,那么输入之间将有100 mV p-p。也就是,平衡±50 mV。请注意,图5中显示的标准双极性曲线在±50 mV时损耗了约一半的增益,从而保证了大规模失真。不过,智能双极仅损耗了13%的增益,阈下MOS损耗了26%,退化双极损耗了12%,平方律MOS损耗了15%。

图6显示了输入级的失真与振幅。在应用电路输出时将显示这些信息(乘以噪声增益)。输出失真可以继续增加,但不能减少。

图6.输入级的总谐波失真与差分输入电压

除智能双极的输入级之外,输入级的差分放大器显示失真与输入的平方成正比。在增益一致的应用中,输出失真与输入失真的影响相同。这是大多数运算放大器的主要失真来源。

请考虑一个采用双极输入的增益一致的缓冲区。若输出VOUT峰峰值电压,输入差分信号将为

我们估算

和

其中,GNOISE为应用的噪声增益。

1 ppm非线性度相当于–120 dBc谐波失真,比例为0.0001%。假定一个放大器使用双极性输入级,GBW为15 MHz,作为缓冲区的输出为5 V p-p,通过方程式2可得知该线性度的最大频率仅为548 Hz。上述的假设前提是放大器在较低频率下的线性度最低。当然,当放大器提供增益时,噪声增益增加,且–120 dBc的频率会下降。

阈下MOS输入级支持的–120 dBc频率最高为866 Hz,平方律MOS最高支持1342 Hz,退化双极最高支持1500 Hz。智能双极的失真不符合预测模式,人们必须根据数据手册进行估算。

我们可以使用更简单的公式

其中,K可从运算放大器数据手册的失真曲线中找到。

附加一点,许多运算放大器都是使用轨到轨输入级。大多数放大器通过两个独立的输入级都能实现此功能,即在输入共模范围内,不同输入级之间可以转换。这种转换会导致失调电压变化,还可能导致偏置电流、噪声乃至带宽变化。此外,基本上还会导致输出时出现开关瞬变现象。如果信号总是穿过交越区,那么则不能对低失真应用使用这些放大器。不过,对于相反的应用场合可以使用它们。

我们还没有讨论压摆增强型放大器。这些设计在差分输入较大的情况下不会耗尽电流。遗憾的是,差分输入较小的场合仍会导致gm出现与所讨论的输入幅度类似的变化,并且低失真仍需要有较大的频率环路增益。

由于我们要寻找的是ppm级的失真度,所以我们不会以接近压摆率限值的任何方式运行放大器,所以十分异常的压摆率不是ppm级频率线性度的重要参数,只考虑GBW即可。

前面,我们讨论了单极补偿设计模式的开环增益。并不是所有运算放大器都以该方式提供补偿。通常,开环增益可从数据手册的曲线中找到,而方程式中的GBW/(GNOISE × fSIGNAL)就是频率的开环增益。

增益节点误差

接下来,我们来看图1中的R1和R2。这些电阻连同输入gm提供放大器的开环直流增益:gm × (R1||R2)。原理图中绘制的这些电阻带有可变的非线性删除线。这些电阻的非线性度体现了放大器的空载失真度。而且,R1会从正电源施加影响,以致于直流正电源电压抑制比(PSRR+)约等于gm × R1。同理,R2负责PSRR–。请注意,为什么PSRR的幅度几乎等于开环增益?CCOMPP和CCOMPM向R1和R2注入类似的电源信号;它们在频率范围内设置PSRR+和PSRR–。

增益适度(《《106)的放大器的线性度可能很好,但适度增益会限制增益精度。

电源端口可能会导致失真。如果输出级驱动的负载较大,其中某个电源就会提供负载电流。在一定频率下,远端电源的远程调制能力可能很小,以致于运算放大器的旁路电容成为实际的电源。通过旁路电容后,电源电流下降。下降幅度取决于ESR、ESL和电抗,并且它们会造成电源干扰。由于输出为AB类,所以只有一半的输出电流波形会调制电源,形成平稳的谐波失真。频率范围内的PSRR可降低电源干扰。例如,如果我们观察到电源干扰为50 mV p-p,并希望PSRR抑制电源输入干扰使其在输出端降至低于5 µV p-p,则PSRR在信号频率下需达到80 dB。估算PSRR(f)~Avol(f),GBW为15 MHz的放大器在低于1500 Hz的频率下则会拥有充足的PSRR。

输出级失真

图1中的最后一项是输出级,输出级在本文中被视为缓冲区。图7展示了一个典型的输出级转换函数。

图7.不同负载的输出缓冲区的转换函数

对于不同的负载,我们可看到四种误差。首先是削波:尽管假设该输出级的标称增益为1,但它不完全是轨到轨输出级。这种情况下,甚至空载输出时,每个电源轨也会削波100 mV。随着负载增加(降低负载电阻),输出电压会逐步削减。显然,削波会严重影响失真,而且必须降低输出摆幅才能避免削波。

下一种误差是增益压缩,当转换函数的曲率达到信号极限情况时,我们会看到这种现象。随着负载增加,在电压早期阶段就会出现压缩。同削波一样,在这种机制下,通常无法实现ppm级失真。这种压缩通常是由输出级较小而难以满足输出需要的电流所致。最好的解决方案是,使放大器提供的线性、无压缩最大输出电流仅约为输出短路电流的35%。

另一种显著的失真来源在于交越区约为VIN = 0。空载时,交越扭结可能不那么明显。但随着负载增加,我们可看到绿色曲线的扭结增加。估算交越失真通常需要强大的电源电流。

最后一种失真比较难以理解。由于有些放大器电路输出正电压和电流,还有一些输出负信号,所以无法保证它们具有相同的增益,特别是在带负载时。图7显示了负载时负信号的增益减少情况。

通过环路增益可降低所有这些失真。如果输出级的失真为3%,那么环路增益需要为30,000才能达到–120 dBc电平。当然,这种情况发生在GBW/(30,000 × GNOISE)频率以下,对于15 MHz的放大器通常为1 kHz机制。

有些输出级的失真与频率有关,但也有许多输出级与频率无关。开环增益可抑制输出级失真,但该增益会随频率而下降。如果输出失真不随频率而变化,则增益损耗会产生输出失真,并随频率而线性增加。同时,输入失真会导致总体输出失真随频率而增加。这种情况下,总体闭环输出失真可能主要为输入失真,从而掩盖输出级失真的影响。

另一方面,如果输出级失真确实随频率而线性变化,那么环路增益下降除导致输入失真之外,还会导致另一种输出失真,该失真随频率的平方而变化,并且无法与输入失真区分开来。

低功耗运算放大器包含的输出级通常较少,静态电流低。输出失真可能主要是由这些放大器的输出级导致,而不是输入级。所以,至少需要2 mA电源电流才能获得低失真运算放大器,这种说法一定程度上是正确的。

ppm级精度的规格要求

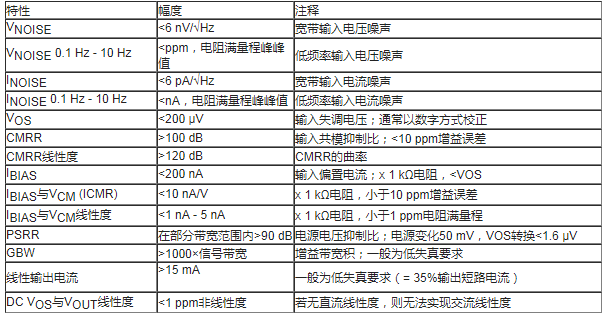

在实际电平转换、衰减/增益和有源滤波器电路中,运算放大器需满足一些基本要求才能支持±5 V信号、适用于1 kΩ环境并实现表1所示的1 ppm线性度。

表1.ppm精度所需的运算放大器误差和幅度列表

现在,我们了解了运算放大器在ppm精度领域的局限性,那么我们该如何改善它们?

噪声:显然,首先要选择一款输入噪声电压不高于应用电阻组合噪声的运算放大器。这样可以降低应用电路的总阻抗,从而降低噪声。当然,随着应用的阻抗下降,通过它们的信号电流会增加,并可能使负载诱发的失真加大。在任何情况下,都不必使运算放大器级别的输出噪声远低于其驱动级别的输入噪声。

电流噪声会乘以应用阻抗,进而形成更多的电压噪声。在电流噪声很低的应用中,MOS输入非常吸引人,但它们的1/f电压噪声通常比双极性输入大。双极性输入的电流噪声为pA/√Hz级别,可能会产生较大的应用噪声,但1/f电流内容生成的应用电压噪声可能大于放大器的1/f电压噪声。一般而言,应用阻抗应小于放大器的VNOISE/INOISE,以避免IBIAS为主的应用噪声。双极性放大器的VNOISE越低,INOISE则越高。

帮助运算放大器实现最佳性能

减少输入误差

除选择CMRR优良的运算放大器之外,设计人员还可以选择用运放搭建反相放大电路而不是同相放大电路。在反相电路中,输入会与地面或一些基准电压源相连,完全不会引发CMRR误差。不过,并不是所有应用电路都能反相,而且通常负电源无法用于负信号偏移。图8显示了非反相电路和反相电路中应用的双极点Sallen-Key滤波器。

图8.非反相(左)和反相(右)Sallen-Key有源滤波器

如果两个输入端均包含应用电阻,则每个输入端的偏置电流乘以相应的电阻产生的电压误差会在输出端抵消,因此也可以抵消ICMR误差。例如,如果设置的放大器增益为10,附带900 Ω反馈和100 Ω接地电阻,则在正输入端安置串联的90 Ω(900Ω||100Ω)电阻即可抵消完全相等的输出偏置电流产生的电压误差。大多数双极性运算放大器的偏置电流搭配都很恰当,使得选择0.1%(而不是常见的1%)电阻即可实现最佳ICMR抑制。在图4中,补偿电阻与反相输入端-input串联放置。它们应能够被旁路通过。因为额外的输入电阻会导致噪声增加(电流噪声乘以连接的等效电阻)。

反相增益让我们能够使用包含轨到轨输入的运算放大器,而不必让信号穿过切换点(假设我们已偏置电源和共模输入电平,以避免切换电压)。

电源注意事项

输出电流将会调节本地的供电电源。电源信号将通过PSRR传输到输入端。被影响的输入会生成输出信号,围绕其环路运行。在1 kHz频率下,1 μF本地旁路电容的阻抗为159 Ω,远低于电源之间线路加上电源本身的阻抗。因此,本地旁路电容实际上在低于100 kHz的频率下没有效果。在1 kHz频率下,调控情况由远程电源控制。在1 kHz频率下,放大器可能达到90 dB电源抑制比。请注意,运算放大器电源端口的大部分电流包含了大量的信号谐波,所以我们希望从输出到供给电源的增益低于30 dB,以实现120 dBc的目标。要实现30 dB的增益,需要电源阻抗《30×负载阻抗。因此,500 Ω负载需要电源的阻抗小于17 Ω。这种情况可行,但是这样就不能在电源与运算放大器之间串联电阻和电感。在10 kHz频率下,要求则更加严格;PSRR将从90 dB降至70 dB,而电源阻抗则必须降至1.7 Ω。可行,但要求严苛。使用大型本地旁路可提供帮助。

图9.负载和电源电流环路

图10.复合放大器与单一放大器失真测试

从布局角度来看,了解输出电流环路的路径非常重要,如图9所示。

图9左侧的图表显示了驱动至负载的正电源电流,然后又通过地面回归负载。在整个接地路径中可能存在压降,以致于偶谐波电源电流的电压从信号源降至输出,从反馈分频器降至输出或输入地。不过,此地非彼地。图9右侧显示了一种传输电源电流的更好方式。电源电流从输入和反馈节点传出。

在高于100 kHz的更高频率下,电源线路的磁辐射可能成为失真来源。电源的偶谐波电流可通过磁性方式耦合到反馈网络的输入,从而使失真随频率大幅增加。在这些频率之下,审慎的布局至关重要。有些放大器采用的是非标准引脚;它们的电源引脚远离输入,有些甚至会在输入侧提供额外的输出端口,以避免磁干扰。

减少负载为主的失真

在高负载环境下,许多运算放大器的输出级都会成为主要的失真来源。您可以通过一些技巧来改善负载失真。其一,使用复合放大器,即一个放大器驱动输出,另一个放大器进行控制,如图10所示。

此电路通过LTspice仿真设计实现。LTC6240和LT1395的spice模型文件中包含失真回放功能的宏模型。大多数宏模型都不会尝试显示失真情况,即使显示,仿真结果也可能不准确。该工具(LTspice)可查看宏模型的文本文件,确实如此,这些宏模型的失真模拟效果非常不错。

图10右侧是LTC6240,提供的增益为2,驱动电阻为100 Ω,对于该放大器而言负载较大。图10左侧是一款复合放大器,输入端另设一个LTC6240,并有一款良好的宽带电流反馈放大器(CFA)作为独立放大器来驱动相同的负载。复合放大器的理念是,输出运算放大器已具备适度的低失真,并且通过输入放大器在频率范围内的环路增益可进一步减少该失真。对于独立放大器和复合放大器,我们的闭环增益都为2,但在复合放大器中,可以对LT1395单独设置其自身的增益(通过Rf1和Rg1设置为4),以降低控制放大器的输出摆幅。由于输入引发的失真随输出振幅的平方增加,由此可进一步减少控制运算放大器的失真。

图11显示了10 kHz、4 V p-p输出的频谱。

谐波失真的计算方式为:每个谐波电平(dB)减去基波电平(在10 kHz频率下)。如图底部所示,输入信号的失真约为–163 dBc,非常好,足以让人相信模拟效果。V(out2)来自于独立的LTC6240,失真为–78 dBc。也不错,但当然没有达到ppm级。

图11.复合放大器和常规放大器的失真频谱

图11顶部显示了复合放大器的失真,–135 dBc,相当出色。这么好的结果,我们能否相信?为了加以验证,中间部分显示了原理图上节点的失真。如果复合放大器输出端的失真接近于零,但输出放大器本身的失真确实有限,那么反馈过程会在其输入端(中间)为输出放大器失真设置负值。中间部分的失真为–92 dBc,这实际上与LT1395数据手册的曲线匹配!我仍会想,如果宏模型中体现出物理LTC6240输入CMRR或ICMR曲率,它们可能还会增加实际的电路失真。

遗憾的是,很少有宏模型包含失真。您必须阅读宏模型.cir文件的标题来查看其是否受支持。要了解失真是否与数据手册的曲线匹配,需要进行一些模拟。

复合放大器的补偿可能有点棘手,但在我们的示例中,第二个放大器的带宽比输入放大器高出10倍以上,只需少许Cf即可提供电路补偿。在此补偿架构中,如果控制放大器的总体增益中包括BW的带宽,那么输出放大器的带宽应》3 × BW,而总体带宽应保守设置为约等于BW/3。

为避免带宽损耗,我们可以使用增强放大器的方法。这样相比复合方案对失真的改善较小,但带宽及建立时间都会毫发无损。图12显示了测试原理图。

图12右侧显示了U2,即我们的独立LTC6240;左侧显示了两个LTC6240放大器。U1同独立放大器类似,控制输出,增益为2;U2的增益为3。U2在增强节点的输出电压大于U1的相应电压,所以U2会向输出端驱动输送电流。RBOOST和U2的增益可以配置,以使U2向Rl驱动输送96%的负载电流,并使U1保持轻载,从而改善失真。我们需要确保U2包含足够的裕量,以承载额外的摆幅。

LTC6240在kΩ范围内的负载失真主要为输入失真,但对于100 Ω负载则主要为输出级失真。

图13显示了频谱结果。

同样,独立放大器在10 kHz频率下的失真为–78 dBc。增强型放大器提供的失真为–106 dBc;不像复合放大器那么好,但比独立放大器几乎高出30 dBc。不过,增强型放大器的带宽只会降低少许。

图12.增强型放大器与独立放大器的模拟设置

请注意,RBOOST微调了一下;如果将其改为52 ± 2 Ω,增强型失真则下降10 dBc,但随后发生的变化则较小,最高为±10 Ω。似乎U1有一些预期极性的适度负载。理想(无负载)或额外的增强电流会导致失真增加。

最好是,U2与U1有相同的群组延迟,以使增强信号与输出同时出现。U2的增益比U1高50%,因而闭环带宽较少,这意味着增强输出会使频率范围内的主要输出延迟。通过跨接在U1输入端的电阻,可将U1的带宽降至与U2相同的水平。这样可使U1的噪声增益等于U2,从而实现相同的群组延迟。该模拟器在10 kHz频率下没有改善;U1提供最佳失真,无延迟均衡。您需要尝试一下,才能了解在更高的频率下是否也是这种情况。如果放大器为电流反馈类型,那么可以通过降低Rf1和Rg1使U2的带宽升至U1的水平。

ppm级质量放大器推荐

表2显示了一些建议的接近ppm线性度的放大器的重要规格。

红色条目旨在提示读者:该参数可能不符合ppm级失真。该组当中最易于使用的更好的产品为AD8597、ADA4807、ADA4898、LT1468、LT1678和LT6018。

有些放大器需要解决其输入问题(同相放大应用可能存在问题),但仍能提供良好的失真:AD797、ADA4075、ADA4610、ADA4805、ADA4899和LTC6228。

图13.增强型放大器和常规放大器的失真频谱

结论

遗憾的是,商用型ppm精度放大器难以找到(如果可以找到)。市场上存在ppm线性放大器,但必须注意这些放大器的输入电流,它们可能会通过电路中的应用阻抗产生失真。这些阻抗可以降低,但在反馈中驱动它们会导致运算放大器输入端产生失真的风险。在特别低的输入电流和变动环境下使用运算放大器,可以通过调整电路中的应用阻抗以使运算放大器获得最佳失真,但这样会增加系统噪声。要达到ppm级线性度和噪声,需要认真挑选运算放大器并优化应用电路。

作者简介

Barry Harvey曾担任模拟IC设计人员,负责设计高速运算放大器、基准电压源、混合信号电路、视频电路、DSL线路驱动器、DAC、采样保持放大器、倍增器等。他拥有斯坦福大学的电气工程硕士学位。他拥有20多项专利,发表过许多文章和论文。Barry喜欢维修用过的测试设备、弹吉他以及研究Arduino相关项目。作者:Barry Harvey ADI公司

-

什么是运算放大器2022-11-08 1959

-

运算放大器的精度局限性是什么2021-03-11 1996

-

运算放大器的误差源2021-02-05 2893

-

如何在运算放大器串联时实现高精度和高输出的功率?2020-11-09 2425

-

如何通过运算放大器实现ppm精度2020-06-05 4269

-

如何通过运算放大器实现ppm精度?2020-05-06 3249

-

帮助运算放大器实现最佳性能的措施分析2020-04-17 2358

-

运算放大器类型总结2019-09-26 4153

-

转向特定应用的运算放大器2018-10-22 2241

-

关于运算放大器的选型2017-06-22 1805

-

运算放大器2014-04-23 5066

-

运算放大器对基本运算的实现2010-04-24 769

-

运算放大器,运算放大器是什么意思2010-03-09 4139

全部0条评论

快来发表一下你的评论吧 !