实现汉明纠错码的编码和解码方案设计

编码与解码

描述

本实验的目的是实现汉明纠错码的编码和解码

1.1汉明码简介

汉明码,是在电信领域的一种线性调试码,以发明者理查德 卫斯理 汉明的名字命名。汉明码在传输的消息流中插入验证码,当计算机存储或移动数据时,可能会产生数据位错误,以侦测并更正单一比特错误。由于汉明编码简单,他们被广泛应用于内存。

与其他的错误校验码类似,汉明码也利用了奇偶校验位的概念,通过在数据位后面增加一些比特,可以验证数据的有效性。利用一个以上的校验位,汉明码不仅可以检验数据是否有效,还能在数据出错的情况下指明错误的位置。(汉明码可以检测两位错误,纠正一位错误)。

1.2编码规则

理解汉明码首先要理解奇偶校验,奇校验就是在一串编码里增加一位校验位使这一串编码里的1的个数位奇数。偶校验同理,使编码里1的个数为偶数。

汉明码的编码位数n与纠错码的位数k的关系:2^k >= n+k+1。这里给出常用的n和k的值:

我们将纠错码加入到相应的编码里,纠错码的位置必须在2^n位置上。以10101100为例进行编码。这个序列为8位,需要4个纠错码。我们先将序列从1到8编号

然后将纠错码(p1,p2,p3,p4)加到这个序列里 的2^n的位置,并用二进制重新编号

然后我们要求出p1,p2,p3,p4的值,先将上面的序列分组编号为xxx1的分为一组,xx1x 的分为一组,x1xx的分为一组,1xxx的分为一组:

xxx1:p1,1,0,0,1,0

xx1x:p2,1,1,0,1,0

x1xx:p3,0,1,0,0

1xxx:p4,1,1,0,0

我们采用偶校验,所以p1 = 1,p2 = 1, p3 = 1, p4 = 0。这样我们就得到了10101100的汉明码111101001100。

那么汉明码是如何来纠错的呢?

我们将p4,p3,p2,p1按这个顺序排列得到0111,这个就是出错的位数,由于是二进制传输,所以就将相应位取反就可以得到正确的序列了。

1.3FPGA实现

对于p1,p2,p3,p4的计算在用fpga实现时只需进行按位异或就行。输入数据位8位,需要四个纠错位。

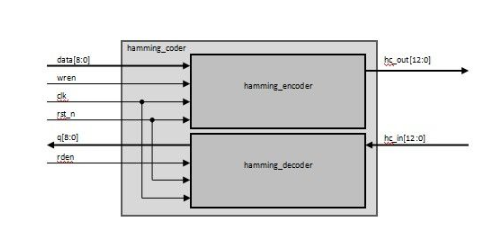

1.3.1 顶层架构

信号说明

顶层代码

1.3.2 编码模块

编码模块只需将分组之后的每一组数据(不包括p)按位异或后赋值给p就可以

编码模块代码

1.3.3解码模块

解码模块只需判断哪位出错,然后取反,并将纠错位删除即可

解码模块代码

仿真验证

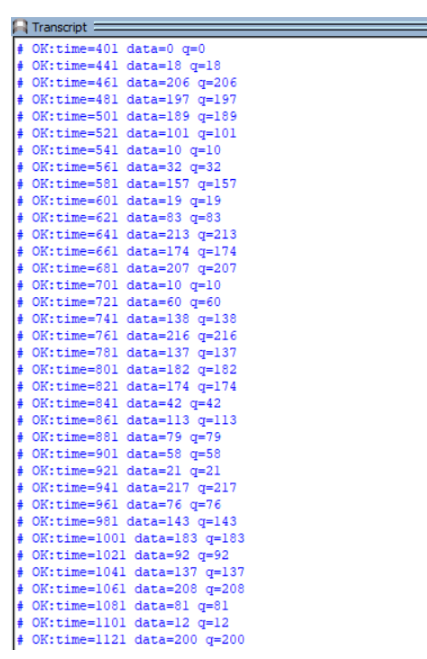

我们用$random系统函数产生的随机数来作为编码模块数据,用$random系统函数产生的随机数来将hc_out的哪一位取反来模拟噪声。并判断输入的数据和输出的数据是否相等,以验证纠错功能。用$display和$error系统函数来生成报告。

测试文件代码

生成的报告,我们可以看到错误的数据可以被修改成原来正确的数据,证明我们的编码解码模块功能正确

-

【原创】基于FPGA的汉明码编码解码设计2020-04-15 3509

-

STM32H7系列内部存储器保护的纠错码(ECC)管理2023-09-08 650

-

汉明纠错编码器实例(VHDL源代码)2009-05-27 767

-

认证系统与纠错码的应用研2009-08-13 819

-

符合中国数字电视地面广播标准的前向纠错码编码器设计2009-12-13 504

-

新的非对称量子纠错码的构造2010-02-10 907

-

RS纠错码在图文电视数据广播中的应用2011-07-21 1147

-

纠错码性能仿真中的误码率估计2011-11-10 1197

-

纠错码与通信系统的保密2016-07-29 836

-

适用于SRAM_PUF的纠错码研究2017-01-08 1049

-

基于纠错码的灰度位信息隐藏算法2018-01-07 888

-

线性纠错码的基石——奇偶校验2018-07-13 6779

-

STM32H7系列内部存储器保护的纠错码(ECC)管理2023-08-01 1079

-

是什么导致RAM中的内存数据损坏?纠错码(ECC)如何修复位翻转?2023-12-15 4659

全部0条评论

快来发表一下你的评论吧 !